1.引言

隨著集成電路制造技術(shù)的發(fā)展,VLSI 已經(jīng)進(jìn)入了SoC(System-on-Chip )片上系統(tǒng)時(shí)代。對(duì)于復(fù)雜的片上系統(tǒng)而言,系統(tǒng)驗(yàn)證占整個(gè)設(shè)計(jì)時(shí)間的60%-70%,其中涉及到軟件與硬件的協(xié)同工作等等。傳統(tǒng)的系統(tǒng)驗(yàn)證在RTL 級(jí)進(jìn)行,RTL 提供更精確接近實(shí)現(xiàn)的同時(shí),也加長(zhǎng)了驗(yàn)證時(shí)間以及此時(shí)發(fā)現(xiàn)問題再修改帶來的成本增加,所以非常有必要地在盡可能早地進(jìn)行有效的系統(tǒng)驗(yàn)證。

SystemC 作為一種系統(tǒng)描述語(yǔ)言應(yīng)運(yùn)而生,它支持從系統(tǒng)級(jí)到門級(jí)的描述,解決了傳統(tǒng)片上系統(tǒng)設(shè)計(jì)方法中不同級(jí)別使用不同描述語(yǔ)言帶來的過渡問題,而其事務(wù)級(jí)(TransacTIon-Level,TL)建模仿真方法可以在早期有效地進(jìn)行系統(tǒng)驗(yàn)證,同時(shí)速度較RTL 級(jí)仿真更快。

目前,事務(wù)級(jí)建模得到廣泛的使用和認(rèn)同,Synopsys 公司現(xiàn)已提供關(guān)于AMBA 架構(gòu)的事務(wù)級(jí)模型,以供進(jìn)行由AMBA 架構(gòu)組成的SoC 系統(tǒng)的事務(wù)級(jí)建模仿真所用。

2.SystemC 事務(wù)級(jí)建模

SystemC 由C++衍生而來,在C++基礎(chǔ)上添加硬件擴(kuò)展庫(kù)和仿真庫(kù)構(gòu)成,從而使SystemC 可以建模不同抽象級(jí)別的包括軟件和硬件的復(fù)雜電子系統(tǒng),既可以描述純功能模型和系統(tǒng)體系結(jié)構(gòu),也可以描述軟硬件的具體實(shí)現(xiàn)。

在使用SystemC 進(jìn)行高層次建模時(shí),引出一個(gè)新的概念——TLM(Transaction-Level Model )事務(wù)級(jí)模型,該建模方法創(chuàng)建一可執(zhí)行平臺(tái)模型,對(duì)系統(tǒng)進(jìn)行仿真,但其不僅僅是功能級(jí)描述,仿真也具有一定時(shí)序。

事務(wù)級(jí)模型建模因不考慮很多底層細(xì)節(jié),所以進(jìn)行建模時(shí)間短,并且可以將重點(diǎn)放在如何通信,而不是通信在更底層如何實(shí)現(xiàn);事務(wù)級(jí)建模可以使用事件驅(qū)動(dòng),由一事件可以驅(qū)動(dòng)一系列行為,因此建模可以在早期進(jìn)行。所以,SystemC 事務(wù)級(jí)模型具有建模效率高和仿真速度快的優(yōu)點(diǎn)。另外,SystemC 事務(wù)級(jí)建模作為高層次建模方法,還具有如下特點(diǎn):

–模型之間依靠時(shí)鐘和(動(dòng)態(tài))事件同步;

–模型內(nèi)部是周期精確的;

–模塊pin 沒有明確進(jìn)行建模實(shí)現(xiàn),但可通過適配器外部實(shí)現(xiàn);

–模塊之間通過端口(port)和層次化通道(hierarchy channel )進(jìn)行通信。

上述特點(diǎn)描述中,端口(port)和層次化通道(hierarchy channel )概念為SystemC 事務(wù)級(jí)建模引入的新概念:

. 接口(inteRFace):定義一組方法來實(shí)現(xiàn)設(shè)計(jì)目標(biāo),但不實(shí)現(xiàn)這些方法;

. 通道(channel): 實(shí)現(xiàn)接口定義的方法;根據(jù)通道內(nèi)部所實(shí)現(xiàn)方法的情況,又分為基本 通道和層次化通道;基本通道中沒有可見的結(jié)構(gòu),不包括進(jìn)程,也不能直接訪問其他的基本通道;層次化通道則包括模塊、進(jìn)程等,可以直接訪問其他的通道;

. 端口(port):總是與一定的接口類型相關(guān)聯(lián),端口也只能連接到實(shí)現(xiàn)了該類接口的通道上,通過端口模塊和進(jìn)程來訪問通道內(nèi)定義的接口方法; 通過接口又引出接口方法調(diào)用(interface-method-call,IMC) 的概念,是指一個(gè)進(jìn)程通過端口調(diào)用通道內(nèi)實(shí)現(xiàn)的接口方法。方法在接口中定義,在通道內(nèi)實(shí)現(xiàn),但在進(jìn)程內(nèi)執(zhí)行。基于以上概念,提出一種事務(wù)級(jí)建模思想:

①設(shè)備若僅作為被訪問者,如存儲(chǔ)器、FIFO 等,那么只需要定義接口,以備被訪問,實(shí)現(xiàn)接口方法,此設(shè)備作為基本通道存在;

②設(shè)備若僅作為訪問者,如CPU,那么只需要定義端口,來訪問其他設(shè)備;

③設(shè)備若既可作為訪問者和被訪問者,如總線,那么它就需要同時(shí)定義端口和接口,同時(shí)也要實(shí)現(xiàn)接口,這也就是層次化通道,接口用來被訪問,端口用來發(fā)起訪問。

對(duì)于SoC 設(shè)計(jì)而言,事務(wù)級(jí)建模屬于架構(gòu)型設(shè)計(jì)。在架構(gòu)的事務(wù)級(jí)建模中,模塊在共享的通信通道(如總線)彼此進(jìn)行交易。同時(shí)在進(jìn)行系統(tǒng)的SystemC 事務(wù)級(jí)建模中,可以有效地對(duì)軟件部分進(jìn)行描述,結(jié)合其進(jìn)行協(xié)同仿真。所以,對(duì)所設(shè)計(jì)的系統(tǒng)使用事務(wù)級(jí)模型進(jìn)行仿真時(shí),不僅系統(tǒng)架構(gòu)可以找到系統(tǒng)級(jí)的瓶頸并能有效解決,而且軟件開發(fā)者也可以評(píng)估軟件的運(yùn)行吞吐量,同時(shí)也可以研究在系統(tǒng)背景下軟件和硬件模型之間的交互。

3.CoCentric System Studio(CCSS)內(nèi)事務(wù)級(jí)建模仿真

CCSS 是Synopsys 公司提供的一SystemC 仿真平臺(tái),支持使用完全事務(wù)級(jí)模型進(jìn)行設(shè)計(jì)、分析、調(diào)試驗(yàn)證SoC 架構(gòu)。

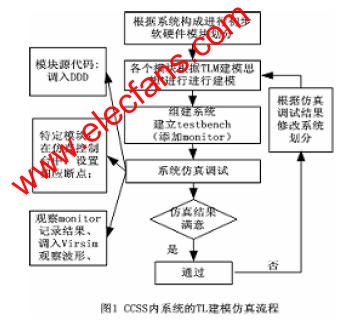

事務(wù)級(jí)仿真中,對(duì)于源代碼的調(diào)試,CCSS 內(nèi)嵌調(diào)試軟件DDD。使用事務(wù)級(jí)模型組建系統(tǒng),在編譯之后的系統(tǒng)仿真中,當(dāng)系統(tǒng)工作運(yùn)行到將要調(diào)試的特定模塊部分,則可以將該模塊部分調(diào)入DDD,進(jìn)行普通設(shè)置斷點(diǎn)的調(diào)試,顯示該模塊的執(zhí)行情況以及對(duì)系統(tǒng)的影響。對(duì)于系統(tǒng)中整體特定模塊而言,可以在實(shí)例上設(shè)置斷點(diǎn)、在連線上設(shè)置數(shù)據(jù)監(jiān)控點(diǎn)(data watch point)、在端口和參數(shù)上設(shè)置層次監(jiān)控點(diǎn)(level watch point)。仿真進(jìn)行時(shí),仿真控制面板上的Level Watch 中,可以改變參數(shù)值,以得出不同參數(shù)值的仿真情況。若觀察波形,則可以調(diào)入Virsim 波形仿真軟件。

此外,對(duì)于整個(gè)系統(tǒng)的事務(wù)級(jí)仿真,更需要一些直接明確的數(shù)據(jù)來對(duì)系統(tǒng)性能進(jìn)行評(píng)估,例如需要知道系統(tǒng)中發(fā)送數(shù)據(jù)的數(shù)目,某一時(shí)刻系統(tǒng)的狀態(tài)、發(fā)生的事件等等。CCSS 提供的監(jiān)控器(monitor )可以解決這一問題。

對(duì)于監(jiān)控系統(tǒng)仿真情況,CCSS 提供了3 種類型的監(jiān)控器,分別為表格、消息以及數(shù)據(jù)類型。程序中設(shè)置此三種監(jiān)控器,對(duì)期望的系統(tǒng)行為進(jìn)行監(jiān)控,調(diào)整系統(tǒng)參數(shù)帶來的性能改變也可以清晰顯示。根據(jù)記錄結(jié)果,觀察系統(tǒng)弱點(diǎn),以此為出發(fā)點(diǎn)進(jìn)行改進(jìn)系統(tǒng)。

圖1 總結(jié)出系統(tǒng)的TLM 建立及仿真流程,TLM 建模思想見部分2 中描述,在整個(gè)系統(tǒng)仿真、修改過程中,驗(yàn)證平臺(tái)(testbench )保持不變從而減少工作量,同時(shí)系統(tǒng)修改前后的性能也有更好的可比性。

4.具體實(shí)例

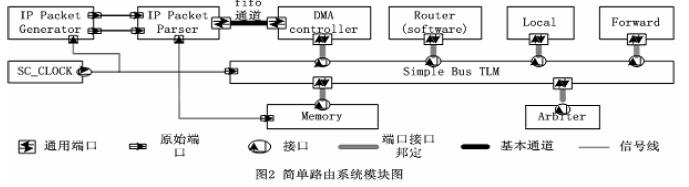

這部分給出一例子,結(jié)合數(shù)據(jù)來說明由TLM 組建的系統(tǒng)在CCSS 中進(jìn)行仿真的方法及特點(diǎn)。如圖2 所示一簡(jiǎn)單IP 路由系統(tǒng)。該系統(tǒng)實(shí)現(xiàn)簡(jiǎn)單路由尋址,分析數(shù)據(jù)屬于本地地址還是其他地址。該系統(tǒng)有四個(gè)主設(shè)備:DMA 控制器、路由分析(Router)、本地輸出(Local)、其他輸出(Forward)模塊,兩個(gè)從設(shè)備:存儲(chǔ)器(Memory)、仲裁(Arbiter)模塊。

遵循部分2 中所敘述思想對(duì)系統(tǒng)中模塊進(jìn)行事務(wù)級(jí)建模。

IP 數(shù)據(jù)包產(chǎn)生(IP Packet Generator )模塊這里為testbench,IP 數(shù)據(jù)包分析(IP Packet Parser)模塊分析接收來的IP 包,然后送入DMA 控制器,DMA 控制器再將數(shù)據(jù)送入存儲(chǔ)器中,路由分析模塊進(jìn)行路由分析,本地輸出模塊為本地地址端口輸出、其他輸出模塊為其他地址端口輸出。

初步系統(tǒng)設(shè)計(jì),對(duì)于Router 模塊,考慮使用軟件或者硬件實(shí)現(xiàn),具體根據(jù)系統(tǒng)性能結(jié)果決定。

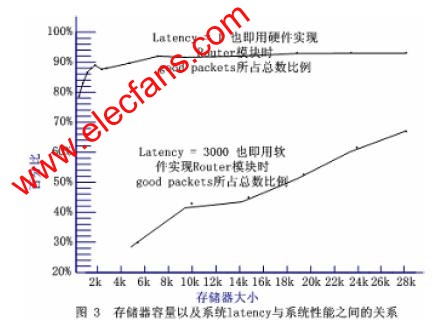

探測(cè)系統(tǒng)性能,在此主要分析IP 包丟失率。鑒于存儲(chǔ)器的大小直接關(guān)系整個(gè)系統(tǒng)的成本,同時(shí)系統(tǒng)的路由延遲(latency )關(guān)系到系統(tǒng)性能。可以同時(shí)考慮該兩項(xiàng)對(duì)IP 包的丟失的影響。對(duì)于使用硬件實(shí)現(xiàn)Router 模塊,路由延遲范圍值在1-40 時(shí)間單位之間;而使用軟件實(shí)現(xiàn)范圍值則在3000-7000 時(shí)間單位之間。

整個(gè)系統(tǒng)中使用三種類型的監(jiān)控器進(jìn)行驗(yàn)證系統(tǒng)行為,在IP Packet Parser 模塊內(nèi)考察IP 包丟失情況,分析存儲(chǔ)器大小和系統(tǒng)延遲帶來的影響。改變存儲(chǔ)器大小和延遲大小,根據(jù)IP Packet Parser 模塊內(nèi)監(jiān)控器記錄得出結(jié)果。如圖3 所示。

結(jié)合圖3,可以看出,當(dāng)存儲(chǔ)器容量一定時(shí),延遲越大,系統(tǒng)性能也就越差,也就是說,這種情況下,系統(tǒng)為了達(dá)到較好的性能,就需要使用硬件實(shí)現(xiàn)Router 模塊。使用軟件實(shí)現(xiàn)Router 模塊雖然可以降低成本,但是帶來的是系統(tǒng)性能的降低;提高存儲(chǔ)器容量可以對(duì)此進(jìn)行補(bǔ)償,但是同時(shí)也增加了一定的成本。所以需要同時(shí)考慮兩方面的因素,進(jìn)行折衷選擇。

另外一方面,在延遲latency = 1 時(shí),即使用硬件實(shí)現(xiàn)路由分析模塊時(shí),系統(tǒng)在存儲(chǔ)器容量大于20K 以后,性能幾乎沒有提高,這時(shí),考慮到到系統(tǒng)瓶頸,重點(diǎn)將不放在延遲及存儲(chǔ)器大小,而轉(zhuǎn)為分析系統(tǒng)架構(gòu)的原因。

5.結(jié)論

SystemC 語(yǔ)言中TLM 具有建模效率高、仿真速度快的特點(diǎn),本文結(jié)合其特點(diǎn)給出了一種建模思想。CoCentric System Studio(CCSS )支持完全的TLM 仿真,并且支持各種調(diào)試,可以明確分析系統(tǒng)性能,給出仿真流程。結(jié)合例子來說明在CCSS 內(nèi)進(jìn)行TL 建模組建系統(tǒng)并仿真,可以得出對(duì)系統(tǒng)改進(jìn)的指導(dǎo)結(jié)果。