IMS Research的調(diào)查顯示,帶有視頻功能的汽車音響主機的數(shù)量將會由2006年的850萬臺增長到2015年的2660萬臺。為了既能向駕駛員提供信息,又不分散其注意力,顯示器需要安裝在遠離汽車音響主機的位置,并將畫面投影到擋風(fēng)玻璃的背面。這種結(jié)合了圖像源和面板的視頻接口正在越來越多地從模擬視頻技術(shù)轉(zhuǎn)向質(zhì)量更高的RGB(紅綠藍)數(shù)字視頻格式,后者已成為LCD顯示器中使用的標(biāo)準(zhǔn)接口。前端顯示應(yīng)用的電纜長度通常保持在1到3米的范圍內(nèi),而后座娛樂(RSE)單元的電纜則需要達到8米甚至更長。這種連接支持千兆位/秒的數(shù)據(jù)傳輸速率,遠超過傳統(tǒng)車載網(wǎng)絡(luò)的波特率,并可以利用點對點串行器/解串器(SerDes)解決方案完美實現(xiàn)。與傳輸一路較寬的并行視頻總線相比,這種芯片組大大降低了傳輸線和連接器的引腳數(shù)量,從而實現(xiàn)了出眾的系統(tǒng)級優(yōu)勢。

為滿足汽車顯示器接口方面的嚴(yán)苛要求,比如高數(shù)據(jù)吞吐量、超薄布線、高級信號調(diào)節(jié)、可檢測性以及超低EMI(電磁干擾)等。美國國家半導(dǎo)體(NS)公司開發(fā)出DS90UR905/6 和DS90UR907/8 SerDes芯片組,該產(chǎn)品是能將分辨率從QVGA(400 x 240)擴展到24位色深的XGA(1024 x 768)的嵌入式時鐘SerDes解決方案。寬范圍的像素時鐘頻率使汽車制造商只需在其整個車型系列中采用一個數(shù)字視頻顯示接口方案,即可覆蓋從雙畫面的小儀表盤面板、中控臺的LCD到更大尺寸的RSE顯示器應(yīng)用。

視頻應(yīng)用和SerDes概念

SerDes組件的目標(biāo)應(yīng)用領(lǐng)域是平板顯示器鏈路接口,它可以通過一根較長的串行電纜把圖像主機與顯示器連接起來。典型的例子包括:中央信息顯示器(CID)、儀表盤、頭枕上的娛樂顯示器或為后座乘客準(zhǔn)備的車頂下降式顯示模塊,如圖1所示。這些新型芯片組是NS推出的"FPD-Link II"系列產(chǎn)品中的一組,它們可以將一個視頻源的27位數(shù)字RGB色彩信息和時間控制信號轉(zhuǎn)換成一個嵌入了時鐘信息的單一串行數(shù)據(jù)流在雙絞線上傳輸。芯片組在I/O(輸入/輸出)層采用高速的差分信號,也就是說,在"真"(正)端子上傳輸實際信號的同時,"互補"(負)端子上傳輸與之對應(yīng)的相反極性信號。

圖2在系統(tǒng)層面上描述了視頻傳輸?shù)母拍睢3祟伾蜁r序位外,還有一個可選的I2C控制接口,它可替代通過常規(guī)引腳帶選項實現(xiàn)的組件配置。芯片組支持18bpp(每像素位)或24bpp的色深。彩色顯示器使用3個子像素(紅、綠、藍)來定義一個單獨的像素。由于每個像素有18位(6位紅,6位綠和6位藍),我們可以得到26.2萬種顏色。大多數(shù)人的眼睛可以看到1000萬種以上的顏色,這也就解釋了為什么使用24bpp已成為趨勢:它能提供超過1600萬種顏色,可實現(xiàn)更豐富的用戶體驗和平滑的顏色梯度。像素時鐘范圍現(xiàn)已極寬:頻率可從5MHz 到65MHz,這使得串行鏈路速率從140Mbps提高到1.82Gbps,涵蓋了汽車顯示器的全部主流分辨率。

并行LVCMOS輸入和輸出信號可以分別靈活地對準(zhǔn)同步發(fā)射器輸入及接收器恢復(fù)輸出時鐘(PCLK)的上升沿或下降沿,這一特性大大簡化了串行器至圖像控制器以及解串器至LCD計時控制器的接口連接。在發(fā)射器并行時鐘周圍的一定頻段內(nèi),SerDes芯片組在"預(yù)同步"接收器的PLL時無需外部參考時鐘(石英或振蕩器)。甚至在一切可能的隨機數(shù)據(jù)模式傳輸過程中該同步都能得到保證,這被稱為"隨機數(shù)據(jù)鎖定"特性。這不僅節(jié)省了參考組件系統(tǒng)的成本,而且消除了另一個潛在的電磁干擾源。該性能還可以實現(xiàn)"熱插拔",即在不需要任何特殊排序或訓(xùn)練模式的情況下,就可以對送往解串器的串行數(shù)據(jù)流執(zhí)行斷言/取消斷言操作。

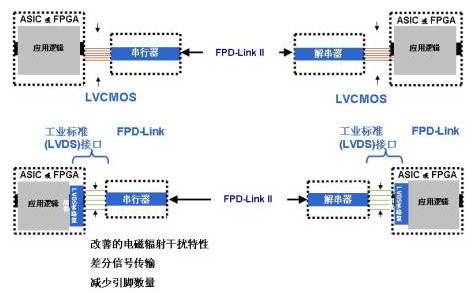

一旦接收器PLL鎖定在發(fā)射器的頻率下,即可由LOCK輸出標(biāo)志引腳顯示這一狀態(tài),確保接收器輸出的數(shù)據(jù)完整性。DS90UR907/8芯片組具有DS90UR905/6芯片組的一切特性,兩耳區(qū)別在于輸入輸出不再是發(fā)送LVCMOS信號的并行總線,而是遵照開放的工業(yè)標(biāo)準(zhǔn)"FPD-Link"。很多現(xiàn)代化的圖像控制器、顯示定時控制器、ASIC和FPGA都支持這種"一級串行化"技術(shù),它采用適合18bpp的3個數(shù)據(jù)通道,或者適合24bpp的4個數(shù)據(jù)通道,每一個都有一路并行時鐘通道。電信號的發(fā)送遵循開放的ANSI/TIA/EIA-644A標(biāo)準(zhǔn),該標(biāo)準(zhǔn)又稱作"LVDS"(低壓差分信號傳輸)。使用該接口技術(shù)代替常規(guī)LVCMOS的優(yōu)勢在于:采用差分信號可降低電磁干擾,并減少組件的引腳數(shù)量,如圖3所示。

圖3 FPD-Link系統(tǒng)接口選項的優(yōu)勢

FPD-Link II有效負載

在每一個像素時鐘周期內(nèi),28個"次符號"在差分I/O上經(jīng)過時分多路復(fù)用,轉(zhuǎn)換成一個串行數(shù)據(jù)流。嵌入的有效負載包含24個顏色位、3個定時信號(水平同步-HS、垂直同步-VS和數(shù)據(jù)使能-DE)以及附加位。互連線路速率為28x像素時鐘。在65MHz下,該速率轉(zhuǎn)化為1.82Gbps。串行數(shù)據(jù)流由前端的"CLK1"HIGH 位和末尾的"CLK0"LOW位限定,由此可在每一個幀之間實現(xiàn)高低電平的平穩(wěn)過渡,令串行器的PLL可以參照其進行同步并提取嵌入的時鐘信息。兩個附加位("DCA"和"DCB"位)位于每一個幀中間,它們包括嵌入在DCA 和 DCB位過渡過程的定時信號。有效負載位為了降低諧波電磁干擾和改善信號質(zhì)量,經(jīng)過了隨機化、平衡和加擾處理,同時為交流耦合建立了直流平衡。

由于電纜連接越長,發(fā)射器和接收器模塊之間越有可能出現(xiàn)接地電位漂移,交流耦合接口方案則可通過在傳輸線中采用串聯(lián)電容實現(xiàn)電勢解耦。串行器中的直流平衡編碼器和相應(yīng)的解串器中的直流平衡解碼器可在串行鏈路上實現(xiàn)高低位之間的均勻分布,以防止ISI(符號間干擾)效應(yīng)和由電容引起的靜態(tài)模式的阻塞。通過在兩端配置電容,該方案也可以在電纜損壞或者對地或板上凈電壓出現(xiàn)短路時提供輸入/輸出短路保護。隨機化和不規(guī)則性不僅能保證良好的眼圖開度,同時還能最小化互聯(lián)線路的電磁干擾,總體來說其編碼效率高于85%。

增強的信號調(diào)理能力

信號調(diào)理技術(shù)在推動長距離高速連接方面發(fā)揮了至關(guān)重要的作用,在串行器端采用了信號還原特性,圖4是一個信號還原操作的例子。這一串轉(zhuǎn)換的比特流,依次為0、1、000和1,圖形頂部給出了單端(SE)波形,可以在真值和輸出端子處相對于地電位進行測量。圖形底部給出了差分(DIFF)信號,相當(dāng)于在其端子范圍內(nèi)接收器輸入端的差分電壓擺幅。對于第一次轉(zhuǎn)換,發(fā)送的第一個信號是0,形成全差分擺幅。下一次轉(zhuǎn)換是一個1,同樣是全電壓擺幅。接下來在C、D和E時間幀中是一系列0,其中第一個0是全電壓擺幅。隨著之后時隙D和E中第二個和第三個0的到來,幅值將會下降,表示被信號"還原"了。因此電纜中的靜電荷將受到限制,否則它將會隨著時間增強。這使得在時隙F發(fā)送的末位1又形成全差分擺幅。信號還原特性通常是在傳輸線路中平衡高低頻信號的內(nèi)能。總體效果就是清晰的信號眼圖張開,在由1或0組成的長序列之后是以一個單獨的比特位轉(zhuǎn)換。信號還原層是可編程的,以便為特定電纜媒介調(diào)整至最佳補償水平。

此外,信號還原特性在可調(diào)差分輸出電壓(Vod)方面有不錯的效果,即它可以使長電纜傳輸?shù)牟罘州敵鲭妷?Vod)加倍。信號還原不需要大幅降低接收器輸入的信號幅度就能做到信號恢復(fù)。解串器的輸入端集成了一個電纜均衡器,在再生全部信號波形時,此功能相對輸入信號而言等同一個高通濾波器,可以部分消除由傳輸媒介引起的低通濾波器效應(yīng)。均衡器在1.5dB到12dB的增益之間具有可編程性。當(dāng)然,所有增強的信號處理特性也可以協(xié)調(diào)使用,為長電纜傳輸中的無差錯數(shù)據(jù)恢復(fù)建立足夠的眼圖開度。

擴頻時鐘

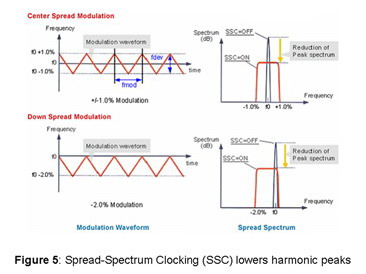

解串器通過一塊集成可配置的擴頻時鐘(SSC)生成器得到增強。在接收器輸出總線端,這會導(dǎo)致輸出時鐘頻率和數(shù)據(jù)頻譜隨著時間推移而以幾十KHz的低調(diào)制率產(chǎn)生輕微變化。如圖5所示,頻率變化可以發(fā)生在名義像素時鐘中心頻率附近("中心擴頻調(diào)制"),或朝向更低的頻率("向下擴頻調(diào)制")。頻譜擴展百分比可高達±2%。擴頻時鐘將峰值能量分散在更寬的頻譜范圍內(nèi),從而大大降低了電磁干擾噪聲水平,而不是在同一時間點上、以恒定頻率來轉(zhuǎn)換所有輸出,此時的輻射噪聲集中在一個窄頻段內(nèi),所有輸出數(shù)據(jù)都與輸出時鐘同步,這使得數(shù)據(jù)和時鐘得到有效擴展。特別是DS90UR906接收器輸出具有低壓(LV)CMOS接口選項,可以大大降低電磁輻射。

增強的診斷能力

另一個特性是內(nèi)建自測試(BIST)功能。在這種模式下,發(fā)射器發(fā)送偽隨機碼序(PRBS)。接收器內(nèi)部產(chǎn)生同樣的序列,并與接收的位模式進行比較。為了在整體測試時間和需要驗證的最低比特誤碼率之間找到最佳折衷方案,用戶可以控制BIST的持續(xù)時間。在遇到有誤碼的有效負載時,PASS引腳會以時鐘方式進行切換。PASS引腳存放BERT(誤碼率測試)的最終結(jié)果。如果測試失敗,說明出現(xiàn)了一個或多個負載錯誤;如果測試通過,說明PRBS序列的傳播和接收均無差錯。在鏈路遠端,BIST無需任何數(shù)據(jù)發(fā)生器、數(shù)據(jù)記錄或測量系統(tǒng)。汽車生產(chǎn)商可使用BIST模式來測試系統(tǒng)和檢查鏈路運行。它還可以用作系統(tǒng)開發(fā)階段的試驗臺,在沒有視頻源的情況下向整個鏈路發(fā)送數(shù)據(jù),同時僅在發(fā)射器上施加時鐘信號。在服務(wù)或故障排除階段,可利用系統(tǒng)測試來驗證鏈路正常工作,以此在主機或顯示端上鎖定問題范圍。最終當(dāng)汽車啟動后,顯示接口可進行例行檢查并驗證連接性。

更多增強功能

更多增強功能包括集成的終端電阻,它降低了電路板設(shè)計的復(fù)雜性,使成本更低,板極空間更小。解串器的輸入端提供了一個終端共模濾波器引腳。建議用戶將共模引腳通過電容接地以確保穩(wěn)定,并保證頻率濾除共模電壓。這將減少對外界的電磁輻射水平,同時可以提高對外界噪聲源的抵抗能力。通常通過大電流注入(BCI)測試對數(shù)字視頻鏈路對外部干擾的抵抗能力進行研究,利用電感將高達300mA的側(cè)電流調(diào)制到電纜屏蔽罩上。I/O 庫通過VDDIO供電,1.8V或3.3V均可。這樣的靈活性可以利用低接口電平的優(yōu)勢,并提供與下游器件的兼容性。

一般來說,當(dāng)在1.8V電壓下操作組件時,電磁干擾水平也隨之降低。斷電情況下,解串器的輸出電壓狀態(tài)可以設(shè)置為三態(tài)(高阻)或低阻。像素時鐘(PCLK)狀態(tài)也可設(shè)置為三態(tài)或低阻,以選擇停止內(nèi)部振蕩器。在后者的情況下,無論是否有輸入信號,時鐘輸出會一直存在。當(dāng)接口僅與短距離的輕負載總線連接時,接收器驅(qū)動強度(RDS)特性可以最小化輸出總線的電流消耗,減慢輸出邊緣轉(zhuǎn)換率并最終降低電磁干擾。芯片組支持-40℃ 到 +105℃的超寬溫度范圍,可適用于不同工作環(huán)境下的各種汽車電子系統(tǒng)。這些芯片組采用LLP封裝,占用的空間很小,并通過了RoHS認證和AEC-Q100 Grade 2標(biāo)準(zhǔn)的全面汽車應(yīng)用認證。

本文小結(jié)

新型DS90UR905/6 和DS90UR907/8 FPD-Link II型芯片組具有許多系統(tǒng)優(yōu)勢和增強特性。并行視頻總線通過一個嵌入式時鐘串行化到一個單組中,這降低了系統(tǒng)成本,消除了時鐘/數(shù)據(jù)偏斜問題,減少了噪聲,并將鏈路延伸至遠途電纜距離。芯片組支持從QWVGA到24位色深XGA的所有普通汽車LCD分辨率。為了促進系統(tǒng)設(shè)計、合格審定和批準(zhǔn),設(shè)計人員能將更多注意力集中到如何降低EMI的特性上。這樣可以在不犧牲可靠性的情況下盡可能降低防護要求的成本。診斷BIST模式有利于工廠測試和實際應(yīng)用,對故障排除的測試和診斷也有益處。作為FPD-Link II系列產(chǎn)品中的第三代芯片組,其組件基于已驗證和可信賴的IP協(xié)議,并且與前幾代芯片組后向兼容。FPD-Link II芯片組系列代表了針對汽車行業(yè)進行優(yōu)化并支持真正即插即用的方案,因為它與低密度線路結(jié)合使用時不影響性能,且?guī)捀摺⒐牡汀⒌虴MI、耐用并可實現(xiàn)自主鏈路同步。