摘要:設(shè)計(jì)了基于FPGA的誘發(fā)電位儀完整系統(tǒng),。首先給出了整個(gè)誘發(fā)電位儀的總體設(shè)計(jì),,討論了FPGA作為主芯片的各模塊集成設(shè)計(jì),在此基礎(chǔ)上論述了ADSl258模/教轉(zhuǎn)換芯片的特點(diǎn)并給出了其與FPGA的接口電路設(shè)計(jì),。該誘發(fā)電位儀系統(tǒng)設(shè)計(jì)具有可靠性高,,通用性和擴(kuò)展性好等優(yōu)點(diǎn),并且具有非常重要的應(yīng)用價(jià)值和良好的市場前景,。

0引言

誘發(fā)電位是指對(duì)神經(jīng)系統(tǒng)某一特定部位給予特定刺激后在大腦皮層所產(chǎn)生的特定電活動(dòng),,對(duì)于神經(jīng)系統(tǒng)功能性異常的疾病有獨(dú)特的檢測診斷能力,也是大腦認(rèn)知和腦機(jī)接口研究常用的技術(shù)手段,。誘發(fā)電位儀通常包括視覺誘發(fā)電位,、聽覺誘發(fā)電位和體感誘發(fā)電位三種檢測功能,其硬件系統(tǒng)核心組成部分包括:刺激信號(hào)源,、腦電信號(hào)放大和數(shù)據(jù)采集,。刺激信號(hào)源包括視覺刺激信號(hào)(如棋盤格、黑白閃光等),、聽覺刺激信號(hào)和神經(jīng)刺激信號(hào),,一般采用分離設(shè)計(jì)。

腦電信號(hào)數(shù)據(jù)采集一般包括模/數(shù)轉(zhuǎn)換、數(shù)據(jù)預(yù)處理和數(shù)據(jù)傳輸?shù)炔糠?,而?數(shù)轉(zhuǎn)換芯片和主控微處理器芯片的選擇主導(dǎo)了整個(gè)數(shù)據(jù)采集系統(tǒng)的性能。在目前的采集系統(tǒng)中,,基于單片機(jī)的中低端控制芯片功能較弱,,逐漸被DSP和ARM或增強(qiáng)型單片機(jī)所取代。DSP芯片采用哈佛結(jié)構(gòu)的流水線工作方式,,能實(shí)現(xiàn)復(fù)雜信號(hào)處理算法,,如文獻(xiàn)采用DSP實(shí)現(xiàn)復(fù)雜的腦電信號(hào)采集系統(tǒng);而ARM適合做事務(wù)處理或者中低端應(yīng)用,如文獻(xiàn)中通過ARM處理器建立操作系統(tǒng)實(shí)現(xiàn)任務(wù)調(diào)度,。盡管采用DSP和ARM芯片可使系統(tǒng)的運(yùn)算能力和管理事務(wù)的能力得到很大增強(qiáng),,但是構(gòu)成完整的數(shù)據(jù)采集系統(tǒng)通常還需要外部邏輯控制器件,尤其不能將數(shù)據(jù)采集和刺激信號(hào)源在單片上集成實(shí)現(xiàn),。

由于現(xiàn)代電子技術(shù)的飛速發(fā)展,,可編程邏輯芯片F(xiàn)PGA的集成度越來越高,受到很多廠家和研究機(jī)構(gòu)的關(guān)注,,利用它的可編程性和可擴(kuò)展,,可將絕大部分的功能集成到FPGA芯片中。如文獻(xiàn)采用FPGA實(shí)現(xiàn)了腦電信號(hào)采集;文獻(xiàn)則將盲分離算法ICA在FPGA上實(shí)現(xiàn),,能同時(shí)對(duì)腦電信號(hào)進(jìn)行采集和獨(dú)立分量分解,。

本文針對(duì)誘發(fā)電位儀的硬件系統(tǒng)設(shè)計(jì),提出將信號(hào)采集控制,、處理,、傳輸、刺激信號(hào)產(chǎn)生等功能集成在一塊FPGA芯片上的設(shè)計(jì)方案,,并結(jié)合ADSl258模/數(shù)轉(zhuǎn)換芯片,,使得系統(tǒng)具有16通道,每個(gè)通道24位采樣精度和400 kHz采樣率的高性能,,而且電路結(jié)構(gòu)簡單,。

1 系統(tǒng)總體設(shè)計(jì)

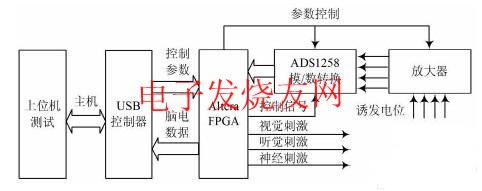

本文提出的誘發(fā)電位儀包括了刺激信號(hào)源、數(shù)據(jù)采集和數(shù)據(jù)傳輸三大部分,。其中核心控制芯片采用Altera公司的FPGA,,產(chǎn)生刺激誘發(fā)信號(hào)源包括聽覺刺激、神經(jīng)傳導(dǎo)刺激和視覺誘發(fā)刺激,,以及實(shí)現(xiàn)對(duì)外圍電路如A/D,,USB等模塊的控制并在芯片內(nèi)部集成濾波算法模塊;數(shù)據(jù)采集采用高精度多通道的模/數(shù)轉(zhuǎn)換芯片ADSl258將通過放大器放大后的誘發(fā)電位信號(hào)進(jìn)行模/數(shù)轉(zhuǎn)換并輸入FPGA內(nèi)進(jìn)行前置處理;數(shù)據(jù)傳輸通

過USB控制器Cypress 68013A將誘發(fā)電位數(shù)據(jù)傳輸至PC上位機(jī),由上位機(jī)應(yīng)用程序?qū)崿F(xiàn)誘發(fā)腦電信號(hào)的后期處理,、顯示,、存儲(chǔ)等功能。系統(tǒng)總體框圖見圖1。

圖1 系統(tǒng)總體框圖

2 FPGA軟件模塊設(shè)計(jì)

2.1 FPGA的優(yōu)勢

FPGA即現(xiàn)場可編程門陣列,,是在CPLD的基礎(chǔ)上發(fā)展起來的新型高性能可編程邏輯器件,,它既繼承了ASIC的大規(guī)模、高集成度,、高可靠性的優(yōu)點(diǎn),,又克服了普通ASIC設(shè)計(jì)周期長、投資大,、靈活性差的缺點(diǎn),,逐步成為復(fù)雜數(shù)字硬件電路設(shè)計(jì)的理想選擇。不同于傳統(tǒng)的誘發(fā)電位儀設(shè)計(jì),,本文將大部分分立元件實(shí)現(xiàn)的功能集成到了FPGA芯片中,,實(shí)現(xiàn)多種刺激模式和濾波模塊以及實(shí)現(xiàn)對(duì)外圍器件的控制,不僅提高了集成度使儀器小型化,、便攜化成為可能,,而且片內(nèi)模塊可反復(fù)修改,提高了設(shè)計(jì)開發(fā)效率降低了成本,,也可以方便地實(shí)現(xiàn)各模塊之間的同步,。

2.2 軟件模塊整體設(shè)計(jì)

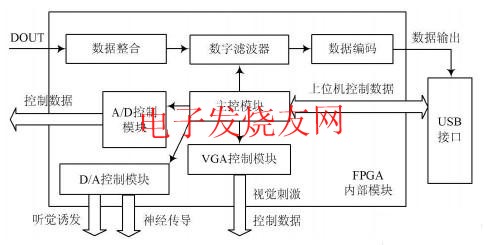

本設(shè)計(jì)中,F(xiàn)PGA芯片軟件模塊包括了誘發(fā)電位刺激模塊,、信號(hào)傳輸控制模塊和數(shù)字信號(hào)處理模塊三大部分;由共同的同步信號(hào)協(xié)同合作,,完成誘發(fā)電位儀的誘發(fā)刺激、信號(hào)的傳輸,、數(shù)字濾波等核心控制處理功能,。FPGA內(nèi)軟件模塊框圖如圖2所示。

圖2 FPGA 內(nèi)部功能結(jié)構(gòu)模塊

2.3 誘發(fā)電位刺激模塊

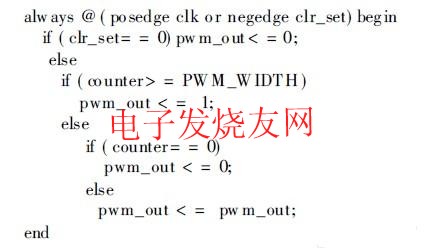

在FPGA芯片中設(shè)計(jì)了誘發(fā)電位刺激模塊,,主要功能包括:聽覺誘發(fā)電位刺激,、神經(jīng)傳導(dǎo)刺激和視覺誘發(fā)電位刺激。刺激信號(hào)主要由脈沖信號(hào)進(jìn)行控制,,通過 FPGA芯片可以直接輸出脈沖信號(hào)和VGA控制信號(hào),。聽覺誘發(fā)刺激信號(hào)和神經(jīng)傳導(dǎo)刺激信號(hào)可由FPGA輸出的脈沖信號(hào)經(jīng)功率放大后產(chǎn)生,在此聽覺誘發(fā)電位刺激信號(hào)為雙通道,,一路信號(hào)產(chǎn)生脈沖信號(hào)如PWM(脈寬調(diào)制)波,,另一路由FPGA芯片內(nèi)部模塊通過DA轉(zhuǎn)換器產(chǎn)生白噪聲,而神經(jīng)傳導(dǎo)刺激信號(hào)可直接由 FPGA輸出PWM脈沖直接驅(qū)動(dòng)電壓放大器生成,。通過Verilog硬件描述語言,,在FPGA中實(shí)現(xiàn)誘發(fā)電位刺激源信號(hào),并通過FPGA端口輸出,,例如在芯片中使用以下代碼可產(chǎn)生一個(gè)占空比為PWM_WIDTH:1的PWM波形:

視覺誘發(fā)刺激信號(hào)由在FPGA芯片中存儲(chǔ)的刺激圖像數(shù)據(jù)直接產(chǎn)生VGA時(shí)序控制信號(hào),,控制VGA顯示器顯示棋盤格或彩條刺激圖像給予人體視覺刺激,。

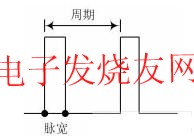

誘發(fā)電位刺激信號(hào)主要參數(shù)包括刺激脈寬、刺激頻率,、刺激強(qiáng)度,、刺激類型和刺激模式,USB芯片從上位機(jī)接收到參數(shù)配置信號(hào),,傳遞給誘發(fā)刺激信號(hào)生成模塊發(fā)出脈沖,。例如,生成聽覺誘發(fā)電位刺激信號(hào)如圖3所示,,它的刺激脈寬為0.2 ms,刺激頻率為12 Hz,,設(shè)置某一刺激強(qiáng)度(由分貝進(jìn)行度量);而生成視覺誘發(fā)電位刺激信號(hào),,刺激頻率為2 Hz,刺激類型為棋盤格模式,,刺激模式為16×16,。

圖3 刺激信號(hào)脈寬和周期

2.4 信號(hào)傳輸控制模塊

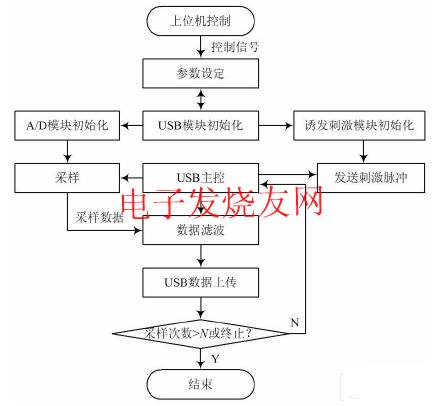

在FPGA內(nèi)部將完成誘發(fā)電位儀同步信號(hào)發(fā)生模塊、A/D轉(zhuǎn)換器的控制,、USB傳輸控制端口和上位機(jī)命令解析模塊,,從而形成一整個(gè)誘發(fā)電位儀核心處理控制模塊,可以方便地使用各個(gè)模塊來完成外圍器件的初始化,、工作模式配置和系統(tǒng)的數(shù)據(jù)傳輸,。圖4為信號(hào)傳輸控制流程圖。

圖4 信號(hào)傳輸控制流程圖

2.5 數(shù)字信號(hào)處理模塊

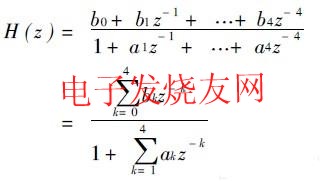

數(shù)字信號(hào)處理模塊集成到FPGA中,,可以將算法拆分,,形成大規(guī)模的數(shù)字信號(hào)處理并行結(jié)構(gòu),將極大地提高處理速度,,且性能不會(huì)下降,,如模式識(shí)別算法、盲源分離算法等,,均比較適合集成到FPGA中實(shí)現(xiàn),。在前置模擬電路放大之前,腦電信號(hào)為微弱混雜的信號(hào),,需要做一些濾波處理,,而此處可以將前段部分的帶通濾波電路轉(zhuǎn)化為數(shù)字濾波器,設(shè)置到FPGA芯片中去,,可簡化電路結(jié)構(gòu),,使系統(tǒng)整體體積大大減小。本設(shè)計(jì)在FPGA芯片中搭建了四階無限脈沖數(shù)字濾波器,,其系統(tǒng)傳遞函數(shù)H(z)如下:

將誘發(fā)電位信號(hào)放大模/數(shù)轉(zhuǎn)換之后的數(shù)據(jù)實(shí)時(shí)經(jīng)過濾波,,實(shí)現(xiàn)信號(hào)的前置處理,經(jīng)測試效果良好。利用FPGA的并行性,,在每個(gè)通道設(shè)置一個(gè)數(shù)字濾波器,,大大增強(qiáng)了系統(tǒng)實(shí)時(shí)性,而且可探索自適應(yīng),、小波數(shù)字濾波器等設(shè)計(jì),,在硬件層次提高系統(tǒng)的處理能力。

3 高精度多通道模/數(shù)轉(zhuǎn)換器ADSl258

在誘發(fā)電位儀采集系統(tǒng)中,,模/數(shù)轉(zhuǎn)換模塊芯片的選取對(duì)整個(gè)采集系統(tǒng)的結(jié)構(gòu)和性能影響非常大,,本文模/數(shù)轉(zhuǎn)換芯片選用ADSl258器件,使得本系統(tǒng)達(dá)到多通道高分辨率的要求,。

3.1 ADSl258的主要特點(diǎn)

ADSl258是16通道24位分辨率的低噪聲模/數(shù)轉(zhuǎn)換芯片,,全量程5 V的單端輸入范圍或者±2.5 V的真雙極輸入,每個(gè)通道采樣速率最高23.7 KSPS(16通道同時(shí)采樣),,單個(gè)通道采樣最高可達(dá)400 KSPS,,通過SPI兼容接口進(jìn)行工作模式配置和串行數(shù)字通信,使用方便,。選用此芯片,,電壓分辨率即可達(dá)到1 μV,因此信號(hào)放大和調(diào)理預(yù)處理電路的放大倍數(shù)只要100倍就可滿足誘發(fā)電位儀的技術(shù)要求,,大大簡化了前級(jí)電路,。

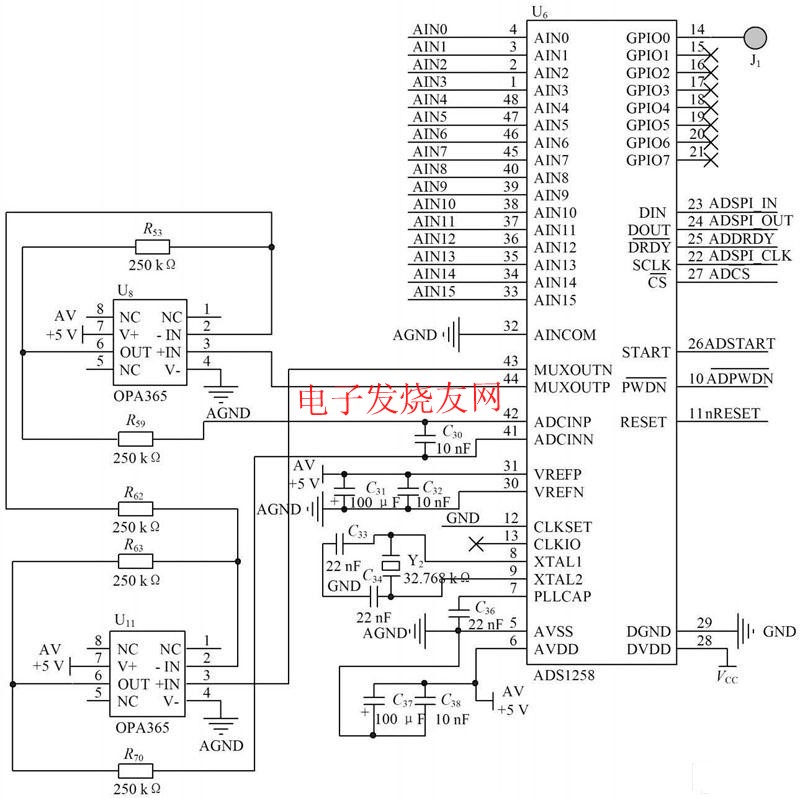

3.2 ADSl258與FPGA接口電路

ADSl258通過一個(gè)SPI兼容串行接口將數(shù)據(jù)寫入配置寄存器,使用命令控制轉(zhuǎn)換器以此來控制A/D芯片的工作模式,,并最終讀取通道數(shù)據(jù),。接口包含,SCLK,,DIN 和DOUT四個(gè)信號(hào),。對(duì)ADSl258的所有操作都得先向其寫入命令,然后由AD根據(jù)寫入的命令做相應(yīng)的操作,。經(jīng)過FPGA的A/D配置模塊啟動(dòng)之后,,ADSl258將處于固定通道掃描模式下或者自動(dòng)通道掃描模式下,ADSl258將可轉(zhuǎn)換16路共模輸入信號(hào)或8路差分輸入信號(hào),。模擬信號(hào)由AIN口輸入,,輸入范圍0~+5 V。外圍控制端口接駁到FPGA,,由FPGA控制模塊控制A/D采樣,,由進(jìn)行選通,START啟動(dòng)ADC開始工作,,通過DIN輸入命令之后由DOUT輸出轉(zhuǎn)換結(jié)果,,共使用8個(gè)端口與FPGA芯片的端口相連接,。具體接口電路的實(shí)現(xiàn)如圖5所示。

圖5 ADS1258 與FPGA 芯片的接口電路

4 結(jié)語

利用FPGA芯片豐富的資源,,將誘發(fā)電位儀的刺激信號(hào)源,、模/數(shù)轉(zhuǎn)換控制邏輯和USB接口控制與數(shù)據(jù)傳輸以及數(shù)字信號(hào)處理等模塊設(shè)計(jì)在單個(gè)芯片上,可最大限度地簡化誘發(fā)電位儀的硬件電路復(fù)雜度,,利用其可編程性極大地方便了硬件設(shè)計(jì),,結(jié)合ADSl258的高分辨率的優(yōu)勢,可以使系統(tǒng)既具有優(yōu)異的性能又具有很高的集成度,,而且本設(shè)計(jì)尚余很多FPGA的I/O口,,如需更多通道則僅需要加入多塊A/D芯片,具有較高的應(yīng)用價(jià)值,。