摘 要: DDS具有分辨率高、轉(zhuǎn)換速度快的優(yōu)點。在一些需要高頻率分辨率、高轉(zhuǎn)換速度的應(yīng)用場合,尤其是雷達(dá)及通信系統(tǒng)中的跳頻信號源中,DDS技術(shù)具有其它頻率合成方法無法比擬的優(yōu)勢,是一種很有發(fā)展前途的技術(shù)。介紹了DDS的基本原理及DDS芯片的功能特點以及DDS芯片AD9852的結(jié)構(gòu)、特點,并采用PIC單片機(jī)控制AD9852,實現(xiàn)了跳頻頻率合成器。

關(guān)鍵詞: DDS 頻率分辨率 轉(zhuǎn)換速度 頻率合成 PIC單片機(jī)

在研制雷達(dá)系統(tǒng)時,常常需要應(yīng)用頻率合成技術(shù)來實現(xiàn)跳頻信號源。頻率合成是指從一個高穩(wěn)定的參考頻率,經(jīng)過各種技術(shù)處理,生成一系列穩(wěn)定的頻率輸出?眼1?演。現(xiàn)在應(yīng)用最廣的是鎖相環(huán)(PLL)頻率合成技術(shù),它是通過變化PLL中的分頻比N來實現(xiàn)輸出頻率的跳頻的,但無法避免縮短環(huán)路鎖定時間與提高頻率分辨率的矛盾,因此很難同時滿足高速和高精確度的要求。直接數(shù)字式頻率合成(DDS)是近年發(fā)展起來的一種新的頻率合成技術(shù)。它將先進(jìn)的數(shù)字處理理論與方法引入頻率合成領(lǐng)域,是繼直接頻率合成(DS)和間接頻率合成(IS)之后的第三代頻率合成技術(shù)。DDS的優(yōu)點是:相對帶寬很寬,頻率轉(zhuǎn)換時間極短(ns級),頻率分辨率很高(可達(dá)μHz),全數(shù)字化結(jié)構(gòu)便于集成,輸出相位連續(xù),頻率、相位和幅度均可實現(xiàn)程控。因此能夠與計算機(jī)緊密結(jié)合在一起,充分發(fā)揮軟件的作用。在實際應(yīng)用中,可以采用單片機(jī)來代替計算機(jī)對DDS芯片進(jìn)行控制,實現(xiàn)合成頻率的輸出。因此在很短的時間內(nèi),DDS得到了飛速的發(fā)展和廣泛的應(yīng)用[3]。

1 DDS的基本原理

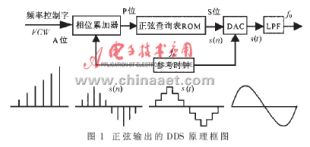

DDS技術(shù)是一種把一系列數(shù)字量形式的信號通過DAC轉(zhuǎn)換成模擬量形式的信號的合成技術(shù)。正弦輸出的DDS的原理框圖如圖1所示。相位累加器在A位頻率控制字FCW的控制下,以參考時鐘頻率fc為采樣率,產(chǎn)生待合成信號相位的數(shù)字線性序列。將其高P位作為地址碼,通過查詢正弦表ROM,產(chǎn)生S位對應(yīng)信號波形的數(shù)字序列S(n),再由數(shù)/模轉(zhuǎn)換器(DAC)將其轉(zhuǎn)化為階梯模擬電壓波形S(t),最后由低通濾波器LPF平滑為正弦波輸出。

頻率控制字FCW和時鐘頻率fc共同決定了DDS輸出信號的頻率f0,它們之間的關(guān)系滿足:

所以,在DDS結(jié)構(gòu)及fc確定的前提下,通過FCW的控制就可以方便地控制輸出頻率f0。其頻率分辨率為:

按照Naquist準(zhǔn)則,最高輸出頻率可達(dá)0.5fc。但考慮到實際低通濾波器的限制,最高輸出頻率一般為0.4fc。

由于DAC非線性作用的存在,使得查表所得的幅度序列從DAC的輸入到輸出要經(jīng)過一個非線性過程。于是就會產(chǎn)生輸出信號f0的諧波分量。又因為DDS是一個采樣系統(tǒng),所以這些諧波會以fc為周期搬移,即:

其中,u、v為任意整數(shù)。它們落到Nyquist帶寬內(nèi)就形成了有害的雜散頻率,頻率的位置可以確定,但幅度難以確定。所以在工程設(shè)計過程中要充分考慮輸出頻帶,注意避免上述雜散分量落入其中,以此來獲得較好的雜散指標(biāo)。

2 DDS芯片介紹

DDS的諸多優(yōu)點使它得到了非常廣泛的應(yīng)用。在數(shù)字調(diào)制方面,它可以用來實現(xiàn)FSK、QPSK、8PSK等調(diào)制。在雷達(dá)頻率源方面,它可以實現(xiàn)多點、窄步長、高相噪的點頻輸出頻率源以及線性調(diào)頻輸出頻率源。在擴(kuò)頻通信方面,它可實現(xiàn)CDMA工作方式以及多種規(guī)律的跳頻模式。

現(xiàn)在國外已經(jīng)有非常成熟的DDS芯片。Qualcomm公司推出了DDS系列Q2220、Q2230、Q2334、Q2240、Q2368,其中Q2368的時鐘頻率為130MHz,分辨率為0.03Hz,雜散控制為-76dBc,變頻時間為0.1μs;美國AD公司也相繼推出了他們的DDS系列:AD9850、AD9851、可以實現(xiàn)線性調(diào)頻的AD9852、兩路正交輸出的AD9854以及以DDS為核心的QPSK調(diào)制器AD9853、數(shù)字上變頻器AD9856和AD9857。AD公司的產(chǎn)品全部內(nèi)置了D/A變換器,稱為Complete-DDS。其中AD9852時鐘頻率為300MHz,近端雜散抑制優(yōu)于-80dBc,遠(yuǎn)端優(yōu)于-48dBc,相位噪聲為-148dBc/Hz@10kHz,頻率跳變速度為130ns,頻率分辨率為1μHz。

AD9852主要由48位的頻率寄存器、48位相位累加器、正(余)弦查詢表(帶正交輸出)、幅度調(diào)制寄存器、乘法器和12位D/A轉(zhuǎn)換器構(gòu)成。

AD9852可以實現(xiàn)單頻、FSK、Chirp、FM Chirp、BPSK等多種輸出形式。用其中的Chirp模式和FSK模式可以方便地實現(xiàn)跳頻功能,滿足雷達(dá)跳頻系統(tǒng)的要求。使用時只要初始化DDS,設(shè)定跳頻持續(xù)時間和跳頻間隔時間即可實現(xiàn)自動跳頻。這比以往的DDS芯片如AD9850要方便得多。

AD9852的管腳分為三部分:(1)數(shù)據(jù)及控制端口;(2)電源部分;(3)參考及輸出部分。

由于AD9852是目前市場上性價比較高的DDS器件之一,而且AD9852具有線性調(diào)頻功能,可以方便實現(xiàn)頻率的跳變。所以在雷達(dá)跳頻系統(tǒng)中最終采用了AD9852芯片。下面就該芯片的應(yīng)用設(shè)計做一簡要介紹[2]。

3 頻率合成器的設(shè)計

要讓AD9852工作,需要按下列流程初始化:

(1)數(shù)據(jù)在WR信號控制下從并行輸入口D0~D1寫入48位并行寄存器,或在SCLK控制下從串行輸入口SDATA寫入48位串行寄存器。

(2)對S/P SELECT置1或置0以決定輸入數(shù)據(jù)是并行還是串行。1為并行,0為串行。

(3)AD9852芯片內(nèi)部不帶帶通濾波器,所以外圍電路中應(yīng)該按實際工作需要外接帶通濾波器,濾除不需要的頻率分量[1]。

利用一片AD9852及簡單的外圍電路實現(xiàn)頻率合成器的結(jié)構(gòu)框圖如圖2所示。

根據(jù)我在設(shè)計過程中的實際經(jīng)驗,有以下幾個問題需要注意。

3.1 單片機(jī)的選擇

因為AD9852是3.3V系統(tǒng),所以必須選擇可以工作在3.3V的單片機(jī)。設(shè)計之初,忽略了這個問題,選用了普通51系列芯片,因為其輸出電平只能為5V, 高于3.3V,DDS芯片因此被損壞。后打算采用51系列,但因為其在市場上很難買到,所以最終采用了Microchip公司的PIC系列單片機(jī)PIC16F874。該單片機(jī)可以工作在2.2~5.5V的范圍內(nèi)[4]。又考慮到設(shè)計要求的高速控制,PIC16F874單片機(jī)的速度是51系列的3倍,所以PIC16F874單片機(jī)滿足設(shè)計要求。

3.2 單片機(jī)的外圍電路

DDS的工作電壓是3.3V,而PIC的掉電復(fù)位電壓是4.5V?眼4?演,所以PIC單片機(jī)的外圍電路需要使用上電復(fù)位模式。

3.3 要避開DDS雜散較大的輸出頻點

在實際應(yīng)用中,還有一些點的雜散信號很大,而且離主頻很近,無法去除。所以應(yīng)該避免輸出這些頻點。這些頻點為靠近fc/3、fc/4、fc/5、fc/6……的頻點。

3.4 去 耦

在一個電子系統(tǒng)中,通常多個器件共用一個電源。而電源線給交流信號提供了一個通路,使得交流信號通過電源線在器件之間傳輸,形成了干擾。所以必須在器件之間和電源到器件之間的電源線上加入濾波部分,濾掉交流干擾,稱為去耦。電源的去耦通常用幾個并聯(lián)電容和串聯(lián)電感來實現(xiàn),如圖3所示。

3.5 接 地

接地可以分為單點接地和多點接地。一般認(rèn)為,連線長度大于信號波長的二十分之一時,應(yīng)采用多點接地;反之,則采用單點接地。

實現(xiàn)多點接地就要在PCB板上布出一個面積較大的接地面,此接地面又與接大地的屏蔽外殼大面積接觸。這樣整個地的阻抗很小,電位可以認(rèn)為是一致的,各器件就近接地,就避免了在地線上形成干擾。

在數(shù)模混和的電路中,由于數(shù)字部分干擾源很多,所以模擬部分易受影響。因此要注意把模擬地和數(shù)字地分開。一般的方法是用一根線來連接數(shù)字地和模擬地,而且只在一處相連,這樣可以較好地切斷數(shù)字部分的干擾源。

3.6 充分利用DDS的sweet pots[2]

如前所述,在DDS中,其相位累加器的位數(shù)為A,但用來查詢正弦表的位數(shù)只有其高P位,剩下的就四舍五入丟棄了,這樣做會產(chǎn)生一種相位截斷誤差。但是如果相位累加器中的A-P位恰好為0,則其相位截斷誤差就為0,其輸出頻點的特性就會比較好,這就是所謂的“sweet pots”。所以在DDS單點輸出時,使DDS盡量在sweet pots頻點輸出,可以達(dá)到優(yōu)化輸出特性的目的。

3.7 DDS參考信號輸入端的注意事項

由于采用了參考信號單端輸入的方式,所以REFCLKB端應(yīng)該接地或電源;參考信號輸入端REFCLK要跟電源相連接。因為DDS的參考信號要求有1.6V的直流電平,在參考信號輸入到REFCLK端的端點處,應(yīng)接一個5.1kΩ的電阻到3.3V直流電源,同時接一個0~10kΩ的可變電阻(此處取5kΩ)到100Ω的電阻,經(jīng)過電阻分壓,REFCLK端就有1.6V的直流電壓。這個0~10kΩ的可調(diào)電阻同時用來微調(diào)REFCLK端對地的電阻,以調(diào)節(jié)REFCLK的直流電位,具體情況請參看圖4。圖4中的∏形濾波部分是為了濾除電源對REFCLK端的干擾。該頻率合成器原理圖如圖4所示。

檢驗證明,利用AD9852設(shè)計的頻率合成器具有跳頻速度快、頻率分辨率高、體積小、系統(tǒng)工作穩(wěn)定、使用方便等優(yōu)點。因此它有很強(qiáng)的實用價值。

DDS除了用于跳頻系統(tǒng)中外,還可以用于任意波形產(chǎn)生、信號調(diào)制等。隨著高速集成電路的飛速發(fā)展,DDS必將開拓更多新的應(yīng)用領(lǐng)域。

參考文獻(xiàn)

1 張厥盛,曹麗娜.鎖相與頻率合成技術(shù).成都:電子科技大學(xué)出版社, 1995.6

2 AD9852-CMOS,300MHz Complete DDS Synthesizer. Technical Data Sheet. Analog Device Inc., 2000

3 渠麗娟.頻率合成技術(shù)的發(fā)展及應(yīng)用. 綜述報告,成都:電子科技大學(xué),2001,12

4 Technical Data Sheet of PIC16F874.Microchip Technology Inc.,2001