E類功率放大器是一種高效率的功率放大器,在理想情況下,它可以達到100%的效率。在這種功率放大器中,功率管的驅(qū)動電壓幅度必須足夠強,使得輸出功率管相當于一個受控的開關(guān),在完全導通(晶體管工作于線性區(qū))和完全截止(晶體管工作于截止區(qū))之間瞬時切換。由于流過理想開關(guān)的電流波形和開關(guān)上的電壓波形沒有重疊,理想開關(guān)不消耗功耗,電源提供的直流功耗都轉(zhuǎn)換為輸出功率,將達到100%的效率。

本文針對藍牙系統(tǒng),設計時考慮寄生電感的影響,采用TSMC 0.18μm CMOS工藝設計出了一個差分E類功率放大器,有效地抑制了寄生電感對系統(tǒng)性能的影響,同時給出了設計方法和設計過程。

1 理想射頻E類功放工作原理及設計方程

晶體管E類功率放大器由單個晶體管和負載網(wǎng)絡等組成。在激勵信號作用下,晶體管工作在開關(guān)狀態(tài)。當晶體管飽和導通時,漏端電壓波形由晶體管決定,即由晶體管的導通電阻決定。當晶體管截至時,漏端電壓波形由負載網(wǎng)絡的瞬態(tài)響應所決定。

E類功率放大器要保持高效率,其負載網(wǎng)絡的瞬態(tài)響應必須滿足以下3個條件:(1)晶體管截至時,漏端電壓必須延遲到晶體管“開關(guān)”斷開后才開始上升。(2)晶體管導通時,漏端電壓必須為零。(3)晶體管飽和導通時,漏端電壓對時間的導數(shù)必須為零。

根據(jù)上述3點,具體分析E類功率放大器工作原理及其電路參數(shù)的計算。圖l為E類功率放大器的電路原理圖,其中Cd為MOS管寄生電容與片上電容的和,L1 為高頻扼流圈。L0,C0為串聯(lián)諧振網(wǎng)絡,Rload為等效負載。當晶體管飽和導通時,漏端電壓為零,由于負載網(wǎng)絡的影響,電流Ld(ωt)有一個上升和下降的過程。當晶體管截至時,漏端電壓則完全由負載網(wǎng)絡所決定。圖2所示為理想E類功放漏端電壓和電流時域波形,由圖可知所以Id(ωt)與 Vds(ωt)不同時出現(xiàn),使放大器效率趨近于100%,該效率主要由負載網(wǎng)絡參數(shù)最佳設計來實現(xiàn)的。

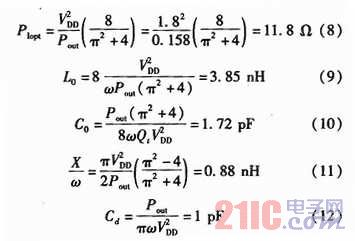

由文獻可求得圖1所示電路中各個元件的值,即

2 射頻CMOS E類功率放大器非理想因素分析

分析了理想功放的設計方程,有載QL的選擇,負載網(wǎng)絡元器件的選取等,但是這些理論基礎都建立在理想情況下,而在實際設計中,必須考慮非理想的因素。非理想因素有多種:

(1)寄生電感的影響。

(2)有限的Chock電感。

(3)NMOS開關(guān)管有限的導通電阻。

(4)NMOS管寄生電容Cd的非線性。

(5)負載網(wǎng)絡的有限Q值。

(6)功率放大器阻抗匹配網(wǎng)絡的損耗。

其中寄生電感對功放的設計結(jié)果影響最大,因此將著重分析寄生電感的產(chǎn)生及其改進措施。

寄生電感分析與改進措施

功率放大器在實際應用中有3個主要的寄生源,分別為RF電路板、封裝和IC。具體表現(xiàn)在輸出級源級到地的寄生電感,它對功率放大器的輸出功率、PAE、穩(wěn)定性等產(chǎn)生巨大的影響。寄生電感可以分為以下3個方面:

(1)在IC級,功率放大器一般用通孔結(jié)構(gòu)或者鍵合線聯(lián)接到襯底地。在實際應用中,可使用多線鍵合減小地電感。

(2)在封裝級,通常用接到封裝底部的接地片,或通過封裝引線架的地連接實現(xiàn)接地。可用各種方法調(diào)整引線架,以減小地電感。

(3)在RF電路板級的地連接一般用通孔接到電路板中間層的專門接地平板。接地的質(zhì)量由物理特性和與系統(tǒng)地的連接好壞確定。

接電源(地)的封裝線對電路的影響與高速電路中同步開關(guān)噪聲原理相似。交流電流在封裝線上引起的感應電勢為

![]()

其中,Le為電源和地封裝線的總等效電感。假設當Le=1 nH,交流電流幅度i為300 mA時,即可達300 mV,如果電感和寄生電容發(fā)生諧振,振蕩信號的幅度會更高,必然會對輸出信號形成干擾。電源(地)封裝線對電路的另一影響是信號或其諧波可能引起振蕩,這些影響是很難通過在電源和地之間接并聯(lián)大耦合電容得到抑制的。因此采用合理的電路結(jié)構(gòu)才能減輕寄生電感對系統(tǒng)的影響。

3 射頻CMOS E類功率放大器設計

功率放大器的輸出級是電路最關(guān)鍵、最復雜的部分,因為它的輸出是芯片射頻接口,除了器件的非線性特性外,還必須要考慮Pad、輸出功率管漏端到地的寄生電感、封裝結(jié)構(gòu)、輸出電壓擺幅、MOS器件擊穿和輸出端口的阻抗匹配等多種因素的影響。在這些因素中,輸出功率管漏端到地的寄生電感對功放性能影響最嚴重,包括鍵合線電感、PCB板級電路寄生電感等的影響。鍵合線電感的經(jīng)驗值是1 nH/mm,可以并聯(lián)大量的鍵合線來減少鍵合線電感值,但是很難控制其精度,有文獻在仿真時僅加入0.4 nH的電感模擬這些寄生量,但是從測試結(jié)果分析來看,寄生電感遠不只0.4 nH,因此取1.5 nH來模擬功率管源端到地的寄生電感量。

3.1 應用理想方程的功放級設計

功放內(nèi)核電路如圖3所示,采用偽差分E類功率放大器,為簡化分析過程,分析右半邊電路圖,L5為片上平面螺旋電感,L6,L7,Ls為鍵合線電感。輸出級為E類功放,Choke電感L6阻止交流信號通過,并給晶體管提供直流電流Idc。反饋網(wǎng)絡Cs和Rs增強功率放大器的穩(wěn)定性和降低輸出電壓駐波比。 L7、C3組成一個串聯(lián)LC網(wǎng)絡,包括一個諧振網(wǎng)絡和部分剩余電感,當該諧振網(wǎng)絡的品質(zhì)因子足夠高時,流過該網(wǎng)絡的電流為理想的正弦型信號,所有的諧波成分都被濾除。并聯(lián)電容Cs由兩部分組成,一部分是晶體管的寄生電容,另一部分是實際引入的電容。

在設計之初,先利用理想設計方程,估算E類功率放大器的各個參數(shù),再采用諧波平衡法(Harmonic Balance)適當?shù)卣{(diào)整參數(shù)。其中Pout=24 dBm,電源電壓VDD=1.8 V,取Qt=5,根據(jù)之前給出的設計方程得出

以上參數(shù)選取依賴于理想設計方程參數(shù),只考慮到最佳負載為實部的情況,考慮到一些非理想因素,利用ADS軟件,采用Load Pull技術(shù)適當?shù)卣{(diào)整參數(shù)。

3.2 應用Load Pull技術(shù)的功放級設計

在功放級設計中,如何使輸出功率最大化是最主要的設計目標。

基本思路是通過CAD技術(shù)進行Load Pull仿真確定最佳的源和負載阻抗。所謂的Load Pull仿真,就是在負載阻抗很大范圍內(nèi)掃描,逐點作諧波平衡分析計算出輸出功率,在圓圖上畫出等功率圓。因此根據(jù)設計目標的輸出功率,就能在圓圖上找到與之對應的一系列的輸出阻抗。同樣的原理,可以畫出等PAE的圓,折中考慮輸出功率,PAE和負載網(wǎng)絡的有載QL等就能確定最佳阻抗。

4 仿真結(jié)果與分析

根據(jù)負載牽引仿真結(jié)果得到負載的最佳阻抗值,下面就是采用適當?shù)钠ヅ湫问?集總參數(shù)或分布參數(shù))實現(xiàn)輸出匹配網(wǎng)絡,并將該輸出匹配網(wǎng)絡加入到電路中進行源負載牽引仿真,以便得到源的最佳輸入阻抗。

這樣通過兩次負載牽引得到最佳輸入輸出阻抗,并選擇適當?shù)钠ヅ潆娐穼?0 Ω變化到所需的阻抗。圖4結(jié)果表明,將負載匹配到31+j24時,該結(jié)構(gòu)具有最大輸出功率26.78 dBm,最大PAE為60.56%。采用L型匹配網(wǎng)絡實現(xiàn)輸入、輸出阻抗的匹配。

表1的Load Pull結(jié)果是有一定條件完成的,其前級驅(qū)動信號并不是理想的開關(guān)信號,而是輸入信號為O dBm,經(jīng)過Cascode驅(qū)動級放大后的信號。利用理想設計方程得到的結(jié)果比較差的原因是,得出理想方程的假設條件和實際應用條件不一樣,具體有:

(1)驅(qū)動信號并不是理想的具有足夠驅(qū)動能力的占空比為50%的方波信號。

(2)仿真時在輸出級功率管的源端加入了1.5 nH的寄生電感。

(3)RFC電感并不是無窮大。

(4)輸出級功率管的導通電阻并不為O,需要一定的導通時間。

(5)負載諧振網(wǎng)絡Q值也是有限的。

5 結(jié)束語

分析比較了CMOS工藝和GaAs工藝的優(yōu)缺點,以及設計過程中所要考慮的非理想因素,著重分析寄生電感的產(chǎn)生,對功放性能的影響,以及如何抑制寄生電感對功放的影響。最終采用理想設計方程和Load Pull技術(shù),基于0.18μm CMOS工藝實現(xiàn)了一個差分的E類功放,ADS仿真結(jié)果表明采用差分結(jié)構(gòu)較好地抑制了漏端電感對功率放大器性能的影響,提高功放的PAE,為實現(xiàn)單片集成發(fā)射機奠定了基礎。