摘要 ADI公司的Blackfin" title="Blackfin">Blackfin系列處理器具有強(qiáng)大數(shù)據(jù)處理和控制能力,在儀器控制、音視頻處理等系統(tǒng)中應(yīng)用廣泛。在應(yīng)用中顯示輸出是必要的,文中根據(jù)Blackfin DSP處理器的特點(diǎn)介紹了一種簡單實(shí)用的液晶" title="液晶">液晶接口設(shè)計(jì)方法。

關(guān)鍵詞 Blackfin;BF532;TFT LCD

TFT LCD液晶顯示器與數(shù)碼管和點(diǎn)陣液晶相比具有體積小巧、控制簡單、可以顯示豐富多彩的圖像視頻信息。文中以ADSP_BF532為例介紹了一種Blackfin DSP處理器與TFT LCD液晶顯示器的接口設(shè)計(jì),在Blackfin DSP的系統(tǒng)設(shè)計(jì)中具有一定的參考價(jià)值。

1 Blackfin DSP處理器與TFT LCD液晶屏簡介

Blackfin DSP處理器是基于ADI公司和Intel公司聯(lián)合開發(fā)的微信號(hào)架構(gòu)(MSA)的一種16位定點(diǎn)DSP處理器,具有較強(qiáng)的數(shù)據(jù)處理能力,能夠完成視頻、圖像、音頻和通信數(shù)據(jù)的數(shù)字化處理等。同時(shí)還具有綜合控制能力,單芯片即可完成通常由DSP+控制器完成的功能。Blackfin DSP處理器可廣泛應(yīng)用在各種嵌入式設(shè)備、儀器中,完成系統(tǒng)控制和數(shù)據(jù)處理。

PPI(Parallel Port Interface)接口是Blackfin DSP處理器的并行數(shù)據(jù)接口,主要用于數(shù)據(jù)的高速傳輸。它包括16位數(shù)據(jù)線,3個(gè)同步信號(hào)和一個(gè)時(shí)鐘信號(hào)。PPI接口直接與DMA通道整合,數(shù)據(jù)傳輸寬度可靈活配置,支持8位、10~16位等多種數(shù)據(jù)寬度。PPI的工作模式有兩種:通用模式(GP模式)和ITU-656模式,其中通用模式下可方便地與數(shù)字液晶屏連接。

Blaekfin DSP處理器的DMA傳輸可以是內(nèi)部與外部存儲(chǔ)器之間,也可以是內(nèi)部或外部存儲(chǔ)器與SPI口、SPORT口、UART口、PPI口之間。

Blackfin DSP處理器的DMA傳輸可基于描述符配置,也可基于寄存器配置。基于描述符的DMA傳輸使用存放在存儲(chǔ)器內(nèi)的一組參數(shù)來初始化一個(gè)DMA傳輸。基于描述符的DMA傳輸允許多個(gè)DMA序列鏈接在一起,一個(gè)DMA傳輸完成后緊接著進(jìn)行下一個(gè)DMA傳輸。基于寄存器的DMA傳輸允許處理器通過對(duì)控制寄存器編程來啟動(dòng)一個(gè)DMA傳輸。一次DMA傳輸完成后,可以用原來設(shè)置的值自動(dòng)更新控制寄存器,連續(xù)傳輸數(shù)據(jù)。

Blackfin DSP處理器支持二維DMA傳輸,特別適合于視頻數(shù)據(jù)傳輸。二維DMA的相關(guān)控制寄存器如下:

配置寄存器(DMAx_CONFIG/MDMA_yy_CONFIG):設(shè)置二維DMA使能方式,中斷產(chǎn)生方式。

內(nèi)部循環(huán)計(jì)數(shù)寄存器(DMAx_X_COUNT/MDMA_yy_X_COUNT):保存二維DMA內(nèi)層循環(huán)的數(shù)目(應(yīng)≥2)。

內(nèi)層循環(huán)地址增量寄存器(DMAx_X_MODIFY/MDMA_yy_X_MODIFY):保存每一次內(nèi)層循環(huán)計(jì)數(shù)器加1后DMA操作地址在內(nèi)存中的增量,此增量應(yīng)該是二維DMA操作的數(shù)據(jù)單元長度的整數(shù)倍。

外層循環(huán)計(jì)數(shù)寄存器(DMAx_Y_COUNT/MDMA_yy_Y_COUNT):保存外層循環(huán)的數(shù)目。

外層循環(huán)地址增量寄存器(DMAx_Y_MODIFY/MDMA_yy_Y_MODIFY):保存每一次外層循環(huán)計(jì)數(shù)器加1后DMA操作地址在內(nèi)存中的增量,可以是負(fù)值,此增量應(yīng)該是二維DMA操作的數(shù)據(jù)單元長度的整數(shù)倍。

AT070TN83 V.1是群創(chuàng)生產(chǎn)的一款數(shù)字液晶顯示屏,屏幕尺寸為7英寸(17.78 cm),分辨率800×480,23行消隱行。采用5 V(背光)和3.3 V(I/0)雙電源供電。該液晶具有DE模式和HV模式,考慮Blackfin PPI的接口特點(diǎn),本系統(tǒng)采用HV模式進(jìn)行數(shù)據(jù)傳輸。

液晶時(shí)序如圖1和圖2所示。

圖l和圖2中相應(yīng)的參數(shù)參照AT070TN83 V.1手冊(cè)。液晶同步時(shí)序可以看做是滿足一定要求的PWM波,可利用Blackfin DSP的定時(shí)器支持PWM輸出的特性輸出此信號(hào)。

2 系統(tǒng)總體設(shè)計(jì)

該液晶屏的輸入格式為RGB666格式,而ADSPBF532的PPI接口數(shù)據(jù)線只有16位,根據(jù)人眼的視覺特性(對(duì)綠色最敏感),將紅色和藍(lán)色的最高位和最低位分別接在一起,其他數(shù)據(jù)線對(duì)應(yīng)連接。

液晶所需的同步信號(hào)HS和VS分別由ADSPBF532的定時(shí)器1和定時(shí)器2產(chǎn)生。通過配置ADSPBF532定時(shí)器的相關(guān)寄存器可以精確地控制輸出PWM

波的有效沿,周期和占空比,完全匹配液晶時(shí)序。

顯示所用的時(shí)鐘信號(hào)可以由外部的獨(dú)立晶振產(chǎn)生,分別輸入液晶和DSP的PPI口。也可以由DSP的輸出時(shí)鐘分頻產(chǎn)生,再分別輸入液晶和DSP的PPI口。本系統(tǒng)使用獨(dú)立的25 MHz晶振將時(shí)鐘信號(hào)直接輸給液晶和PPI。

該液晶內(nèi)部沒有顯存,因此在使用時(shí)系統(tǒng)需要擴(kuò)展SDRAM,在SDRAM中開辟一塊區(qū)域作為顯示緩存,將需要顯示的數(shù)據(jù)寫入緩存,再由DMA傳送到PPI口進(jìn)行顯示。

系統(tǒng)總體設(shè)計(jì)框圖如圖3所示。

在外部25MHz時(shí)鐘的驅(qū)動(dòng)下DSP按照寄存器的配置輸出相應(yīng)的同步信號(hào),同時(shí)將SDRAM對(duì)應(yīng)區(qū)域中的數(shù)據(jù)從PPI口輸出。

3 軟件設(shè)計(jì)

(1)顯示緩存數(shù)據(jù)的存儲(chǔ)。

該液晶每行800點(diǎn),每個(gè)點(diǎn)對(duì)應(yīng)16位數(shù)據(jù),因此每行需要800×2 bit。每屏需要525行,包括前消隱23行,中間480行有效數(shù)據(jù),后消隱22行,因此開辟顯示緩存大小為525×800×2 bit。為了操作方便,可定義一個(gè)二維數(shù)組,二維數(shù)組中的數(shù)據(jù)與TFTLCD上的點(diǎn)具有對(duì)應(yīng)關(guān)系(數(shù)組中每兩個(gè)字節(jié)對(duì)應(yīng)LCD上的一個(gè)點(diǎn))。由于需要將顯示緩存定義在SDRAM中,因此在工程中需要添加ldf文件,將顯示緩存指定存儲(chǔ)在SDRAM中。

緩存數(shù)組的定義如下

section(“SDRAM0”)char DisplayBuffer[525][800*2]

(2)定時(shí)器初始化。

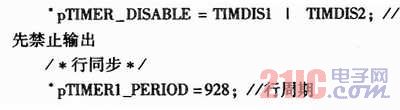

使用定時(shí)器1和定時(shí)器2分別作為行同步信號(hào)和場同步信號(hào),根據(jù)液晶時(shí)序配置定時(shí)器寄存器,包括輸出時(shí)鐘周期,脈沖寬度,有效沿,PWM模式輸出等。為了與液晶同步,使用PPI的輸入時(shí)鐘驅(qū)動(dòng)定時(shí)器。

Blackfin定時(shí)器寄存器設(shè)置如下

(3)PPI初始化。

使用通用模式(GP模式)輸出數(shù)據(jù),兩個(gè)外部幀同步信號(hào),PPI_FS1和PPI_FS2下降沿有效,PPI_DEIAY設(shè)置延時(shí)時(shí)鐘個(gè)數(shù)(行同步變高到數(shù)據(jù)輸出間的時(shí)鐘個(gè)數(shù))。

Blackfin PPI寄存器設(shè)置如下

* pPPI_DELAY=45;//輸出數(shù)據(jù)前的延時(shí)

* pPPI_COUNT=800*2-1;//每行傳輸字節(jié)數(shù),比實(shí)際值小1

注意:AT070TN83 V.1手冊(cè)中給出的輸出數(shù)據(jù)前的延時(shí)參數(shù)為40個(gè)時(shí)鐘周期,但實(shí)際使用中發(fā)現(xiàn)設(shè)為40時(shí)屏幕顯示圖像左偏,說明延時(shí)不夠,經(jīng)試驗(yàn)應(yīng)為45個(gè)時(shí)鐘周期。

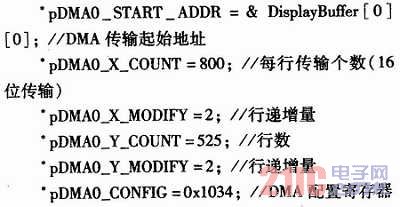

(4)DMA初始化。

使用PPI輸出數(shù)據(jù)時(shí)必須使用DMA傳輸。采用寄存器配置模式,配置DMA傳輸?shù)钠鹗嫉刂贰鬏數(shù)臄?shù)據(jù)個(gè)數(shù)、地址增量和傳輸方式。本系統(tǒng)設(shè)置為二維傳輸方式,行地址增量設(shè)置為2(16位傳輸,2 bit),縱向地址增量設(shè)置為2(上一行最后傳輸?shù)牡刂放c下一行起始地址差,2 bit),DMA傳輸模式設(shè)置為自動(dòng)緩沖模式。

Blackfin DMA寄存器設(shè)置如下

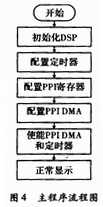

(5)主程序流程圖,如圖4所示。

主程序中首先初始化DSP(包括SDRAM,EBIU等),定時(shí)器,PPI寄存器和PPI DMA寄存器配置的先后順序要求不是絕對(duì)的,但是PPI DMA和定時(shí)器的使能必須在最后,因?yàn)槎〞r(shí)器使能后將觸發(fā)DMA開始傳輸數(shù)據(jù),所以必須在使能PPI DMA之后再使能定時(shí)器。需要改變顯示內(nèi)容時(shí)改變對(duì)應(yīng)數(shù)組中數(shù)據(jù)即可。

4 結(jié)束語

經(jīng)調(diào)試,液晶正確顯示,并且屏幕穩(wěn)定無閃爍,成功應(yīng)用在某儀器系統(tǒng)中。由于Blackfin系列處理器的內(nèi)核都是相同的,接口操作類似,因此文中介紹的方法對(duì)Blackfin系列處理器的液晶接口設(shè)計(jì)具有參考價(jià)值。