電磁兼容性的設(shè)計(jì)與測(cè)量

摘要: 1、主要技術(shù)參數(shù)電磁兼容性的設(shè)計(jì)是一項(xiàng)復(fù)雜的系統(tǒng)工程。首先要學(xué)習(xí)并掌握有關(guān)標(biāo)準(zhǔn)及規(guī)范,,然后參照實(shí)際電磁環(huán)境來(lái)提出具體的要求,,進(jìn)而制定技術(shù)和工藝的實(shí)施方案。在設(shè)計(jì)電子儀器,、設(shè)備時(shí),。應(yīng)重點(diǎn)考慮電路設(shè)計(jì)、隔離

關(guān)鍵詞:

電磁兼容

Abstract:

Key words :

1,、主要技術(shù)參數(shù)

電磁兼容" title="電磁兼容">電磁兼容性的設(shè)計(jì)是一項(xiàng)復(fù)雜的系統(tǒng)工程,。首先要學(xué)習(xí)并掌握有關(guān)標(biāo)準(zhǔn)及規(guī)范,然后參照實(shí)際電磁環(huán)境來(lái)提出具體的要求,,進(jìn)而制定技術(shù)和工藝的實(shí)施方案,。在設(shè)計(jì)電子儀器、設(shè)備時(shí),。應(yīng)重點(diǎn)考慮電路設(shè)計(jì),、隔離退耦、濾波,、接地,、屏蔽以及射頻資源的分配等問(wèn)題。舉例說(shuō)明,,設(shè)計(jì)電路時(shí)宜選噪聲高,、抗干擾能力強(qiáng)的CMOS電路來(lái)代替TTL電路,用無(wú)解點(diǎn)的可視具體情況選用低通濾波器,、高通濾波器或有源濾波器,。利用隔離變壓器或光耦合器可實(shí)現(xiàn)信號(hào)隔離及阻抗變換。選用電磁兼容性良好的VXI總線儀器系統(tǒng)來(lái)構(gòu)成測(cè)試系統(tǒng),。

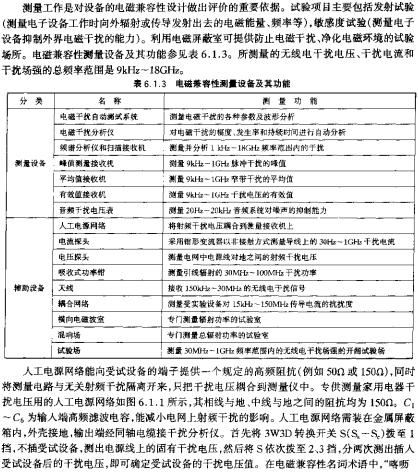

2,、電磁兼容性的測(cè)量

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載,。