引言

ADC 采用逐次逼近型(SAR)結(jié)構(gòu),具有125kHz采樣速率,12位精度。電容電荷重新分布D/A技術(shù)采用電荷按比例縮放子DAC組合,進(jìn)而大大減小了芯片電容面積,也避免了采用像電阻陣列結(jié)構(gòu)所帶來(lái)的固有直流功耗,通過(guò)對(duì)DAC級(jí)間耦合電容值的優(yōu)化設(shè)計(jì),提高了ADC精度。比較器采用自消除失調(diào)電壓的開(kāi)關(guān)電容比較器。

據(jù)調(diào)研,市場(chǎng)上現(xiàn)有觸摸屏控制器芯片主要來(lái)自ADI公司(如AD7843、AD7873、AD7877)和TI公司(如ADS7843、TSC2046、TSC2003),對(duì)其性能進(jìn)行對(duì)比,如表1所示。

表1觸摸屏控制器芯片性能對(duì)比結(jié)果

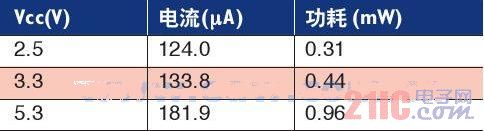

通過(guò)對(duì)ADC電路進(jìn)行優(yōu)化設(shè)計(jì),可使觸摸屏控制器的功耗不足1mW,低于表1中現(xiàn)有芯片的功耗。

因此本設(shè)計(jì)的側(cè)重點(diǎn)是在滿足工作電壓、工作溫度的基礎(chǔ)上,使ADC工作在睡眠/喚醒兩種工作模式下,以大大降低功耗。為了實(shí)現(xiàn)這一目的,芯片中設(shè)計(jì)了電壓基準(zhǔn)電路模塊,以控制ADC的開(kāi)啟和關(guān)閉。

電路設(shè)計(jì)與分析

ADC的整體結(jié)構(gòu)設(shè)計(jì)

SAR ADC包括采樣保持電路、比較器、DAC、逐次逼近寄存器、時(shí)序產(chǎn)生及數(shù)字控制邏輯電路。模擬輸入電壓(vin)由采樣/保持電路保持,N位SAR ADC需要N個(gè)比較周期,同時(shí)在當(dāng)前一位轉(zhuǎn)換完成之前不得進(jìn)入下一次轉(zhuǎn)換。因此該類ADC能夠有效節(jié)省功耗和空間,該結(jié)構(gòu)中DAC和比較器設(shè)計(jì)的好壞對(duì)整個(gè)ADC轉(zhuǎn)換精度起關(guān)鍵性的作用。

DAC的設(shè)計(jì)

DAC結(jié)構(gòu)設(shè)計(jì)

由于在CMOS集成電路中,制造電容比制造電阻更節(jié)省芯片面積,而且電容上沒(méi)有功率損耗,另外,開(kāi)關(guān)電容網(wǎng)絡(luò)可以完成采樣保持的功能,節(jié)省了單獨(dú)的采樣保持電路。因此,本文選擇采用開(kāi)關(guān)電容網(wǎng)絡(luò)構(gòu)成電荷按比例縮放式DAC。

電荷按比例縮放式DAC主要由按照二進(jìn)制加權(quán)排列的電容陣列組成。電容是CMOS工藝兼容的,而且相對(duì)精度高,所以電荷按比例縮放式DAC在CMOS工藝中容易實(shí)現(xiàn)。然而當(dāng)其精度提高時(shí),一方面所需的大電容導(dǎo)致芯片尺寸過(guò)大,而且大電容需要大充電電流,充電時(shí)間過(guò)長(zhǎng);另一方面最高權(quán)位和最低權(quán)位的電容比例變得很大,比值越大,電容匹配越差。所以高精度DAC通常由低精度DAC通過(guò)電容耦合來(lái)實(shí)現(xiàn)。這種耦合結(jié)構(gòu)成功的關(guān)鍵之一是確定耦合電容值。只有選擇合適的耦合電容值,才能保證各位間的權(quán)重關(guān)系,并實(shí)現(xiàn)D/A轉(zhuǎn)換,如圖1所示。

圖1 電荷按比例縮放式DAC組合的實(shí)現(xiàn)

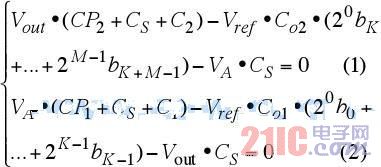

設(shè)圖1中A點(diǎn)到地的電容為CA,DAC的縮放通過(guò)電容CS實(shí)現(xiàn),CS和LSB陣列的串聯(lián)組合必須接于MSB陣列的左側(cè),因此可得:

版圖設(shè)計(jì)時(shí),為了消除介電松弛對(duì)轉(zhuǎn)換精度的影響,消除電荷擴(kuò)散和介電極化效應(yīng),減少噪聲干擾,電容上極板上會(huì)加靜電屏蔽層,并接地。為了消除襯底噪聲,將電容做在阱里,阱接地。電容陣列極板和屏蔽層或阱間形成的寄生電容,使電路中耦合電容兩極板地的寄生電容值增大,使得在確定耦合電容值時(shí),必須考慮寄生電容的影響。

DAC級(jí)間耦合電容值的優(yōu)化設(shè)計(jì)

圖1中CP1、CP2分別為A、B兩點(diǎn)到地的寄生電容。轉(zhuǎn)換過(guò)程中A、B電荷守恒,于是可得:

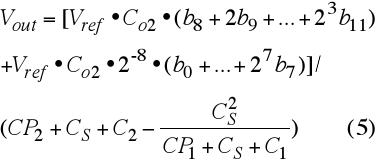

C1、C2分別為低權(quán)位和高權(quán)位子DAC的總?cè)葜?CO1和CO2分別是低權(quán)位和高權(quán)位子DAC的單位容值;K=8,M=4。解方程組,得到輸出電壓為:

由電路參數(shù)可知:C02=4C,C01=2-2C=2-4C02,所以:

以高權(quán)位DAC為基準(zhǔn),輸出應(yīng)有如下表達(dá)式:

比較式(4)和式(5),可得:

比較式(4)和式(5),可得:

分析耦合電容公式(6)可知,耦合電容大小與低權(quán)位寄生電容有關(guān),而與高權(quán)位寄生電容無(wú)關(guān)。高權(quán)位DAC的寄生電容不影響高低權(quán)位間的比例關(guān)系,只影響最終輸出電壓的絕對(duì)值。從輸出表達(dá)式(5)中可以看到,高權(quán)位寄生電容出現(xiàn)在分母中,它會(huì)使輸出絕對(duì)值變小,所以應(yīng)該盡量減小高權(quán)位寄生電容值。低權(quán)位寄生電容也會(huì)使輸出絕對(duì)值變小,但這個(gè)影響很小,和高權(quán)位寄生電容的影響相比,幾乎可以忽略不計(jì)。根據(jù)(6)式,低權(quán)位寄生電容出現(xiàn)在耦合電容表達(dá)式的分子上, 所以低權(quán)位寄生電容越大,耦合電容值也越大,通過(guò)增大耦合電容值就可以消除低權(quán)位寄生電容的影響。

寄生電容通常由電容極板和屏蔽層或阱形成,因此寄生容值和高低權(quán)位寄生電容大小有關(guān)系。所以,為了減小高權(quán)位寄生電容對(duì)輸出電壓的影響,在版圖設(shè)計(jì)時(shí),應(yīng)盡量減小寄生。

綜合考慮輸入電容要求及電容匹配精度后,選取做在N阱里的雙poly電容。單位電容取為400fF ,權(quán)位電容采用單位電容并聯(lián)結(jié)構(gòu),以提高匹配性。采取中心對(duì)稱布局,電容上覆蓋metal2作靜電屏蔽層;N阱和metal2均接地。寄生電容主要包括電容上極板和metal2之間、走線與metal2之間的寄生電容等。雖然高4位子DAC的寄生電容不影響權(quán)位間比例關(guān)系,但它會(huì)使輸出電壓值降低,以致需要更高精度的比較器。所以將覆蓋在高4位子DAC電容上的metal2開(kāi)孔,減小其寄生容值。

比較器的設(shè)計(jì)

由于DAC模塊采用的是開(kāi)關(guān)電容網(wǎng)絡(luò),在此將設(shè)計(jì)一個(gè)可消除直流失調(diào)電壓的開(kāi)關(guān)電容比較器。開(kāi)關(guān)電容比較器使用組合開(kāi)關(guān)電容和開(kāi)環(huán)比較器。它的優(yōu)點(diǎn)是,差分信號(hào)可用單端電路進(jìn)行比較,且可對(duì)開(kāi)環(huán)比較器直流失調(diào)電壓自動(dòng)校零。

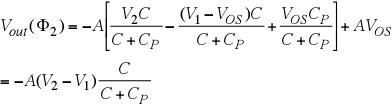

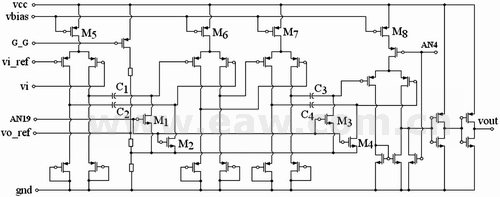

本文采用如圖2所示結(jié)構(gòu)設(shè)計(jì)SAR ADC中的開(kāi)關(guān)電容比較器。

圖2 開(kāi)關(guān)電容比較器電路圖

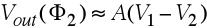

當(dāng)圖2中的開(kāi)關(guān)φ1關(guān)閉時(shí),輸入失調(diào)存儲(chǔ)在輸入串聯(lián)的電容C上,電容C將對(duì)比較器的輸入失調(diào)電壓VOS自動(dòng)校零。電容CP表示比較器輸入到地的寄生電容。在φ1相位周期結(jié)束時(shí),C和CP上的電壓為:

開(kāi)關(guān)φ2關(guān)閉時(shí),

如果CP小于C,那么上式可以簡(jiǎn)化如下:

因此電壓V1和V2的差值通過(guò)比較器的增益得到放大,后面的鎖存器根據(jù)比較器A的輸出產(chǎn)生邏輯電平,輸出Vout,直流輸入失調(diào)電壓自動(dòng)校零。

比較器A電路實(shí)現(xiàn)如圖3所示。

圖3 自消除失調(diào)電壓比較器電路實(shí)現(xiàn)方案

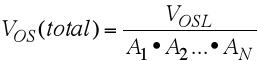

N級(jí)比較器的最終失調(diào)電壓可表示為:

其中A1~AN為各級(jí)的放大倍數(shù),VOSL為鎖存器的失調(diào)電壓。根據(jù)整個(gè)電路的增益要求和失調(diào)要求抑制的強(qiáng)度來(lái)取值,這里取N=4。

該比較器由三級(jí)差分放大器和一個(gè)輸出級(jí)組成,管子M1、M2、M3、M4在采樣期間導(dǎo)通,通過(guò)對(duì)電容C1、C2、C3、C4充電,對(duì)第二、三、四級(jí)差分放大器定靜態(tài)工作點(diǎn),管子M0~M4在比較轉(zhuǎn)換期間不導(dǎo)通。由于在采樣期間,各級(jí)差分輸入端都接靜態(tài)工作點(diǎn)電壓,相當(dāng)于交流地,失調(diào)電壓引起的輸出儲(chǔ)存在電容C1、C2、C3、C4上,比較時(shí)輸入電壓跟存儲(chǔ)在電容上的失調(diào)電壓串聯(lián)輸入,這樣可以使輸入端的失調(diào)電壓不被一級(jí)級(jí)放大輸出,從而減小失調(diào)的影響。輸出級(jí)由一個(gè)雙端變單端的差分放大器和兩個(gè)非門組成,其功能相當(dāng)于前述的鎖存器。

比較器的工作時(shí)鐘fCLK=2MHz,因此電流源提供的電流要相對(duì)大一些,管子M5、M6、M7、M8充當(dāng)電流源,由vbias控制開(kāi)關(guān),以確定電路的直流偏置。vbias是比較器電壓基準(zhǔn)電路的輸出。

電壓基準(zhǔn)電路的設(shè)計(jì)

由于比較器電路中電源電壓VCC的變化范圍為2.5V~5.3V,其變化范圍較大,因此對(duì)于比較器而言,使所有管子都處于飽和狀態(tài)的直流工作點(diǎn)并不多。當(dāng)電源電壓變化時(shí),希望得到穩(wěn)定的直流偏置電流,即要為圖3中偏置管M5、M6、M7、M8提供一個(gè)穩(wěn)定的基準(zhǔn)電壓。理想的基準(zhǔn)電流或電壓是與電源和溫度變化無(wú)關(guān)的,因此采用自舉基準(zhǔn)技術(shù),設(shè)計(jì)如圖4所示。

圖4 閥值基準(zhǔn)電路

圖4中管子M5、M6使得電流I1、I2相等。I1流經(jīng)管M3產(chǎn)生電壓VGS3,I2流過(guò)R產(chǎn)生電壓I2R。因?yàn)檫@兩個(gè)電壓連在一起,就確定出一個(gè)平衡點(diǎn),用Q表示。描述這個(gè)平衡點(diǎn)的方程式為:

因?yàn)镮1=I2=IQ,可以解出:

首先,I1和I2都不作為VCC函數(shù)而隨其改變,于是IQ對(duì)VCC的靈敏度基本為零,作用于一個(gè)電阻就得到一個(gè)基準(zhǔn)電壓。

但是,圖4中有兩個(gè)可能的平衡點(diǎn)。一個(gè)在Q,而另一個(gè)則在原點(diǎn)。為了避免電路選擇錯(cuò)誤的平衡點(diǎn),必須有一個(gè)啟動(dòng)電路。圖4中的虛線框內(nèi)即為啟動(dòng)電路。啟動(dòng)電路的開(kāi)啟和關(guān)閉由數(shù)字信號(hào)AN1和AN2控制,為了控制功耗,啟動(dòng)電路開(kāi)啟后會(huì)馬上關(guān)閉。

通過(guò)信號(hào)sel-y開(kāi)關(guān)控制比較器電路,即sel-y=1時(shí),比較器關(guān)閉,sel-y=0時(shí),比較器開(kāi)啟,使ADC工作在睡眠/喚醒兩種工作模式下,在沒(méi)有觸摸事件時(shí),直流功耗大幅度降低。

版圖實(shí)現(xiàn)及電路仿真分析

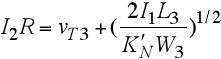

如圖5所示,版圖采用SMIC 2P2M 0.35μm CMOS工藝實(shí)現(xiàn),面積為1600x1700um2。

圖5 觸摸屏控制器版圖設(shè)計(jì)結(jié)果

采用Cadence環(huán)境下的Spectre和Spectre Verilog仿真工具進(jìn)行仿真。提取版圖寄生參數(shù),得到圖1中A、B點(diǎn)的寄生容值分別為212.11fF、278.53fF。根據(jù)式(6)可得優(yōu)化后的耦合電容值CS為1.72pF。

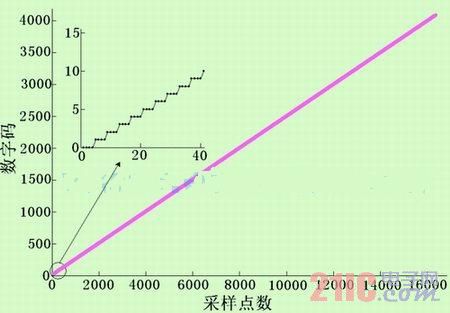

為了測(cè)量ADC的DNL和INL,給ADC加了斜波信號(hào)。可以從仿真圖中輸出數(shù)字碼的文本文件,利用該文件可以通過(guò)Matlab程序繪圖并計(jì)算其DNL和INL值。繪圖結(jié)果如圖6所示,經(jīng)計(jì)算DNL為1/4LSB,INL為-1LSB。

圖6 ADC全范圍仿真圖

從圖6中可見(jiàn),ADC輸出了4096個(gè)臺(tái)階,即完成了12位的A/D轉(zhuǎn)換。

對(duì)SAR ADC功耗進(jìn)行測(cè)試,測(cè)試結(jié)果如表2所示。

表2不同電壓下SAR ADC功耗測(cè)試結(jié)果

結(jié)語(yǔ)

通過(guò)對(duì)電荷按比例縮放式DAC組合結(jié)構(gòu)中寄生電容對(duì)耦合電容影響的分析,給出了耦合電容值的優(yōu)化設(shè)計(jì)方法,通過(guò)開(kāi)關(guān)電容比較器結(jié)構(gòu),消除了比較器的失調(diào)電壓。優(yōu)化后的SAR ADC電路滿足二進(jìn)制權(quán)重關(guān)系,轉(zhuǎn)換結(jié)果達(dá)到了12位的轉(zhuǎn)換精度。并且成功利用電壓基準(zhǔn)電路模塊,使ADC工作在睡眠/喚醒兩種工作模式下,電路功耗大大降低。在時(shí)鐘頻率為2MHz情況下測(cè)試,SAR ADC功耗小于1mW。結(jié)果表明,本文設(shè)計(jì)的基于觸摸屏控制器的SAR ADC電路功耗低并具有較高精度,可以應(yīng)用在任何中等精度、中等轉(zhuǎn)換速率的場(chǎng)合,并且對(duì)觸摸屏控制器的優(yōu)化設(shè)計(jì)具有很好的指導(dǎo)作用。