RS-485標(biāo)準(zhǔn)在工業(yè)控制、電力通訊、智能儀表等領(lǐng)域中使用廣泛。但是,在工業(yè)控制等現(xiàn)場環(huán)境中,情況復(fù)雜,常會(huì)有電氣噪聲干擾傳輸線路;在多系統(tǒng)互聯(lián)時(shí),不同系統(tǒng)的地之間會(huì)存在電位差,形成接地環(huán)路,會(huì)干擾整個(gè)系統(tǒng),嚴(yán)重時(shí)會(huì)造成系統(tǒng)的災(zāi)難性損毀;還可能存在損壞設(shè)備或危害人員的潛在電流浪涌等高電壓或大電流。因此,對RS-485接口的隔離是非常有必要的。

ADM2483是一款集成了信號通道隔離和RS-485收發(fā)器的芯片。以單芯片實(shí)現(xiàn)了對RS-485接口的隔離,電路連接簡單,設(shè)計(jì)方便,性能上遠(yuǎn)高于繁瑣的光耦隔離485電路設(shè)計(jì)。在某些系統(tǒng)應(yīng)用中,由于I/O口數(shù)量有限,因此我們希望半雙工的RS-485收發(fā)器能夠?qū)崿F(xiàn)自收發(fā)功能,以節(jié)省用于控制RE與DE的兩路I/O端口。目前,實(shí)現(xiàn)這一功能的主流方案是采用74HC14芯片。下面,我們采用74HC14與ADM2483實(shí)現(xiàn)RS-485接口的信號隔離自收發(fā)設(shè)計(jì)。

硬件電路

隔離RS-485接口電路

之前我們經(jīng)常采用的485接口隔離電路是利用三個(gè)光耦隔離收發(fā)及控制信號,加上485收發(fā)器共需要4片IC,且采用光耦隔離需要限流及輸出上拉電阻,必要時(shí)還會(huì)使用三極管驅(qū)動(dòng)。設(shè)計(jì)電路繁瑣,耗費(fèi)時(shí)間長,如果沒有之前使用光耦的經(jīng)驗(yàn),那么在選用光耦限流及輸出上拉電阻方面會(huì)耗費(fèi)很多不必要的時(shí)間;且光耦的輸出信號上升時(shí)間較長,在與數(shù)字I/O端口相接時(shí),需另加施密特整形才能保證信號的波形符合標(biāo)準(zhǔn),如在FPGA、DSP等系統(tǒng)中的應(yīng)用。

ADM2483是內(nèi)部集成了磁隔離通道和485收發(fā)器的芯片,內(nèi)部集成的磁隔離通道原理與光耦不同,在輸入輸出端分別有編碼解碼電路和施密特整形電路,確保了輸出波形的質(zhì)量。且磁隔離功耗僅為光耦的1/10,傳輸延時(shí)為ns級,從直流到高速信號的傳輸都具有超越光耦的性能優(yōu)勢。內(nèi)部集成的低功耗485收發(fā)器,信號傳輸速率可達(dá)500Kbps,后端總線可支持掛載256個(gè)節(jié)點(diǎn)。具有真失效保護(hù)、電源監(jiān)控以及熱關(guān)斷功能。

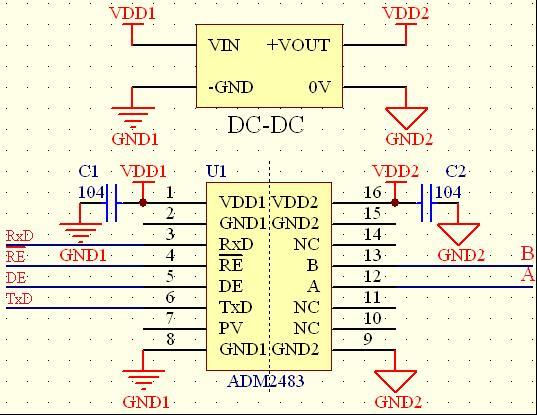

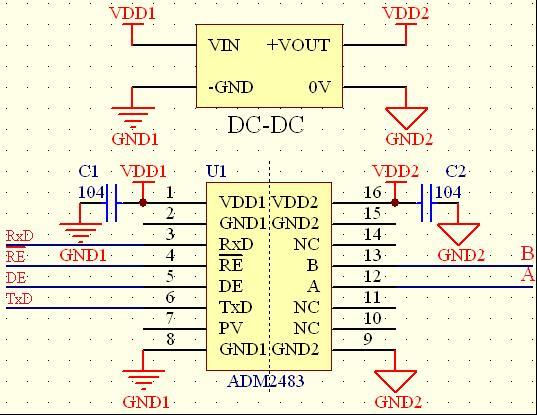

要實(shí)現(xiàn)隔離RS-485接口的電路設(shè)計(jì)只需在ADM2483的電源與地之間接一個(gè)104的去耦電容即可。當(dāng)然,DC-DC隔離電源是必不可少的。其電路連接如下圖:

RS-485標(biāo)準(zhǔn)在工業(yè)控制、電力通訊、智能儀表等領(lǐng)域中使用廣泛。但是,在工業(yè)控制等現(xiàn)場環(huán)境中,情況復(fù)雜,常會(huì)有電氣噪聲干擾傳輸線路;在多系統(tǒng)互聯(lián)時(shí),不同系統(tǒng)的地之間會(huì)存在電位差,形成接地環(huán)路,會(huì)干擾整個(gè)系統(tǒng),嚴(yán)重時(shí)會(huì)造成系統(tǒng)的災(zāi)難性損毀;還可能存在損壞設(shè)備或危害人員的潛在電流浪涌等高電壓或大電流。因此,對RS-485接口的隔離是非常有必要的。

ADM2483是一款集成了信號通道隔離和RS-485收發(fā)器的芯片。以單芯片實(shí)現(xiàn)了對RS-485接口的隔離,電路連接簡單,設(shè)計(jì)方便,性能上遠(yuǎn)高于繁瑣的光耦隔離485電路設(shè)計(jì)。在某些系統(tǒng)應(yīng)用中,由于I/O口數(shù)量有限,因此我們希望半雙工的RS-485收發(fā)器能夠?qū)崿F(xiàn)自收發(fā)功能,以節(jié)省用于控制RE與DE的兩路I/O端口。目前,實(shí)現(xiàn)這一功能的主流方案是采用74HC14芯片。下面,我們采用74HC14與ADM2483實(shí)現(xiàn)RS-485接口的信號隔離自收發(fā)設(shè)計(jì)。

硬件電路

隔離RS-485接口電路

之前我們經(jīng)常采用的485接口隔離電路是利用三個(gè)光耦隔離收發(fā)及控制信號,加上485收發(fā)器共需要4片IC,且采用光耦隔離需要限流及輸出上拉電阻,必要時(shí)還會(huì)使用三極管驅(qū)動(dòng)。設(shè)計(jì)電路繁瑣,耗費(fèi)時(shí)間長,如果沒有之前使用光耦的經(jīng)驗(yàn),那么在選用光耦限流及輸出上拉電阻方面會(huì)耗費(fèi)很多不必要的時(shí)間;且光耦的輸出信號上升時(shí)間較長,在與數(shù)字I/O端口相接時(shí),需另加施密特整形才能保證信號的波形符合標(biāo)準(zhǔn),如在FPGA、DSP等系統(tǒng)中的應(yīng)用。

ADM2483是內(nèi)部集成了磁隔離通道和485收發(fā)器的芯片,內(nèi)部集成的磁隔離通道原理與光耦不同,在輸入輸出端分別有編碼解碼電路和施密特整形電路,確保了輸出波形的質(zhì)量。且磁隔離功耗僅為光耦的1/10,傳輸延時(shí)為ns級,從直流到高速信號的傳輸都具有超越光耦的性能優(yōu)勢。內(nèi)部集成的低功耗485收發(fā)器,信號傳輸速率可達(dá)500Kbps,后端總線可支持掛載256個(gè)節(jié)點(diǎn)。具有真失效保護(hù)、電源監(jiān)控以及熱關(guān)斷功能。

要實(shí)現(xiàn)隔離RS-485接口的電路設(shè)計(jì)只需在ADM2483的電源與地之間接一個(gè)104的去耦電容即可。當(dāng)然,DC-DC隔離電源是必不可少的。其電路連接如下圖:

信號自收發(fā)電路

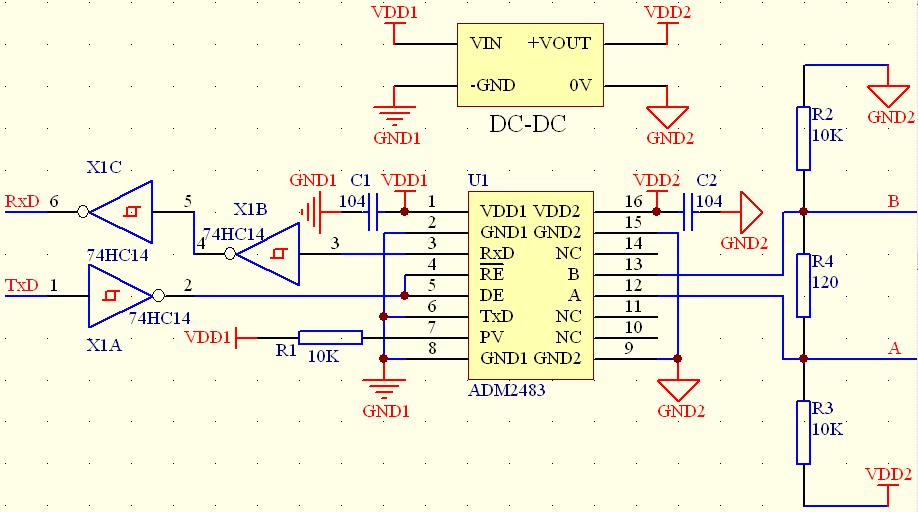

信號自收發(fā)電路我們采用74HC14芯片,利用它的施密特波形翻轉(zhuǎn)性能來控制RE、DE引腳,以實(shí)現(xiàn)信號的自收發(fā)。其電路連接如下圖:

如圖所示,MCU的發(fā)送信號經(jīng)過施密特觸發(fā)器反向后輸給DE和RE腳,發(fā)送數(shù)據(jù)引腳TxD接地。

當(dāng)有高電平信號發(fā)送時(shí),經(jīng)反向變?yōu)榈碗娖叫盘枺珼E/RE引腳輸入為低電平,使發(fā)送驅(qū)動(dòng)器禁止,總線為高阻狀態(tài),此時(shí)由A、B總線上的上拉電阻產(chǎn)生高電平輸出。

當(dāng)有低電平信號發(fā)送時(shí),經(jīng)反向變?yōu)楦唠娖叫盘枺珼E/RE引腳輸入為高電平,使發(fā)送驅(qū)動(dòng)器工作,由于TxD引腳端接地,為低電平,這樣就將低電平發(fā)送至總線。

本參考設(shè)計(jì)僅為實(shí)現(xiàn)RS-485接口的自收發(fā)功能,在實(shí)際應(yīng)用中,應(yīng)根據(jù)使用情況作出相應(yīng)的修改。此收發(fā)電路也有不足之處,當(dāng)在連續(xù)發(fā)送高電平時(shí),ADM2483的DE/RE引腳處于接收狀態(tài),所以,此時(shí)的發(fā)送端和接收端都處于接收狀態(tài),這時(shí)的總線是空閑狀態(tài),是允許各節(jié)點(diǎn)發(fā)送數(shù)據(jù)的,因此一般在主從式的網(wǎng)絡(luò)結(jié)構(gòu)中采用此方法。

在網(wǎng)絡(luò)上也有不同的幾種實(shí)現(xiàn)RS-485收發(fā)器自收發(fā)的方案,分別有以下幾種:

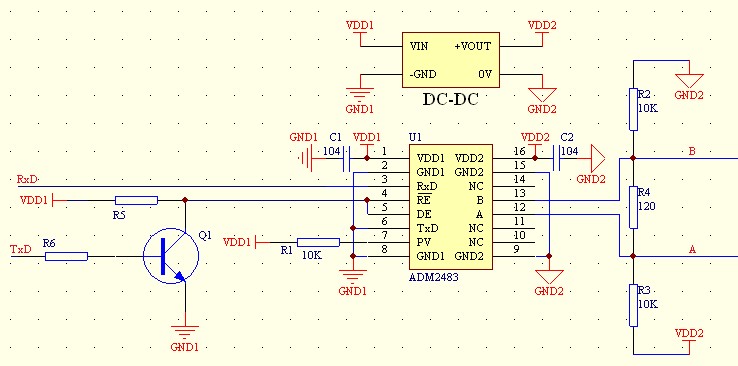

利用三極管反向原理實(shí)現(xiàn)

電路如下圖:

當(dāng)不發(fā)送數(shù)據(jù)時(shí),TxD信號為高電平,經(jīng)V1反向后使ADM2483處于接收狀態(tài)。

當(dāng)發(fā)送數(shù)據(jù)時(shí),TxD為高時(shí),經(jīng)V1反向,使發(fā)送驅(qū)動(dòng)器禁止,總線為高阻狀態(tài),此時(shí)由A、B總線上的上拉電阻產(chǎn)生高電平輸出。TxD為低時(shí),經(jīng)V1反向,使發(fā)送驅(qū)動(dòng)器工作,由于TxD引腳端接地,為低電平,這樣就將低電平發(fā)送至總線。

采用這種電路時(shí),需要程序保證不同時(shí)進(jìn)行接收和發(fā)送的操作。

利用555定時(shí)器,其原理于以上電路類似,電路圖如下:

555定時(shí)器為邊沿觸發(fā),當(dāng)TxD發(fā)送高電平時(shí),555定時(shí)器OUT引腳輸出低電平,當(dāng)TxD發(fā)送低電平時(shí),555定時(shí)器OUT引腳輸出高電平,當(dāng)TxD轉(zhuǎn)為高電平時(shí),OUT引腳輸出的高電平狀態(tài)會(huì)延遲一會(huì)再轉(zhuǎn)入低電平,以確保發(fā)送數(shù)據(jù)的正確性。

采用74HC14和RC電路實(shí)現(xiàn),此電路是對單純使用74HC14實(shí)現(xiàn)自收發(fā)電路的改進(jìn),增加了RC充放電電路,減少總線處于空閑狀態(tài)的時(shí)間,電路如下圖:

當(dāng)TxD信號為高電平,則通過電阻為電容充電,其充電時(shí)間為T,該時(shí)間應(yīng)設(shè)置為串口發(fā)送一個(gè)字節(jié)所需要的時(shí)間,由R,C參數(shù)來確定。當(dāng)電容充滿后,則DE/RE為低電平,使ADM2483處于接收狀態(tài)。

在發(fā)送數(shù)據(jù)時(shí),TxD起始位產(chǎn)生第一個(gè)下降沿,使電容經(jīng)過二極管進(jìn)行快速放電,使DE/RE很快變?yōu)楦唠娖剑珹DM2483處于發(fā)送狀態(tài)。在發(fā)送過程中, 當(dāng)TxD變成高電平時(shí),電容通過電阻緩慢充電,使DE/RE仍然保持在發(fā)送狀態(tài),可有效吸收總線上的反射信號。當(dāng)RC充電結(jié)束,使DE/RE轉(zhuǎn)入接受狀態(tài)時(shí), 總線上的上拉、下拉電阻將維持TxD高電平的發(fā)送狀態(tài),直至整個(gè)bit發(fā)送結(jié)束。

當(dāng)數(shù)據(jù)發(fā)送完畢以后,TxD變?yōu)楦唠娖剑琑C又開始充電,即經(jīng)T時(shí)間后,ADM2483又轉(zhuǎn)換為接收狀態(tài)。

聲明

以上所有電路均為參考電路,為電路設(shè)計(jì)者提供思路,在實(shí)際使用中請?jiān)俅悟?yàn)證,以確保電路的穩(wěn)定及不會(huì)對系統(tǒng)造成破壞。對于電路損壞造成的損失,概不負(fù)責(zé)。