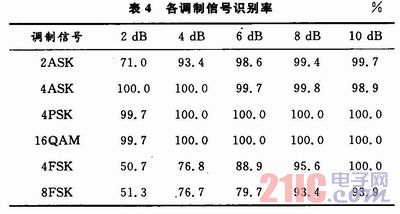

摘要:基于高階累積量的數(shù)字調(diào)制信號(hào)識(shí)別算法在低信噪比環(huán)境下識(shí)別率較低,。針對(duì)這一問(wèn)題,提出了高階累積量的改進(jìn)算法,,通過(guò)調(diào)整特征參數(shù)的判別順序先識(shí)別出MASK信號(hào)的方式,,取得了較好的效果。討論了該算法的FPGA設(shè)計(jì),,并利用Virtex-4開(kāi)發(fā)板對(duì)該設(shè)計(jì)進(jìn)行硬件協(xié)同仿真測(cè)試,。測(cè)試結(jié)果表明,該算法在低信噪比環(huán)境下對(duì)2ASK,,4ASK,,4PSK,16QAM信號(hào)的識(shí)別率有顯著提高,。在信噪比為4dB時(shí),,對(duì)2ASK,4A-SK信號(hào)的識(shí)別率分別為93.4%,,100%,。在信噪比為2 dB時(shí),對(duì)4PSK,,16QAM信號(hào)的識(shí)別率最高,,達(dá)到了99.7%。

關(guān)鍵詞:System Generator,;FPGA,;調(diào)制識(shí)別,;高階累積量

0 引言

由于數(shù)字調(diào)制信號(hào)越來(lái)越多地應(yīng)用于通信信號(hào)處理領(lǐng)域,因此對(duì)數(shù)字信號(hào)調(diào)制識(shí)別的研究也越來(lái)越多,。傳統(tǒng)的調(diào)制識(shí)別的判決方法有:決策判決法,、高階累積量算法和人工神經(jīng)網(wǎng)絡(luò)算法等。但是決策判決法在低信噪比環(huán)境中識(shí)別率不高,,而基于人工神經(jīng)網(wǎng)絡(luò)的識(shí)別方法計(jì)算復(fù)雜度較高,。信號(hào)的高階累積量算法具有很好的抗噪性能,故對(duì)基于高階累積量的通信信號(hào)調(diào)制識(shí)別算法的研究受到了廣泛重視,。文獻(xiàn)利用高階累積量實(shí)現(xiàn)了對(duì) 2ASK/BPSK,,4ASK,4PSK,,2FSK,,4FSK信號(hào)的分類(lèi)。文獻(xiàn)利用四階和六階累積量實(shí)現(xiàn)了對(duì) 2ASK,,4ASK,,8ASK,QPSK,,8P-SK,,16QAM信號(hào)的分類(lèi)。文獻(xiàn)利用二,、四,、六階累積量實(shí)現(xiàn)了對(duì) 2ASK/BPSK,4ASK,,QPSK,,2FSK,4FSK,,8FSK,,16QAM信號(hào)的分類(lèi)。文獻(xiàn)對(duì)高階累積量的四階,、五階累積量進(jìn)行了優(yōu)化和仿真,,但是在低信噪比的環(huán)境下,對(duì)信號(hào)的識(shí)別率都不高,。

在尋找更優(yōu)識(shí)別算法的過(guò)程中,,以往的研究更多的把注意力放在了識(shí)別算法上,而沒(méi)注重算法的硬件設(shè)計(jì)與實(shí)現(xiàn),。System Generator for DSP是Xilinx公司開(kāi)發(fā)的一款理想的DSP開(kāi)發(fā)軟件,,它對(duì)數(shù)字信號(hào)處理單元進(jìn)行系統(tǒng)建模,并將模型轉(zhuǎn)換成可靠的硬件實(shí)現(xiàn),是連接數(shù)字信號(hào)處理高層系統(tǒng)設(shè)計(jì)與Xilinx FPGA實(shí)現(xiàn)的橋梁,。針對(duì)上述問(wèn)題,,本文提出了高階累積量的改進(jìn)算法,并在System Generator中實(shí)現(xiàn)了算法的FPGA設(shè)計(jì),。

1 高階累積量的改進(jìn)算法

數(shù)字信號(hào)的調(diào)制識(shí)別通常經(jīng)過(guò)三個(gè)步驟:接收信號(hào)預(yù)處理,、特征參數(shù)提取和調(diào)制方式識(shí)別。然而實(shí)現(xiàn)信號(hào)調(diào)制識(shí)別的關(guān)鍵環(huán)節(jié)是從接收信號(hào)中提取出用于識(shí)別的特征參數(shù),。下面首先介紹高階累積量算法是如何提取用于調(diào)制識(shí)別的特征參數(shù)的,。

1.1 特征參數(shù)的提取

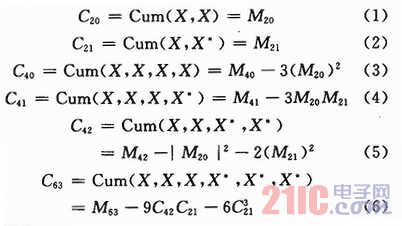

首先給出高階矩的定義,對(duì)于一個(gè)具有零均值的復(fù)隨機(jī)過(guò)程X(t),,其p階混合矩可表示為:Mpq=E[X(t)p-qX*(t)q],。其中,*表示函數(shù)的共軛,。然后定義高階累積量如下:

設(shè)信號(hào)的能量為E,利用文獻(xiàn)中提出的算術(shù)平均來(lái)代替統(tǒng)計(jì)平均的方法,,計(jì)算各種數(shù)字調(diào)制信號(hào)的高階累積量,,得到高階累積量的理論值,如表1所示,。

從表1中可以看出,,從信號(hào)的高階累積量中提取特征參數(shù),可以實(shí)現(xiàn)大部分信號(hào)的分類(lèi),,而由于2ASK和BPSK信號(hào)的各累積量值相同,,故利用高階累積量無(wú)法實(shí)現(xiàn)其分類(lèi)。MFSK的高階累積量也相同,,直接利用累積量無(wú)法實(shí)現(xiàn)其類(lèi)內(nèi)識(shí)別,。

由文獻(xiàn)知,對(duì)MFSK信號(hào)求導(dǎo),,再經(jīng)中值濾波,,在濾除含有沖激函數(shù)的項(xiàng)后,再計(jì)算所得信號(hào)的高階累積量值,,如表2所示,。

由以上分析可知,為了實(shí)現(xiàn)數(shù)字調(diào)制信號(hào)的調(diào)制識(shí)別,,利用不同的累積量組合,,從中提取了以下4個(gè)特征參數(shù),定義如下:

1.2 信號(hào)的調(diào)制識(shí)別流程

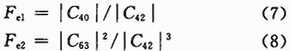

在低信噪比環(huán)境中,,基于高階累積量的數(shù)字調(diào)制信號(hào)識(shí)別算法對(duì)2ASK和4ASK信號(hào)的識(shí)別率普遍較低,。針對(duì)此問(wèn)題,本文提出了高階累積量的改進(jìn)算法。文中在高階累積量算法的基礎(chǔ)上,,對(duì)四個(gè)特征參數(shù)的判決順序稍作調(diào)整,,將MASK信號(hào)與其他信號(hào)分離,取得了較好的效果,。具體識(shí)別過(guò)程如下:

(1)用編程工具編程產(chǎn)生各種數(shù)字調(diào)制信號(hào),,并加入信噪比已知的噪聲,作為待識(shí)別的信號(hào),。

(2)將接收到的待識(shí)別信號(hào)通過(guò)下變頻直接變換到零頻,,然后利用正交下變頻技術(shù)得到復(fù)基帶調(diào)制信號(hào)。

(3)計(jì)算各種待識(shí)別信號(hào)的二,、四,、六階累積量,并計(jì)算其特征參數(shù)Fe1,,F(xiàn)e2,,T4。

(4)利用特征參數(shù)T4的識(shí)別,,可以將信號(hào)分為兩組:第一組為MASK信號(hào),,第二組為MPSK,16QAM,,MFSK信號(hào),。利用Fe2的閾值(t1)實(shí)現(xiàn)

第一組組內(nèi)識(shí)別;再利用Fe2的另一個(gè)閾值(t2)和Fe1從第二組中識(shí)別出16QAM,,MPSK信號(hào),。

(5)將待識(shí)別信號(hào)進(jìn)行微分后再經(jīng)中值濾波器,計(jì)算變換信號(hào)的高階累積量,,并計(jì)算特征參數(shù)Fe3,,利用Fe2實(shí)現(xiàn)MFSK類(lèi)內(nèi)識(shí)別。

在信號(hào)的調(diào)制識(shí)別過(guò)程中,,主要是根據(jù)決策樹(shù)方法進(jìn)行分類(lèi)和識(shí)別,。本文在提取上述四個(gè)特征參數(shù)的基礎(chǔ)上,根據(jù)不同的決策規(guī)則建立決策樹(shù),。經(jīng)過(guò)多次性能的仿真和比較,,最終得到一種比較好的識(shí)別算法,如圖1所示,。其中t0,,t1,t2,,t3,,t4都是閾值,。

1.3 仿真結(jié)果

文中采用高階累積量的改進(jìn)方法,對(duì)算法識(shí)別性能做蒙特卡洛仿真,。給閾值t0,,t1,t2,,t3,,t4設(shè)置合適的值后,再將1 000次獨(dú)立實(shí)驗(yàn)得到的仿真結(jié)果取平均,。在每次試驗(yàn)中,,設(shè)置信號(hào)的載波頻率為12 kHz,碼元速率為1 200 b/s,,其中4FSK,,8FSK的頻偏分別為1.5 kHz,3.5 kHz,,碼元個(gè)數(shù)為200,。圖2為原算法仿真結(jié)果,圖3為本文算法的仿真結(jié)果,。

對(duì)圖2和圖3進(jìn)行比較,,可以看出本文算法的識(shí)別效果有了顯著提高。在信噪比為2 dB時(shí),,本文算法對(duì)16QAM信號(hào)和4PSK信號(hào)識(shí)別率達(dá)到100%,,而原算法幾乎不能識(shí)別16QAM信號(hào),;在信噪比為4 dB時(shí),,對(duì)2ASK,4ASK信號(hào)的識(shí)別率分別為93%,,100%,。在信噪比為8 dB時(shí),所有信號(hào)的識(shí)別率都可以達(dá)到90%以上,,原算法有的信號(hào)識(shí)別率低于90%,。比較后可知,在低信噪比環(huán)境下本文的算法對(duì)2ASK,,4ASK,,4PSK,16QAM信號(hào)的識(shí)別率有了顯著提高,。

2 算法的System Generator設(shè)計(jì)

目前,,F(xiàn)PGA芯片已成為數(shù)字信號(hào)處理系統(tǒng)的核心器件。由于DSP設(shè)計(jì)者通常對(duì)C語(yǔ)言或Matlab工具很熟悉,,卻不了解硬件描述語(yǔ)言VHDL,,使得FPGA并未在數(shù)字信號(hào)處理領(lǐng)域獲得廣泛應(yīng)用。System Generator在很多方面擴(kuò)展了MathWorks公司的Simulink平臺(tái),提供了適合硬件設(shè)計(jì)的數(shù)字信號(hào)處理建模環(huán)境,,加速,、簡(jiǎn)化了FPGA的DSP系統(tǒng)級(jí)硬件設(shè)計(jì)。通過(guò)Simulink的設(shè)計(jì),,System Generator即可自動(dòng)完成硬件比特流的產(chǎn)生,,從而高效的實(shí)現(xiàn)FPGA設(shè)計(jì)。

在FPGA調(diào)試和開(kāi)發(fā)過(guò)程中,,采用Xilinx公司的系統(tǒng)級(jí)建模工具System Generator構(gòu)建信號(hào)調(diào)制識(shí)別的算法模塊,,開(kāi)發(fā)板選用Virtex-4。算法模塊主要由信號(hào)產(chǎn)生模塊,,信號(hào)參數(shù)提取模塊和信號(hào)判決模塊構(gòu)成,。

2.1 調(diào)制信號(hào)的產(chǎn)生

在System Generator設(shè)計(jì)過(guò)程中,各種調(diào)制信號(hào)是利用Matlab語(yǔ)言編程提供的,,并疊加上已知信噪比的高斯白噪聲,。文中測(cè)試了2ASK,4ASK,,4PSK,,16QAM,4FSK和8FSK信號(hào)的識(shí)別率,。

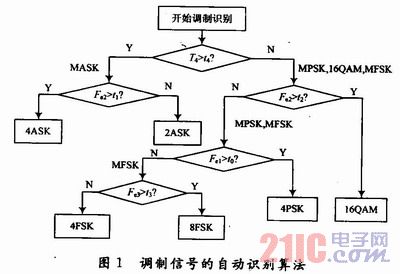

2.2 微分前參數(shù)提取模塊

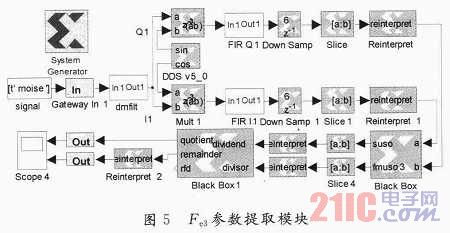

提取特征參數(shù)Fe1,,F(xiàn)e2,T4的模塊,,如圖4所示,。其中,signal是信號(hào)源,,DDS,,F(xiàn)IR,DowSamp共同實(shí)現(xiàn)復(fù)基帶信號(hào)的同向分量和正交分量的提取,,calculatmodule是計(jì)算Fe1,,F(xiàn)e2,T4三個(gè)特征參數(shù)的模塊,,且這三個(gè)特征參數(shù)的結(jié)果分別由三個(gè)示波器輸出,。

2.3 微分后參數(shù)提取模塊

提取特征參數(shù)Fe3的模塊,如圖5所示,。其中,,dmfilt是微分中值濾波模塊,兩個(gè)Black Box是計(jì)算特征參數(shù)Fe3的模塊,。待識(shí)別調(diào)制信號(hào)經(jīng)過(guò)dmfilt模塊后,,然后由DDS,,F(xiàn)IR,DowSamp等提取同向分量和正交分量,,再通過(guò)計(jì)算Fe3的模塊計(jì)算參數(shù),,最后結(jié)果由Scope輸出。

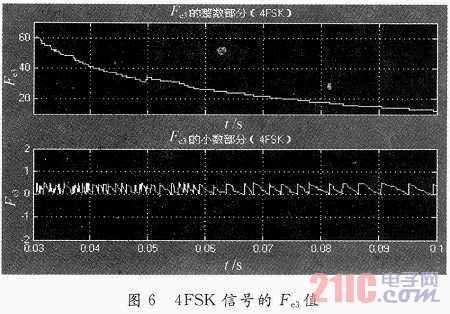

圖6是當(dāng)信號(hào)為4FSK時(shí),,計(jì)算得到的Fe3值,。其中,O.03~O.1 s是模塊計(jì)算參數(shù)的過(guò)程,,O.1 s時(shí)對(duì)應(yīng)的數(shù)據(jù)是計(jì)算的最終結(jié)果,。將結(jié)果輸出到Matlab變量空間workspace中,可以得到在0.1 s時(shí)計(jì)算的Fe3值為12.4,。

3 實(shí)驗(yàn)結(jié)果

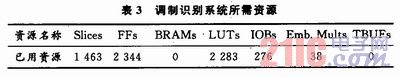

為了驗(yàn)證調(diào)制識(shí)別系統(tǒng)的可行性,,分別在Simulink和目標(biāo)開(kāi)發(fā)板上運(yùn)行該設(shè)計(jì)。在產(chǎn)生硬件協(xié)同仿真模塊之前,,先調(diào)用Resource Esti-mator模塊對(duì)本系統(tǒng)所需資源進(jìn)行估測(cè),。估測(cè)結(jié)果見(jiàn)表3。

由于所需芯片內(nèi)部資源較多,,所以選用Virtex4-xc4vlx200芯片,。然后在System Generator模塊中點(diǎn)擊Generate產(chǎn)生硬件協(xié)仿真模塊,并將它拖入到設(shè)計(jì)文件當(dāng)中,。給Virtex-4目標(biāo)板上電,,連接好JTAG口,啟動(dòng)硬件協(xié)同仿真,。當(dāng)信號(hào)分別為2ASK,,4ASK,4PSK等調(diào)制信號(hào)時(shí),,測(cè)試整個(gè)設(shè)計(jì)系統(tǒng)判決的結(jié)果,,并將1 000次獨(dú)立試驗(yàn)得到的仿真結(jié)果取平均,,得到各種調(diào)制信號(hào)的識(shí)別率,,如表4所示。從試驗(yàn)結(jié)果來(lái)看,,調(diào)制識(shí)別系統(tǒng)設(shè)計(jì)的FPGA硬件協(xié)同實(shí)現(xiàn)與Simulink仿真的結(jié)果基本一致,,達(dá)到了設(shè)計(jì)的要求,從而也說(shuō)明了System Generator有很高的精度,。

4 結(jié)語(yǔ)

本文采用高階累積量改進(jìn)算法對(duì)各種數(shù)字信號(hào)進(jìn)行調(diào)制識(shí)別,,大大提高了低信噪比環(huán)境下2ASK,4ASK,,4PSK和16QAM信號(hào)的識(shí)別率,,并在 System Generator中實(shí)現(xiàn)了高階累積量改進(jìn)算法的FPGA設(shè)計(jì),,從模型的建立到FPGA的實(shí)現(xiàn)都是在圖形化設(shè)計(jì)環(huán)境下完成的,避開(kāi)了編寫(xiě)復(fù)雜VHDL語(yǔ)言的環(huán)節(jié),,且轉(zhuǎn)化到FPGA上實(shí)現(xiàn)的性能好,,設(shè)計(jì)過(guò)程簡(jiǎn)便靈活,從而為調(diào)制方式識(shí)別算法的設(shè)計(jì)提供了一種新的方案,。利用System Generator提供的圖形化建模環(huán)境和自動(dòng)轉(zhuǎn)換成VHDL代碼的能力,,設(shè)計(jì)者可以將更多的時(shí)間和精力放在算法的優(yōu)化上,同時(shí)又能顯著縮短設(shè)計(jì)開(kāi)發(fā)周期,。