簡介

基于微處理器的器件需要使用穩(wěn)壓電源(PSU)以檢測輸入功率損耗和繼續(xù)在完成內存?zhèn)浞?即將關鍵數據寫入非易失性存儲器)的時間內進行供電。

設計連續(xù)輸出功率的一種方法是:生成較高的輸出電壓和使用線性穩(wěn)壓器生成所需的較低電壓。線性穩(wěn)壓器輸入端電容用于提供維持時間。但遺憾的是,這種方法會降低電源的整體效率,原因是它需要使用次級線性穩(wěn)壓器,進而需要更大的變壓器和元件,使得電源電路初級側的額定功率更高。

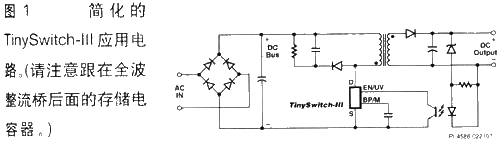

另一種解決方案是使用已知的導通時間延長技術,這種方法在Power Integrations(PI)的一系列離線式開關IC中得到采用。在PI芯片中,導通時間延長功能與開/關控制功能相結合,用來提供穩(wěn)壓。這兩種技術都可以替代傳統(tǒng)的脈寬調制(PWM)控制,而無需添加額外的電路,如圖1所示。

內存?zhèn)浞莨β室?/strong>

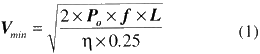

需要在關斷之前存儲關鍵數據的產品應用通常會使用EEPROM內存,并需要獲得穩(wěn)壓電源電壓,以便在完成內存寫周期的時間持續(xù)供電。對于某些EEPROM內存而言,寫周期時間可能長達10 ms。為了提供足夠的寫周期時間,標準的做法是:通過關閉所有外設和不必要的額外負載來降低斷電序列條件下的功耗。圖2顯示了直流總線電壓和斷電序列的關系,從而可以有效利用儲存在輸入直流總線端濾波電容中的能量。

功率轉換器階段需要使用儲存于輸入濾波電容中的能量,以便將輸出電壓維持在穩(wěn)壓限制范圍之內。在圖2中,這代表著直流總線電壓從Vmin2降到Vmin3及進行數據備份所需要維持的一段時間(檢測到輸入失敗情況后)。

對于大多數低功率應用而言,反激式轉換器因為具有成本低、元件數量少和在通用輸入應用中易于設計等優(yōu)勢,而成為一種可選的拓撲結構。我們將用兩個反激式轉換器進行比較,來說明導通時間延長技術的效率及其對電容選擇的影響:一個反激式轉換器在非連續(xù)導通模式工作一固定頻率技術(DCMFF),而另一個則利用導通時間延長來實施非連續(xù)導通模式-占空比擴展技術(DCMDE)。

輸入電壓下降時的功率輸出

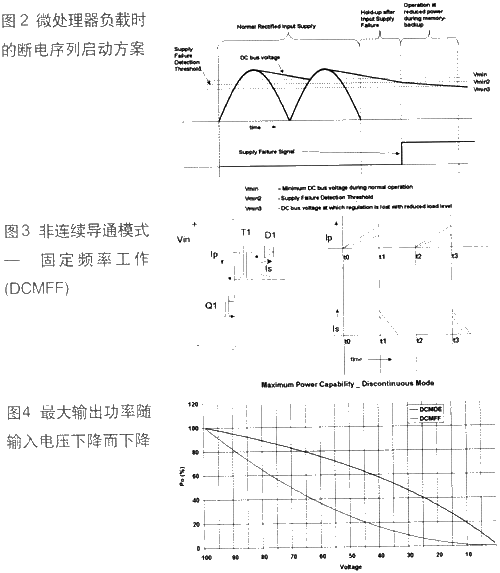

案例1:DCMFF-最大占空比為50%。在本例中,我們將針對工作頻率為100kHz并使用了一個500μH初級電感的21.25W([email protected])電源設計,對最大占空比為50%的DCMFF轉換階段的功率輸出能力進行測評(參見圖3)。假設能效為84%。

此設計的Vmim為100V。當直流總線電壓為100V時,如果所連負載等于滿載(即21.25W),則占空比將達到最大值。

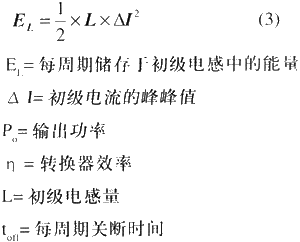

對于最大占空比為50%的DCMFF設計,最大輸出功率與直流總線電壓之間的關系如公式(1)所示。

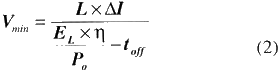

圖4顯示,電路的最大功率能力將隨著電壓的下降而下降,對于為50%滿載的負載,電路可以維持輸出端穩(wěn)壓,使直流總線電壓僅下降到69V。

案例2:DCMDE-導通時間延長而不改變關斷時間可以自動擴展占空比。要使導通時間延長方法與固定頻率DCMFF方法進行可行性對比,需要將Vmin=100V下的占空比假設為50%。其結果是,電路在100V直流輸入電壓下輸出滿載功率時的初級電感值相同,以及高于100VDC的直流總線電壓具有相同的工作條件。

電路工作情況:電路的工作情況與DCMFF配置相同,直到直流輸入電壓降到與Vmim相等的值。隨著輸入電壓降到Vmin以下,t0-t1的時間間隔將被延長,直到初級電流達到預定的峰值初級電流值,后者等于輸入電壓為Vmin(占空比為50%)時的預計值。t1到t2的時間間隔保持不變,且等于正常工作條件下開關頻率的時間間隔的一半。

圖5顯示了輸入電壓下降時初級繞組電流波形的變化。由于電感電流斜率隨著輸入電壓的降低而降低,因此初級電流達到所需的峰值電流值將需要更長的時間。雖然通過延長導通時間間隔可以自動降低工作頻率,但每個工作周期儲存在電感中的能量仍將保持不變。工作頻率下降可以導致電路的最大功率能力隨之下降。此時,電路的最大功率能力曲線表現(xiàn)為不同的形狀(參見圖4)。

最小輸入電壓與最大輸出功率之間的關系如公式(2)和公式(3)所示。

對比以上兩條曲線可以明顯確定,與DCMFF(固定頻率占空比限制)設計相比,導通時間延長方案可以使功率轉換器在較低的輸入電壓下輸出更高的功率(參見圖4)。

通過這兩條曲線還可以看到,對于輸出端50%的負載,DCMFF可以維持直流總線電壓降至大約69V的穩(wěn)壓,而DCMDE轉換器則可以維持低至31.5V的穩(wěn)壓。因此,DCMDE方法使電源能夠為內存?zhèn)浞莶僮魈峁└L的維持時間,充分利用儲仔于輸入電容中的能量。

直流輸入總線濾波電容值的選擇

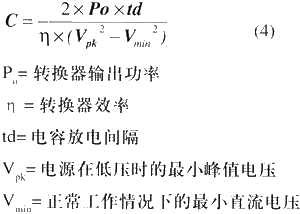

如圖6所示,直流總線濾波電容可以用來將轉換器階段的輸入電壓維持在等于或高于Vmin值的水平,使轉換器可以保持工作并維持穩(wěn)壓。參考文獻[1]、[2]和[3]中提供有計算這一電容值的詳細方法。轉換器在td期間所需的能量由放電電容提供。所需的電容值可以通過公式(4)進行估算。

90VDC或100VDC的值是轉換器最小直流總線電壓的最佳選擇,這一點在參考文獻[3]中已有說明。Vmin值進一步減小有助于降低輸入端所需的電容值,但這也會導致初級繞組中的峰值電流大幅升高,并且還需要過大設計電路中的開關元件。

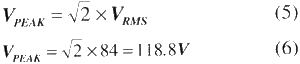

如果開關電源必須保持工作并在干擾期間提供穩(wěn)壓輸出電壓,則必須對其輸入電容進行選擇,以使最小輸入RMS電壓比額定電壓低30%,即120V系統(tǒng)的最小輸入RMS電壓約為84 VAC(參見公式(5)和公式(6))。

在任何給定輸入電源電壓情況下,時間td是工作頻率的函數(參見圖6)。

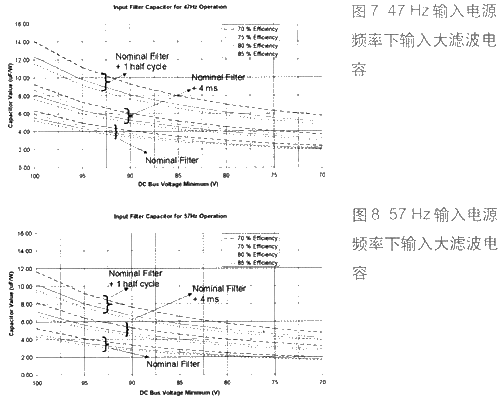

圖7和圖8顯示了在不同轉換器工作頻率下的不同最小直流總線電壓值(Vmin)所需的輸入電容估計值。三組曲線分別表示:不需要任何維持的條件下的額定電容;4 ms的維持時間;輸入電源線電壓頻率的一個半周期的維持時間。

對于正常工作情況或存在短時間電源線干擾的工作情況,圖7和圖8提供了易于使用的倍增系數,用于計算所需的電容值。此電容的值稱為Cn或額定電容。

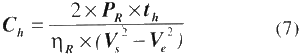

用于在斷電序列期間維持穩(wěn)壓的直流總線電壓最小值可以從圖4得出,或使用公式(1)和公式(2)計算得出。然后,可以使用公式(7)來計算輸入端所需的電容值,以確保在完成斷電序列期間能夠提供足夠長的維持時間。

Ch=完成斷電序列或內存?zhèn)浞菟璧碾娙?/p>

PR=在斷電序列期間降低的輸出功率水平

ηR=功率水平降低時的轉換器效率

th=斷電序列的持續(xù)時間

Vs=斷電序列開始時的直流總線電壓

Ve=功率降低時維持穩(wěn)壓所需要達到的直流總線電壓

如果Ch遠遠大于Cn,則必須使用較高的值。可以通過提高Vmin來減小計算的Cn和Ch

值之間的差異。

對于設計用于在低至100VDC的直流總線電壓下工作且必須在低至47Hz的頻率下工作的20W通用輸入電源來說,正常工作情況下的輸入電容值或Cn將大約為100μF,其前提

是轉換器效率超過85%(見圖7)。

如果在輸入電源失敗后必須至少在35 ms的時間內提供穩(wěn)壓電源(以便完成EEPROM寫周期),那么電容Ch中必須具備足夠的能量。

如果內存?zhèn)浞萜陂g所需的負載為10 W(滿載的50%),且電源采用最大占空比為50%、固定頻率100 kHz控制器設計而成,那么所需的電容值將為172μF,該值可以使用公式(1)、公式(4)或圖4計算得出。

如果將此電源的控制方案修改為使用導通時間延長技術,則所需的Ch值可大幅減少到100 μF,使用公式(4)或圖4可以計算出該值。因此,無需擴充輸入電容便能滿足延長的(35ms)功率要求。

在前面的示例中,假設在較低直流電壓和50%的負載條件下運行時轉換器功率降至78%(在實際設計中,這一點可經過全面驗證)。

導通時間延長技術的限制

雖然導通時間延長可顯著提高反激式電源的功率輸出,但必須注意的是,不要讓電源在延長的導通時間下無限期地運行。導通時間在超過正常極限之外的任何延長均會導致RMS電流的增加,從而導致MOSFET及初級繞組上的功率全部耗盡。

結語

電源需要配備正確容量的輸入電容,這樣可以確保在電源線干擾期間仍能夠正常運行,并可在檢測出輸入故障之后,提供足夠時間的穩(wěn)壓電源,確保關鍵數據在關斷之前得以儲存。如果使用的是帶導通時間延長功能的集成開關,則在本應用中可大幅減小輸入電容的容量。本文所列舉的示例表明,DCMFF技術(不含導通時間延長設計)需要更高的輸入電壓才能輸出與DCMDE技術(含導通時間延長設計)同等數量的功率,在低于設計的最小直流電壓下工作時更是如此。導通時間延長是Powei Integrations的離線式開關IC中集成的眾多功能之一,設計師采用這些IC可以設計出更為高效和更具成本效益的電源產品。