電路功能與優(yōu)勢(shì)

將寬帶DAC互補(bǔ)電流輸出轉(zhuǎn)換為單端信號(hào)的傳統(tǒng)方法是使用中心抽頭變壓器,,或者在差分轉(zhuǎn)單端配置中使用一個(gè)單通道運(yùn)算放大器,。然而,變壓器的低頻非線性可能會(huì)限制其在DC附近使用,;運(yùn)算放大器方法則要求電阻嚴(yán)格匹配,,以提供直流共模抑制,、負(fù)載阻抗和互補(bǔ)DAC輸出之間的增益匹配,。如果匹配有誤差,,則最終輸出也會(huì)產(chǎn)生誤差。本電路利用差分接收放大器AD8130實(shí)現(xiàn)簡(jiǎn)單的差分轉(zhuǎn)單端功能,,無(wú)需使用昂貴的精密電阻,,從而以更少的元件提供更高的精度。

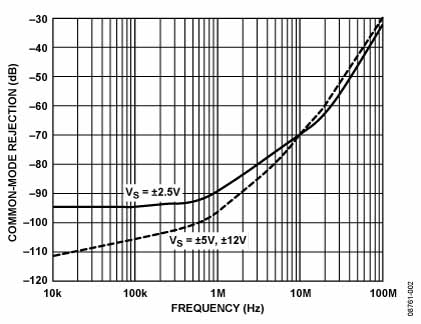

AD8130還有一個(gè)優(yōu)勢(shì),,即具有業(yè)界領(lǐng)先的交流共模抑制性能(10 MHz時(shí)為70 dB),。可以利用這一特性抑制DAC數(shù)字地層與接收器模擬地層之間的噪聲,,這是此類混合信號(hào)應(yīng)用的一個(gè)常見(jiàn)問(wèn)題,。

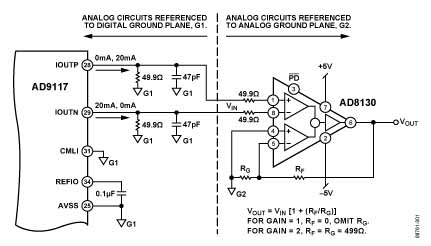

圖1. 用接收器AD8130實(shí)現(xiàn)高速TxDAC差分轉(zhuǎn)單端(原理示意圖,未顯示去耦和所有連接)

電路描述

本電路采用20 mA互補(bǔ)電流輸出,、低功耗,、14位、125 MSPS,、雙通道TxDAC®數(shù)模轉(zhuǎn)換器AD9117和低成本,、270 MHz差分接收放大器AD8130。

通過(guò)改變FSADJI或FSADJQ與地之間的電阻值,,可以在4 mA至20 mA范圍內(nèi)調(diào)整AD9117的滿量程輸出電流,。本例使能了內(nèi)部電阻選項(xiàng),并將其設(shè)置為1.6 kΩ,,以便提供最大20 mA電流輸出,。該配置要求將0b10100000寫入AD9117的寄存器IRSET和QRSET?;パa(bǔ)電流輸出采用49.9 Ω外部電阻端接,,以產(chǎn)生差分電壓。采用滿量程數(shù)字輸入擺幅時(shí),,這些電阻上產(chǎn)生的電壓彼此相差180°,,大小介于0 V至1 V之間,因此峰峰值差分輸出電壓為2 V,。一個(gè)47 pF電容與這些負(fù)載電阻并聯(lián),,構(gòu)成一個(gè)68 MHz一階重構(gòu)濾波器,并衰減奈奎斯特帶寬之外的鏡像,。與AD8130輸入引腳串聯(lián)的兩個(gè)49.9 Ω電阻可改善電路的整體失真性能,。共模輸出引腳CMLI和CMLQ可以用來(lái)提供附加偏移,但本例中未使用,,而是將其接地,。

AD8130是一款理想的互補(bǔ)產(chǎn)品,,因?yàn)樗休^大的平衡輸入阻抗,可以將差分輸入輕松轉(zhuǎn)換為單端格式,,并具有出色的交流共模抑制性能,,如圖2所示。

圖2. AD8130共模抑制

AD8130帶寬為270 MHz,,支持AD9117在最大更新速率125 MSPS時(shí)產(chǎn)生的最高達(dá)約40 MHz的DAC輸出頻率,。

本例中,AD8130的增益設(shè)置為1(RF,,省去RG),。不過(guò),只需改變RF/RG比,,就能調(diào)整增益,。電源設(shè)置為±5 V,但如果輸出端需要更大擺幅,,可以將其提高至最大±12 V,。

為使本電路正常工作,必須考慮與DAC和運(yùn)算放大器相關(guān)的裕量問(wèn)題,。DAC輸出電壓需保持在其規(guī)格范圍內(nèi),,防止內(nèi)部電路引入失真。當(dāng)DAC VDD = 3.3 V且VCM = 0 V時(shí),,AD9117輸出必須小于±1 V,,這可以通過(guò)49.9 Ω負(fù)載電阻和20 mA滿量程電流來(lái)實(shí)現(xiàn)。當(dāng)放大器輸出端負(fù)載為1 kΩ時(shí),,AD8130要求1 V的電源電壓裕量,;因此,當(dāng)采用±5 V電源時(shí),,輸出擺幅不能超過(guò)±4 V,。

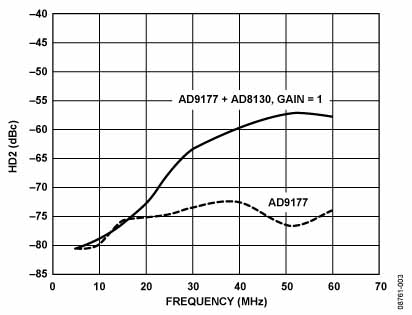

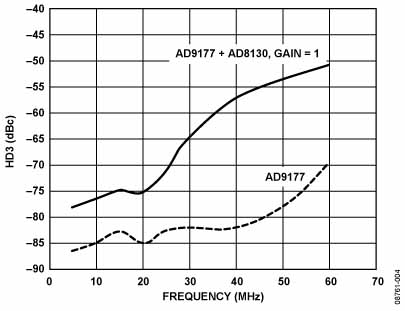

諧波失真是本設(shè)計(jì)的重要標(biāo)準(zhǔn)。圖3和圖4分別顯示了整個(gè)電路(AD9117 + AD8130)的二次和三次諧波失真測(cè)量結(jié)果,,以及AD9117本身的諧波失真,。測(cè)量在AD8130的增益設(shè)置為1(RF = 0,省去RG)的條件下進(jìn)行,。

圖3. 電路的二次諧波失真(G = 1)

圖4. 電路的三次諧波失真(G = 1)

如果時(shí)域應(yīng)用需要更快的上升/下降時(shí)間,,可以通過(guò)減小電容值來(lái)提高重構(gòu)濾波器的截止頻率。不過(guò),,與AD9117 DAC的內(nèi)在性能相比,,AD8130的270 MHz帶寬會(huì)限制上升/下降時(shí)間和建立時(shí)間。該電路仍然可以在3次DAC更新(125 MSPS)的時(shí)間內(nèi)建立,。

0.1 μF電容對(duì)AD9917內(nèi)部基準(zhǔn)電壓源去耦,。應(yīng)將一個(gè)0.1 μF低電感陶瓷去耦電容(圖1未顯示)與VDD相連,,并使其非??拷麬D9117,。

將AD8130的引腳4和RG(圖2中顯示為G2)連接到一個(gè)失調(diào)電壓(VOFF),可以獨(dú)立于放大器增益來(lái)調(diào)整AD8130的輸出電壓失調(diào),,使其值不為0 V,。該配置中,VOFF出現(xiàn)在單位增益輸出端,,而AD8130的增益仍然為1+RF/RG,。

為了使本文所討論的電路達(dá)到理想的性能,必須采用出色的布線,、接地和去耦技術(shù),。至少應(yīng)采用四層PCB:一層為接地層,一層為電源層,,另兩層為信號(hào)層,。

所有IC電源引腳都必須采用0.01 μF至0.1 μF低電感多層陶瓷電容(MLCC)去耦至接地層(為簡(jiǎn)明起見(jiàn),圖中未顯示),,并應(yīng)遵循各IC數(shù)據(jù)手冊(cè)和教程MT-101的相關(guān)建議,。

常見(jiàn)變化

只要將輸出頻率保持在AD8130的帶寬范圍內(nèi),就可以在本配置中使用其它TxDAC IC,,例如AD9707,、AD9717、AD9767或AD9744,。