現代單片機" title="單片機">單片機(MCU)擁有豐富的外設和功能,極大地方便了設計的功耗" title="功耗">功耗預算。全面了解器件的相關知識對于嵌入式設計人員非常重要,只有這樣,設計人員才能充分利用可用的模式和外設來降低設計功耗。

充分利用省電模式" title="省電模式">省電模式和功能

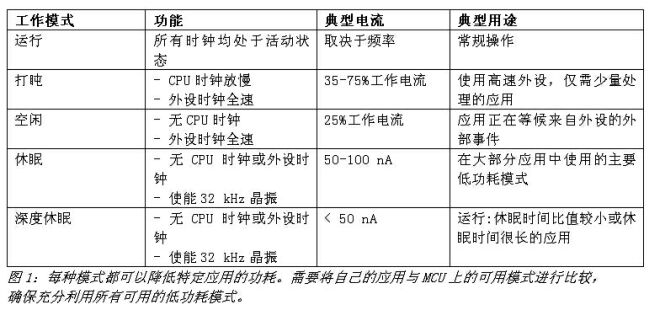

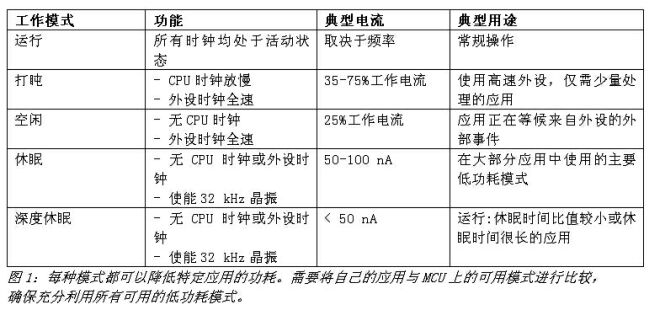

大多數單片機都設有多種模式,可提供各種省電選項。盡管模式的名稱可能各不相同,但是幾乎所有MCU都會提供“運行”、“空閑”和“休眠”三種典型模式。圖1給出了許多單片機上可用模式的匯總。在一些情況下,何時使用哪種模式是顯而易見的;例如,對于主要的處理工作,只能使用運行模式。在處理工作完成后,如果需要長時間等候外部事件,顯然應該選擇休眠模式。何時適合選擇空閑模式并不容易判定,但是在發(fā)送或接收大批量的數據時最常選擇該模式。在保留其他功能的同時等候較短時間延遲來關閉CPU,也會使用空閑模式。

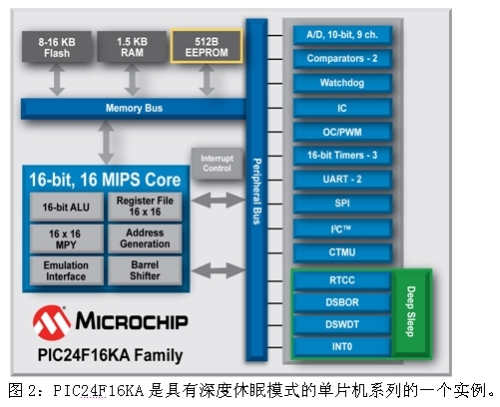

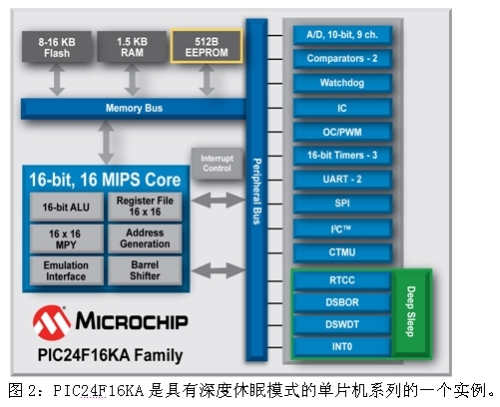

對于特定架構的多種其它模式和功能的熟悉程度非常重要。雖然僅使用上述一些熟悉的模式也可以使設計功耗達到可接受的水平,但是要使應用的電流消耗達到絕對的最低水平,最好是利用器件的獨特功能。例如,某些MCU采用了一種新型斷電模式,該模式取消對MCU的內核供電以最大程度地降低功耗,從而使功耗低于常規(guī)斷電模式下的功耗。這種模式通常被稱為“深度休眠”。圖2中顯示的PIC24F16KA 16位MCU便是深度休眠器件的一個實例。

MCU內核斷電時RAM也將斷電,這樣會導致其它低功耗模式(如休眠)下仍然可以保留的某些信息丟失。既然代價如此高昂,那么什么情況下才適合使用深度休眠模式呢?使用深度休眠模式的好處是取消器件的大部分供電時產生的漏電流很小,這可以顯著降低掉電電流——某些情況下可以降到50 nA以下,如圖1所示。小漏電流還使得深度休眠模式在高溫或高壓應用中的表現更好,高溫和高壓常常導致休眠模式電流增加。深度休眠模式的另一個主要優(yōu)點是可以實現設計尺寸更小且性能更佳的芯片,同時不用放棄低功耗目標。這種模式最適用于掉電時間較長的應用,這些應用中減小掉電電流的重要性遠遠超過使應用重新初始化的成本。

設計人員對器件的熟悉度變得重要的另一個原因是,不僅只有低功耗模式才能降低功耗,很多用于提升性能的功能也有利于降低功耗。例如,如果某個器件有內部振蕩器,則用戶可以在主晶振開始運行初始化代碼的同時使用該內部振蕩器,這樣便可以縮短器件喚醒所需的總時間。

現代單片機(MCU)擁有豐富的外設和功能,極大地方便了設計的功耗預算。全面了解器件的相關知識對于嵌入式設計人員非常重要,只有這樣,設計人員才能充分利用可用的模式和外設來降低設計功耗。

充分利用省電模式和功能

大多數單片機都設有多種模式,可提供各種省電選項。盡管模式的名稱可能各不相同,但是幾乎所有MCU都會提供“運行”、“空閑”和“休眠”三種典型模式。圖1給出了許多單片機上可用模式的匯總。在一些情況下,何時使用哪種模式是顯而易見的;例如,對于主要的處理工作,只能使用運行模式。在處理工作完成后,如果需要長時間等候外部事件,顯然應該選擇休眠模式。何時適合選擇空閑模式并不容易判定,但是在發(fā)送或接收大批量的數據時最常選擇該模式。在保留其他功能的同時等候較短時間延遲來關閉CPU,也會使用空閑模式。

對于特定架構的多種其它模式和功能的熟悉程度非常重要。雖然僅使用上述一些熟悉的模式也可以使設計功耗達到可接受的水平,但是要使應用的電流消耗達到絕對的最低水平,最好是利用器件的獨特功能。例如,某些MCU采用了一種新型斷電模式,該模式取消對MCU的內核供電以最大程度地降低功耗,從而使功耗低于常規(guī)斷電模式下的功耗。這種模式通常被稱為“深度休眠”。圖2中顯示的PIC24F16KA 16位MCU便是深度休眠器件的一個實例。

MCU內核斷電時RAM也將斷電,這樣會導致其它低功耗模式(如休眠)下仍然可以保留的某些信息丟失。既然代價如此高昂,那么什么情況下才適合使用深度休眠模式呢?使用深度休眠模式的好處是取消器件的大部分供電時產生的漏電流很小,這可以顯著降低掉電電流——某些情況下可以降到50 nA以下,如圖1所示。小漏電流還使得深度休眠模式在高溫或高壓應用中的表現更好,高溫和高壓常常導致休眠模式電流增加。深度休眠模式的另一個主要優(yōu)點是可以實現設計尺寸更小且性能更佳的芯片,同時不用放棄低功耗目標。這種模式最適用于掉電時間較長的應用,這些應用中減小掉電電流的重要性遠遠超過使應用重新初始化的成本。

設計人員對器件的熟悉度變得重要的另一個原因是,不僅只有低功耗模式才能降低功耗,很多用于提升性能的功能也有利于降低功耗。例如,如果某個器件有內部振蕩器,則用戶可以在主晶振開始運行初始化代碼的同時使用該內部振蕩器,這樣便可以縮短器件喚醒所需的總時間。

數字外設" title="數字外設">數字外設的功耗

集成外設有助于顯著提升MCU的性能并允許移除外部元件,這兩點都有利于降低功耗。但是,如果使用不當,運行外設的成本會高過所節(jié)省的功耗。可以通過幾種簡單的技巧使外設自身的供電成本最小化,以維持低功耗應用。

一般來說,單片機中使用的最耗電的外設是串行通信總線。I2C和SPI通信均使用多條高速線路。驅動這些線路的供電成本非常高。SPI在高速運行時消耗的電流會達到毫安級,因為它需要驅動三條高速I/O總線。驅動這些總線時的開關損耗會導致極大的電流消耗。相比而言,I2C運行速度較慢,但是因為它使用了上拉電阻,而當低電阻上拉用于實現高速時會造成相當大的電流,因此電流消耗會更大。

降低這些串行通信外設功耗的最簡單的方法是降低速度;但是,并不是所有情況下都可以這樣做。既然運行串行通信的大部分成本來自于驅動總線,那么我們就應該將焦點放在驅動總線上。對于SPI而言,采用走線較短的簡潔電路板布局來最小化線路阻抗很重要。而I2C則相反——在總線上采用值較高的上拉電阻可以降低電流消耗,并且在某些情況下并不會減慢最大速度。要最小化這兩種情況下的功耗,可以減少總線上的器件數量或關閉未使用的器件的電源,而不是在選擇芯片上費腦筋。在軟件中,如果某個應用正在等候串行數據,可以通過禁止CPU來降低這些外設的功耗。另外,也可以將串行傳輸數據組合成集群,而不是持續(xù)傳輸,這樣應用就可以更長時間保持在省電模式,而在更少時間處于喚醒狀態(tài)以發(fā)送和接收數據。

模擬外設" title="模擬外設">模擬外設的功耗

MCU上的模擬外設會對電流消耗產生很大的影響。BOR、比較器和ADC等模擬功能需要消耗足夠的功率才能產生準確的結果。因此,當這些功能部件在低功耗模式下運行時,無法總是像對數字功能那樣對其進行功耗優(yōu)化。正因為如此,確保應用僅在需要時使能模擬功能(而不是始終使能)就變得非常重要。若要降低ADC的采樣速率,往往使用盡可能快的時鐘和盡可能短的采樣時間而不是延長采樣時間或放慢ADC時鐘。而且,在采樣完成后,應該禁止ADC。對于很多MCU而言,這樣做可以用更低的功耗產生相同的結果。類似地,在器件運行過程中使用BOR功能來檢測會導致錯誤執(zhí)行的小幅壓降,比在器件處于省電模式時使用該功能更重要,因為在省電模式下,僅要求檢測大到足以造成RAM崩潰的壓降。因此,將BOR配置成采用功耗更低的休眠模式比配置成運行模式更加有用,這樣的話,可以利用在休眠時較低的功耗強度要求并達到低至50nA或更低的電流消耗,同時還能在運行時維持高性能。

本文小結

所有MCU都有一系列可用于降低設計功耗的功能。但是,這些功能中只有一小部分應用到了所有器件中。因此,熟悉所使用的單片機的所有外設和獨特功能非常重要,只有這樣才能真正實現功耗得到優(yōu)化的設計。