隨著計算機和數(shù)字圖像處理技術(shù)的飛速發(fā)展,視頻監(jiān)控技術(shù)應(yīng)用廣泛。傳統(tǒng)的視頻監(jiān)控系統(tǒng)都是用單一攝像頭對某一固定場景進行監(jiān)控,不僅視頻的視野范圍有限,而且不能對同一個物體的不同方位進行監(jiān)控。這里提出了一種多通道視頻監(jiān)控系統(tǒng),通過對不同視頻通道穩(wěn)定、可靠地切換控制,實現(xiàn)監(jiān)控不同場景。該系統(tǒng)不僅彌補了傳統(tǒng)監(jiān)控視頻范圍有限的不足,而且提高了監(jiān)控資源的利用率,降低了監(jiān)控

成本。

1 系統(tǒng)硬件結(jié)構(gòu)

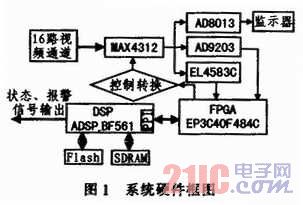

采用DSP+FPGA的硬件結(jié)構(gòu)方案,利用DSP和FPGA控制MAX4312選通所需要的視頻通道,從而達到在多路視頻通道間進行切換的目的。系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

1.1 控制器件的選型

根據(jù)實際需要,DSP采用ADI公司推出的Blackfin" title="Blackfin">Blackfin系列高性能處理器ADSP_BF561" title="BF561">BF561(以下簡稱BF561)作為算法處理和控制核心,BF561處理器包含2個獨立的BF533內(nèi)核,每個內(nèi)核分別包含2個乘/累加器(MAC),2個40位的ALU,4個視頻ALU和1個40位移位器。Blackfin處理器采用改進

的哈佛結(jié)構(gòu)和分級的存儲器結(jié)構(gòu)。L1存儲器一般以全速運行,沒有或只有很少延遲。L2是另一級存儲器,分布在片內(nèi)或片外,對其訪問會消耗多個處理器周期。在L1級,指令存儲器只存放指令,2個數(shù)據(jù)存儲器存放數(shù)據(jù),1個專用的臨時數(shù)據(jù)存儲器存儲堆棧和局部變量信息。在L2級,采用統(tǒng)一的存儲空間,可以存放指令和數(shù)據(jù)。這里采用L2級存儲器。

FPGA采用Altera公司的EP3C40F48C" title="EP3C40F48C">EP3C40F48C對視頻信號進行預(yù)處理,該芯片具有多達24 624個邏輯單元,具有高級外部存儲器接口,允許將外部單數(shù)據(jù)率(SDR)SDRAM" title="SDRAM">SDRAM,雙數(shù)據(jù)率(DDR)SDRAM和DDR FCRAM器件集成到復(fù)雜系統(tǒng)設(shè)計中,而不會降低數(shù)據(jù)訪問性能,具有129個兼容的LVDS通道,每個通道數(shù)據(jù)率高達640 Mb/8,還有4個可編程鎖相環(huán)和8個全局時鐘線。另外EP3C40F484C的功耗較低,全局運行時總功耗為300 mW左右。

1.2 Flash" title="Flash">Flash的設(shè)計

根據(jù)系統(tǒng)設(shè)計的需要,F(xiàn)lash采用CMOS型的M29W640D,其空間為18 Mx16 bit。該系統(tǒng)中,外部數(shù)據(jù)線為D1~D15,地址線為A2~A22。連接時需要注意,因為Flash是16 bit位寬,硬件連接上需要地址錯位,即DSP的A2對應(yīng)Flash的A1,DSP的A3對應(yīng)Flash的A2,依次類推。在軟件

編程上,任何對Flash的操作,如擦除、寫入,均要先對特定地址寫入一定數(shù)量固定的控制命令字,即簽到指令,這樣確保在通電和斷電時,不會對存儲器誤操作。

1.3 SDRAM的設(shè)計

該系統(tǒng)所采用的外部數(shù)據(jù)存儲器是大容量SDRAM MT48LC16M16,其容量是4 Bankx8 Mx16 bit。根據(jù)該系統(tǒng)設(shè)計的實際要求,SDRAM在系統(tǒng)運行時存儲實時圖像數(shù)據(jù)、基準數(shù)據(jù)以及程序代碼。由于Flash的存取速度比較慢,在Flash里,在系統(tǒng)初始化時應(yīng)預(yù)先將存儲在其中的基準數(shù)據(jù)及程序代碼搬到更快的存儲器里面,以便DSP不受存儲器讀取時間的制約,充分發(fā)揮其高速性能。

1.4 視頻采集模塊設(shè)計

由于視頻通道的切換時間非常短,這就需要切換控制模塊對視頻信號有一個非常準確的判斷,以便及時發(fā)送切換命令,因此需要選擇一款高速的轉(zhuǎn)換器。另外由于本系統(tǒng)的電源為5 V供電,因此需要選擇一款低功耗的器件。因此選擇AD9203作為模擬信號的數(shù)字量化器件。

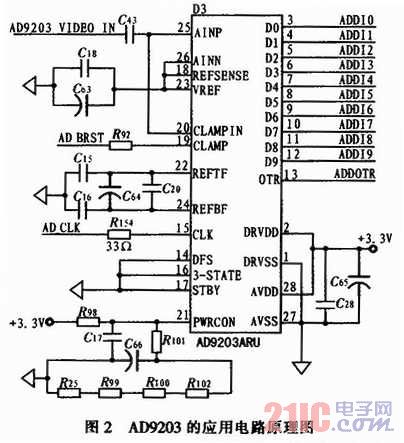

AD9203是ADI公司出品的一款單通道、低電壓的高速A/D轉(zhuǎn)換器,采樣速率可達40 Ms/s。其精度穩(wěn)定可靠,在全采樣帶寬范圍內(nèi),始終基本保持著10位的精度;在40 Ms/s的采樣速率下,ENOB(有效位數(shù))仍然達到9.55位,差分非線性度±0.25 LSB,信噪比和失真度保持在59 dB左右。AD9203的工作電壓比較靈活,允許住2.7~3.6 V范圍內(nèi)變動,特別適合于便攜式設(shè)備在低電壓下的高速操作。在3 V的供電下,40 Ms/s全速工作時,功耗只有74 mW;在5 Ms/s時,功耗將會降到17 mW,在待機模式下,功耗只有0.65 mW。對于輸入信號的峰峰值,通常設(shè)置為1 Vp-p或者2 Vp-p。另外,AD9203允許外部電壓參考,可以根據(jù)設(shè)計需要,在1~2 V間靈活地設(shè)置輸入信號的峰峰值。圖2是AD9203的電路應(yīng)用原理圖。

2 控制模塊設(shè)計

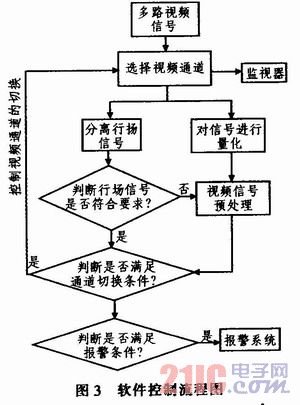

整個系統(tǒng)的工作流程為,在不同的監(jiān)控點上安裝多個攝像頭進行圖像監(jiān)控,多路圖像視頻信號通過MAX4312,每一時刻選通其中一路視頻信號輸入。該視頻信號經(jīng)過AD8013AR處理后從圖像監(jiān)控器輸出數(shù)字圖像信號,同時從行場分離芯片EL4583C輸出相應(yīng)的行(VIDEO_Hs)、場(VIDEO_Vs)信號,從AD9203輸出圖像后肩信號(AD_BRST)和視頻量化信號。然后將行(VIDEO_Hs)、場(VIDEO_Vs)信號送進DSP,將后肩信號(AD_BRST)和視頻量化信號送進FPGA。FPGA利用這些信號對圖像進行預(yù)處理,然后將處理后的圖像通過PPI口送給DSP中進行算法處理。最后由DSP發(fā)送視頻通道切換命令完成不同通道之間的切換,并且將最后處理結(jié)果送給報警和狀態(tài)指示裝置,實現(xiàn)監(jiān)控告警功能。軟件控制流程如圖3所示。

2.1 FPGA模塊功舵買現(xiàn)

FPGA控制部分用于對視頻信號進行預(yù)處理并且等待DSP發(fā)送切換命令。其基本思路為:當某一路視頻信號經(jīng)過AD9203之后,輸出的視頻量化信號被送進FPGA做預(yù)處理,然后被送入DSP進行算法處理,同時FPGA等待DSP根據(jù)場信號發(fā)送的視頻通道切換命令。

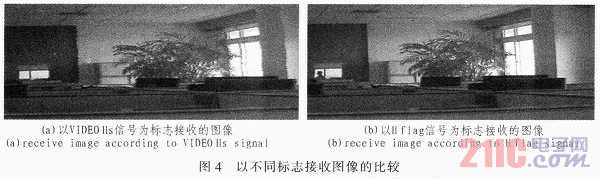

在實驗過程中發(fā)現(xiàn),DSP對圖像的搜索是以行信號的上升沿(或者下降沿)為觸發(fā)的,因此需要行信號有一個穩(wěn)定的上升沿(或者下降沿)。由于信號在分離傳輸?shù)倪^程中可能會產(chǎn)生抖動,導(dǎo)致信號的上升沿(或者下降沿)不穩(wěn)定,從而影響DSP對視頻信號的判斷。若仍然以這個不穩(wěn)定的行信號(VIDEO_Hs)作為DSP搜索圖像的標志,則其接收的圖像將會在相鄰兩行出現(xiàn)錯位的現(xiàn)象,用肉眼看到的圖像漂移現(xiàn)象。圖4中(a)圖像是以VIDEO_Hs信號為標志接收的圖像。這就需要FPGA對行(VIDEO_Hs)信號做去抖動處理,但是FPGA接收到的信號只有EL4583分離出來的行信號,無法分辨信號上升沿(或者下降沿)的具體位置。因此FPGA根據(jù)需要產(chǎn)生1個行標志信號(H_flag),來取代不穩(wěn)定的行信號(VIDEO_Hs),然后將行標志信號(H_flag)和場信號(VIDEO_Vs)送給DSP,以便對視頻信號做出準確判斷。圖4中(b)圖像是以H_flag信號為標志接收的圖像。

2.2 PPI口的設(shè)置

FPGA和DSP之間的數(shù)據(jù)通信是通過PPI口實現(xiàn)的。PPI(并行外部接口)是半雙工形式,具有雙向端口,最大可進行16位數(shù)據(jù)的輸入輸出。 PPI有5個存儲器來控制其操作。其中PPI控制寄存器(PPI_CONTROL)設(shè)置了PPI口的操作模式、控制信號極性以及端口的帶寬。在本設(shè)計中,設(shè)置PPI_CONTROL為0x00EC,將PPI的工作模式設(shè)置為ITU_656模式,端口的寬度設(shè)置為8位,并且僅僅為接收數(shù)據(jù)的模式。由于每個在DMA總線上的PPI_CLK_initiated事件(即輸入或輸出操作)都處理16為實體,也就是說如果傳輸?shù)臄?shù)據(jù)不是16位,則把數(shù)據(jù)的高位補0湊成16為數(shù)據(jù)。這種情況下,更有效的辦法是把數(shù)據(jù)打包,即把2個FPGA傳輸?shù)?位數(shù)據(jù)合成1個16位的數(shù)據(jù),再進行傳輸,這樣有效地利用了資源,提高了傳輸效率。

2.3 DSP控制功能實現(xiàn)

DSP控制功能的實現(xiàn)過程,首先設(shè)置DSP的PF此腳,以便判斷PF引腳上的中斷信號。定義FPGA與DSP的中斷信號的通信是通過PF6和PF7傳送的,然后對DMA(直接存儲器訪問)進行設(shè)置,在對視頻信號進行處理時,分別處理奇偶場信號,也就是在某一時刻只處理信號的奇數(shù)場或者偶數(shù)場,以便提高信號的處理速度。這就需要把視頻信號的奇偶場分別存儲,在設(shè)置DMA時,將奇偶場信號數(shù)據(jù)存儲在不同的地址下面。

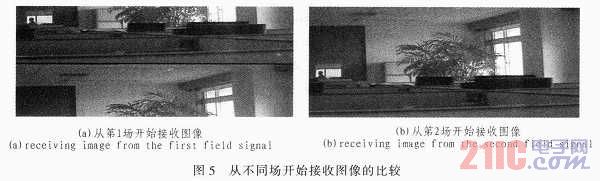

當DSP通過PF引腳接收到FPGA發(fā)送的信號時開始實現(xiàn)其控制功能,具體控制切換的過程為:DSP在接收到PPI口傳輸?shù)牡谝粋€VIDEO_Vs信號時,通過場計數(shù)器(VsCount)開始對視頻信號進行計數(shù),然后讀取VsCount的數(shù)值,當VsCount的計數(shù)達到切換要求時,DSP將發(fā)送一個切換命令給FPGA,即在某一地址下面寫一個數(shù)值,讓FPGA通過DSP_A和DSP_D讀取命令完成視頻通道的切換。由于在視頻通道切換的前后,兩個通道的場信號可能會出現(xiàn)不同步的現(xiàn)象,所以在通道切換后的第2場開始搜索圖像,圖5分別是DSP從第1場和第2場開始接收圖像的結(jié)果。

3 系統(tǒng)測試結(jié)果

實驗對24路視頻信號進行切換,并且設(shè)定每一路視頻信號的切換時間為6場,也就是每經(jīng)過6場信號的時間就對視頻通道進行一次切換。不同視頻通道之間切換時的穩(wěn)定時間也不會超過一場,也就是說,兩通道之間在切換之后在一場之內(nèi)就可以穩(wěn)定。實驗結(jié)果表明,該系統(tǒng)能夠穩(wěn)定、可靠地實現(xiàn)多視頻通道之間的切換,可以在一套監(jiān)控設(shè)備上添加多個攝像頭對不同的場景進行實時監(jiān)控,這樣不僅有效解決了傳統(tǒng)監(jiān)控系統(tǒng)監(jiān)視目標單一的缺點,而且提高了監(jiān)控效率,降低了監(jiān)控成本。

4 結(jié)束語

首先簡單介紹了整個系統(tǒng)硬件架構(gòu)和芯片的性能,描述了整個系統(tǒng)的工作流程,然后著重闡述了DSP和FPGA對多視頻通道的控制與選通。FPGA整個設(shè)計程序是在QuartusⅡ平臺上用Verilog硬件描述語言編寫,DSP程序在VisualDSP++編譯成功,二者都經(jīng)過多次調(diào)試驗證。該系統(tǒng)設(shè)計已成功應(yīng)用于多場景監(jiān)控告警系統(tǒng)中,準確、可靠地切換不同視頻通道。