0 引言

隨著工藝的進(jìn)步以及深亞微米集成電路技術(shù)的不斷發(fā)展,芯片的集成度越來越高,芯片的規(guī)模也越來越大。在無線通信、圖像處理等各個(gè)芯片應(yīng)用領(lǐng)域,越來越多的系統(tǒng)芯片(SoC)選擇將各個(gè)功能不同的模擬電路模塊和數(shù)字電路模塊集成在同一芯片中,以便在整個(gè)系統(tǒng)的性能達(dá)到最優(yōu)的同時(shí)使成本降到最低。但這卻給芯片的測(cè)試帶來了意想不到的困難,也使得測(cè)試成本大為增加。ADC作為連接數(shù)字系統(tǒng)和模擬系統(tǒng)的橋梁,其測(cè)試顯得格外重要。隨著ADC性能的不斷提高,芯片外部環(huán)境也已經(jīng)成為ADC測(cè)試的主要障礙。為了解決上述問題,同時(shí)更準(zhǔn)確地測(cè)試ADC作為IP核集成到SoC中工作時(shí)的真實(shí)性能,各種ADC的內(nèi)建自測(cè)試(Built-In-Self Test)方法應(yīng)運(yùn)而生,而如何精確而高效地為ADC內(nèi)建自測(cè)試提供測(cè)試激勵(lì)是一個(gè)非常關(guān)鍵的問題。本文提出一種可用于ADC片上測(cè)試的三角波信號(hào)發(fā)生器的實(shí)現(xiàn)方法,產(chǎn)生的三角波具有非常好的線性度,可以滿足14 b高精度ADC的測(cè)試要求。整個(gè)設(shè)計(jì)采用UMC 0.18 μm CMOS工藝實(shí)現(xiàn),電源電壓為1.8 V。

1 三角波信號(hào)發(fā)生器的設(shè)計(jì)約束

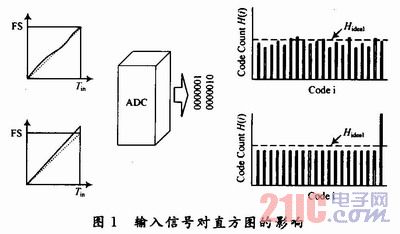

碼密度直方圖測(cè)試法基于統(tǒng)計(jì)學(xué),用該法對(duì)ADC的靜態(tài)特性進(jìn)行測(cè)試時(shí)所加的測(cè)試激勵(lì)必須盡量接近理想,在本文中也就是要盡量獲得精準(zhǔn)的三角波。如果獲得的三角波信號(hào)存在非線性或增益誤差,則用該信號(hào)去測(cè)試一個(gè)理想的ADC,測(cè)得的碼元的直方圖分布就會(huì)不均勻(如圖1所示),這種不均勻來自測(cè)試激勵(lì)本身的誤差,所以由此測(cè)得的ADC的積分非線性(INL)和微分非線性(DNL)就引入了誤差。這樣一來,測(cè)試結(jié)果的精確性很大程度上取決于所加三角波信號(hào)的精確度。所以,在設(shè)計(jì)三角波發(fā)生器時(shí),必須根據(jù)被測(cè)ADC的性能指標(biāo)來確定所需要的三角波發(fā)生器的線性度以及幅度。本文所設(shè)計(jì)的三角波信號(hào)發(fā)生器要滿足精度為14 b的ADC的測(cè)試要求,那么其精度要求必須不低于16 b。

2 三角波信號(hào)發(fā)生器的原理

產(chǎn)生三角波信號(hào)的原理是用一個(gè)恒定不變的正向電流對(duì)電容進(jìn)行充電得到一個(gè)均勻上升的斜波電壓,當(dāng)電壓上升到一定值時(shí)再用一個(gè)恒定不變的負(fù)向電流對(duì)電容放電,從而得到一個(gè)均勻下降的斜波電壓,交替用正負(fù)方向的電流對(duì)電容進(jìn)行充放電,就可以得到連續(xù)的三角波電壓信號(hào),上升和下降的斜率由正負(fù)向電流與電容的比值I/C決定。為了滿足ADC測(cè)試的要求,三角波信號(hào)應(yīng)具有較好的線性度,同時(shí)也要保證較低的斜率,這就需要一個(gè)精確的小電流和一個(gè)較大的電容。

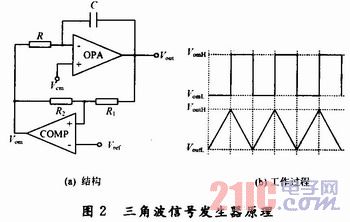

圖2描述了三角波信號(hào)發(fā)生器的原理。圖中運(yùn)算放大器、電阻R、電容C組成一個(gè)方波積分器;比較器、電阻R1、電阻R2組成一個(gè)遲滯比較器作為一個(gè)反饋控制電路。電路的工作過程如下:

(1)當(dāng)比較器輸出電平為低電平VomL時(shí),電容C處于充電狀態(tài),Vout不斷上升,當(dāng)Vout的值上升到使得比較器正相輸入端電壓高于Vref時(shí),比較器輸出翻轉(zhuǎn),輸出高電平VomH,同時(shí)電流方向改變,電容C進(jìn)入放電狀態(tài);

(2)當(dāng)比較器輸出電平為高電平VomH時(shí),電容C處于放電狀態(tài),Vout不斷下降,當(dāng)Vout的值下降到使得比較器正相輸入端電壓低于Vref時(shí),比較器輸出翻轉(zhuǎn),輸出低電平VomL,同時(shí)電流方向也翻轉(zhuǎn),電容C進(jìn)入充電狀態(tài);

(3)如此循環(huán)振蕩,便產(chǎn)生了周期的連續(xù)三角波電壓信號(hào)。

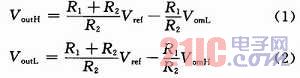

輸出三角波電壓信號(hào)Vout的閾值電壓為:

式中:Vref為比較器負(fù)端參考電壓;VomH,VomL分別為比較器輸出的高、低電平。

由以上公式可知,周期T由RC常數(shù)、峰峰值Vout.pp以及比較器輸出的高低電平VomH,VomL決定。

3 具體電路設(shè)計(jì)實(shí)現(xiàn)

3.1 運(yùn)算放大器設(shè)計(jì)

運(yùn)算放大器是整個(gè)電路結(jié)構(gòu)中的關(guān)鍵部分,它直接決定了三角波信號(hào)發(fā)生器的線性度和線性輸出范圍。運(yùn)算放大器與電阻R、電容C構(gòu)成積分電路,其主要作用是使積分電容C一端電平保持穩(wěn)定,這就要求運(yùn)放具有較高的增益;同時(shí),為了使三角波信號(hào)發(fā)生器的線性輸出范圍盡可能大,要求運(yùn)放具有較大的輸出擺幅。

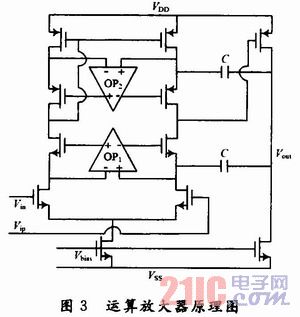

本文中運(yùn)算放大器采用兩級(jí)結(jié)構(gòu),如圖3所示。其中:輸入級(jí)采用帶增益自舉電路的套筒式共源共柵結(jié)構(gòu),包括主運(yùn)放和輔助運(yùn)放。主運(yùn)放采用NMOS輸入的套筒式共源共柵結(jié)構(gòu),具有高增益、低功耗以及良好的頻率特性。輔助運(yùn)放OP1,OP2分別為采用PMOS輸入和NMOS輸入的折疊式共源共柵全差分結(jié)構(gòu),進(jìn)一步提高運(yùn)放增益。第二級(jí)采用共源結(jié)構(gòu)來改善套筒式共源共柵結(jié)構(gòu)輸出擺幅小的缺點(diǎn),同時(shí)也能一定程度上提高運(yùn)算放大器的開環(huán)增益。由于級(jí)數(shù)增加也會(huì)引入新的零極點(diǎn),從而會(huì)影響運(yùn)放的穩(wěn)定性。所以,必須加入補(bǔ)償電容C,使相位裕度滿足要求。

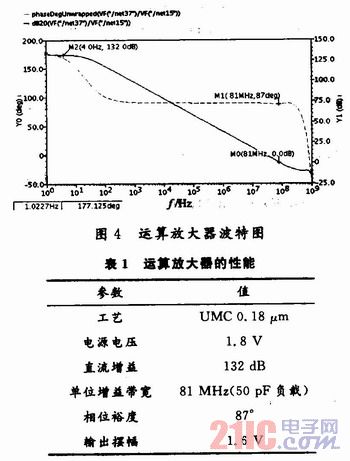

由Spectre仿真所得的運(yùn)算放大器的交流幅頻、相頻特性如圖4所示。表1總結(jié)了運(yùn)算放大器的基本性能參數(shù)。

3.2 遲滯比較器設(shè)計(jì)

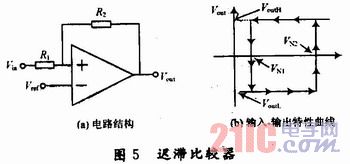

遲滯比較器的遲滯特性是比較器中引入正反饋的結(jié)果。遲滯比較器有兩個(gè)輸入閾值,當(dāng)輸入電壓經(jīng)過其中一個(gè)閾值時(shí)輸出電壓會(huì)改變,同時(shí)輸入閾值會(huì)跳變到另一個(gè)值。要再次改變輸出,輸入必須到達(dá)跳變之后的閾值,在輸出改變的同時(shí),閾值又會(huì)跳變回原來的值。本文所采用的遲滯比較器電路及輸入-輸出特性曲線如圖5所示。

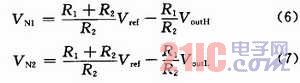

兩個(gè)輸入閾值分別為:

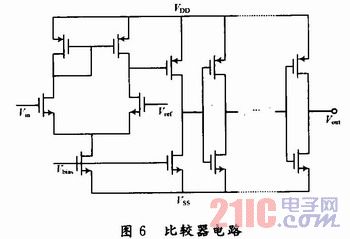

遲滯比較器中的比較器電路采用兩級(jí)開環(huán)運(yùn)放實(shí)現(xiàn),由于比較器后級(jí)是一個(gè)2 mΩ的電阻,所以必須使比較器輸出級(jí)電阻足夠低,以防止由于電阻分壓而導(dǎo)致比較器輸出電壓達(dá)不到電源電壓以及地電壓。因此,在兩級(jí)開環(huán)運(yùn)放之后增加了一個(gè)大寬長(zhǎng)比的反相器鏈以獲得較低的輸出電阻,如圖6所示。

4 仿真結(jié)果

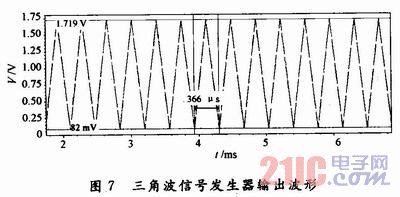

對(duì)該三角波信號(hào)發(fā)生器整體電路進(jìn)行晶體管級(jí)仿真,仿真得到的三角波電壓信號(hào)范圍為82 mV~1.719 V,周期為366μs,如圖7所示。

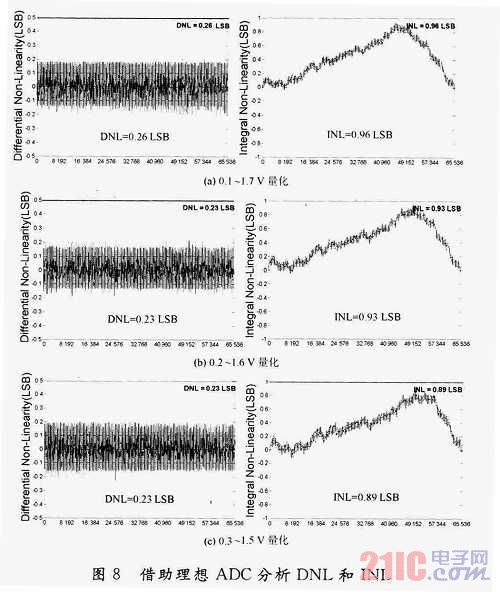

對(duì)該三角波信號(hào)進(jìn)行多個(gè)周期的采樣,利用16 b理想ADC分別對(duì)0.1~1.7 V,0.2~O.6 V,0.3~1. 5 V這三個(gè)不網(wǎng)的電壓范圍進(jìn)行量化轉(zhuǎn)換,并做相應(yīng)的碼密度直方圖分析,得到各自的DNL和INL,如圖8所示。從圖8中可以看到,對(duì)于16 b理想ADC的量化,這三種不同的電壓范圍INL都在1 LSB以下(等價(jià)于INL<24μV),可以滿足14 b ADC靜態(tài)特性的測(cè)試。

5 結(jié)語(yǔ)

本文設(shè)計(jì)了一款應(yīng)用于高精度ADC片上測(cè)試的高精度高線性度模擬三角波信號(hào)發(fā)生器,可為高達(dá)14 b的ADC靜態(tài)參數(shù)片上測(cè)試提供有效的激勵(lì)。仿真結(jié)果表明,該信號(hào)發(fā)生器所生成的三角波電壓信號(hào)范圍為82 mV~1.719 V,周期為366μs,INL<24 μV,等效精度達(dá)到16b以上,其幅值和頻率可根據(jù)具體的設(shè)計(jì)要求進(jìn)行調(diào)節(jié),而且其線性度表現(xiàn)良好,可滿足14 b高精度ADC靜態(tài)參數(shù)的測(cè)試需求。