引言

隨著電子技術(shù)的發(fā)展,數(shù)字電路的集成度和性能有了非常大的提高,因此可以在單板上實現(xiàn)復(fù)雜的電路功能,本設(shè)計就是在TI公司高集成度的TMS320F2812處理器上設(shè)計外圍接口電路,實現(xiàn)多路高速ARINC429接口、高速RS422接口、高速RS232接口,由于該款DSP的卓越性能,該接口板具有強大的多路接口通訊實時處理能力,同時由于該接口板的通訊接口都是標(biāo)準(zhǔn)接口,物理結(jié)構(gòu)為PMC底板結(jié)構(gòu),具有一定的通用性。

系統(tǒng)設(shè)計

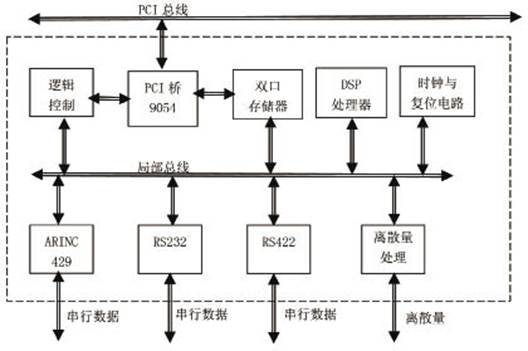

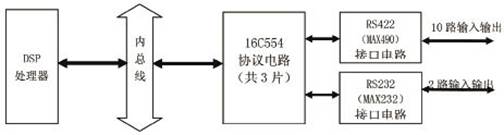

接口板采用TMS320F2812處理器,對串行數(shù)據(jù)的接收和發(fā)送采用智能控制方式,它通過一個512K(32K×16)雙端口存儲器(DPRAM)實現(xiàn)與主處理機(jī)之間的數(shù)據(jù)交互,雙端口存儲器與主處理機(jī)之間為PCI總線接口,物理連接方式為PMC標(biāo)準(zhǔn)插座。模塊功能框圖見圖1。限于篇幅,本文主要介紹局部總線端電路設(shè)計,與主機(jī)接口端PCI設(shè)計另有文章介紹。

圖1 接口板功能框圖

接口板主要由如下功能部分組成:

•處理器電路、數(shù)據(jù)處理器TMS320F2812,主頻150MHz,集成128K字容量程序FLASH、18K字容量SARAM;

• 雙口RAM IDT70V27,容量為32K×16bit;

• 時鐘和復(fù)位電路MAX791;

• 10路全雙工RS422串行接口電路TL16C554;

• 2路全雙工RS232串行接口電路;

• 4收2發(fā)ARINC429接口DEI1016A、BD429A;

• PCI總線接口電路PCI9054;

• 邏輯控制電路XC95288XL;

• 提供+5V轉(zhuǎn)+15V、-15V電路DCP020515DP,負(fù)載80mA。

處理器及存儲電路

處理器

處理器選用TI公司的16位TMS320F2812芯片,主頻可達(dá)到150MHz。主要特點如下:

• 150MIPS運行速度;

• 集成128K字容量程序FLASH,18K字容量SARAM;

• 56路獨立的可編程多路復(fù)用I/O引腳;

• 鎖相環(huán)(PLL)模塊;

• 3個32位定時器

• 2個串行通信接口SCI;

• 1個串行外設(shè)接口SPI;

• 16路ADC(12bit);

• 2路eCAN接口;

• 3個可屏蔽中斷;

• JTAG接口;

• 哈佛結(jié)構(gòu)。

本接口板在設(shè)計中用到TMS320F2812處理器的數(shù)據(jù)處理功能、存儲器功能、通用IO功能、串行通信功能和JTAG接口。16位地址線A15~A0,16位數(shù)據(jù)線D15~D0。

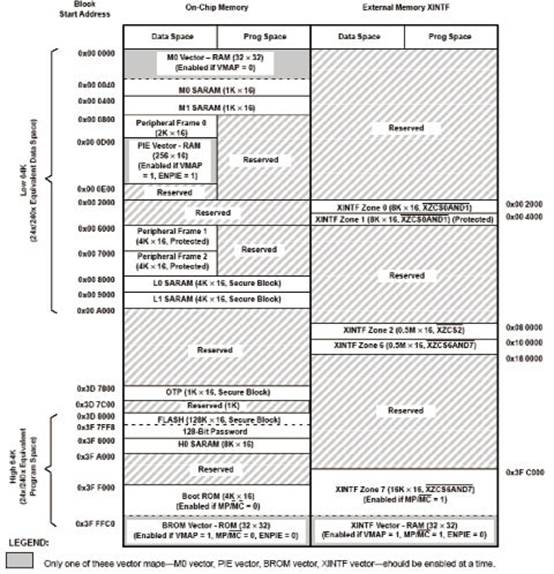

TMS320F2812處理器地址空間映像如圖2所示。該接口板地址分配如表1。

圖2 地址映象

存儲電路

在實時系統(tǒng)中,串行數(shù)據(jù)的采集及交換是影響系統(tǒng)開銷的瓶頸之一,在這類系統(tǒng)中,數(shù)據(jù)交換要求的通訊速率往往很高。傳統(tǒng)的并行接口和串行接口設(shè)計無論在通信速率,還是在可靠性方面都不易滿足要求。而雙端口RAM則是一個較好的實現(xiàn)方案。它具有通訊速率高、接口設(shè)計簡單等特點,因而能在這類設(shè)計中得到廣泛的應(yīng)用。

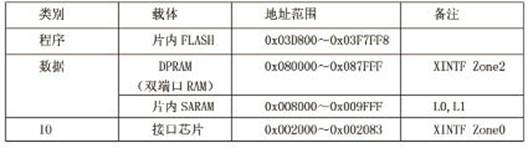

表1 地址分配表

雙端口RAM芯片有兩套完全獨立的數(shù)據(jù)線、地址線和讀寫控制線,因而可使兩個處理器分時獨立訪問其內(nèi)部RAM資源。由于兩個CPU同時訪問時的仲裁邏輯電路全部集成在雙端口RAM內(nèi)部,因而需要實際設(shè)計的電路比較簡單。雙端口RAM內(nèi)一般都有一個總線搶占優(yōu)先級比較器,只要雙CPU不同時訪問同一存儲單元,那么較先送出地址的CPU將擁有該單元的本次訪問優(yōu)先權(quán),而另一個CPU的地址與讀寫信號將被屏蔽掉,同時通過“busy”引腳告知該CPU以使之根據(jù)需要對該單元重新訪問或撤銷訪問。雙端口RAM的優(yōu)點是通訊速度快、實時性強、接口比較簡單、兩邊CPU都可主動進(jìn)行數(shù)據(jù)傳輸;缺點是成本高,需要克服競爭現(xiàn)象。

共享存儲器選用雙口內(nèi)存IDT7027,存儲容量為32K×16bit。共享存儲器具有兩組獨立的地址、控制、I/O引腳,允許從任一組引腳發(fā)出的信號對內(nèi)存中的任何位置進(jìn)行讀或?qū)懙漠惒皆L問。雙口內(nèi)存IDT7027具有防止雙口競爭的功能,該功能可以免去為避免雙口競爭增加的硬件邏輯,通過使用芯片上的信號量可以獲得芯片的控制權(quán),只有獲權(quán)的一組引腳上的信號才能訪問內(nèi)存,另外通過信號量的使用還可以將雙口內(nèi)存劃分為大小不同的區(qū)。

在此模塊設(shè)計中,雙口存儲器一邊由DSP處理器控制,另一邊由PCI總線進(jìn)行控制,而芯片本身自帶的BUSY通過邏輯設(shè)計接READY來實現(xiàn)雙口存儲器產(chǎn)生競爭時的應(yīng)答。

雙口存儲器讀操作訪問

雙口存儲器的讀操作時序如圖3所示,/CE為讀寫數(shù)據(jù)操作的片選信號,低電平有效;/OE為輸出控制信號,由系統(tǒng)讀信號控制,低電平有效;/UB、/LB是高/低字節(jié)有效控制信號,低電平有效,設(shè)計中將這兩信號下拉;R/*W信號在讀操作中保持高電平。

雙口存儲器寫操作訪問

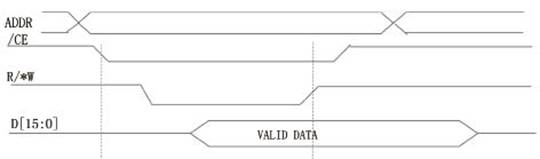

雙口存儲器的寫操作時序如圖4

所示,/CE為寫數(shù)據(jù)操作的片選信號,低電平有效;/UB、/LB是高/低字節(jié)有效控制信號,低電平有效,設(shè)計中將這兩信號下拉;R/*W為輸入控制信號,由系統(tǒng)寫信號控制,低電平有效。

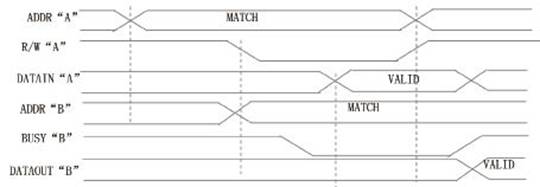

雙口存儲器BUSY信號使用及時序

A/B通道對雙口存儲器的某一個單元同時進(jìn)行訪問時會出現(xiàn)競爭冒險,要避免這種情況的出現(xiàn)必須對訪問信號判斷優(yōu)先級,IDT7025雙口存儲器通過自身硬件的BUSY信號引腳告知該CPU以使之根據(jù)需要對該單元重新訪問或撤消訪問,其操作時序如圖5所示,BUSY信號低電平有效,R/W為讀寫信號。

圖3 讀操作及時序

圖4 寫操作及時序

圖5 讀寫操作時序

時鐘和復(fù)位電路

時鐘電路

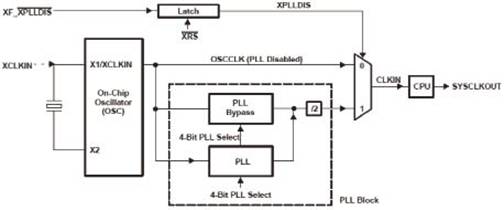

F2812處理器上有基于PLL的時鐘模塊,為器件及各種外設(shè)提供時鐘信號。鎖相環(huán)有4位倍頻設(shè)置位,可以為處理器提供各種頻率的時鐘。時鐘模塊提供兩種操作模式,如圖6所示。

內(nèi)部振蕩器:如果使用內(nèi)部振蕩器,則必須在X1/XCLKIN和X2引腳之間連接一個石英晶體;

外部時鐘:如果使用外部時鐘,可以把時鐘信號直接接到X1/XCLKIN引腳上,X2懸空。

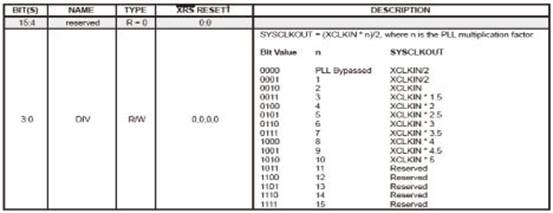

外部XPLLDIS引腳用來選擇系統(tǒng)時鐘源。當(dāng)XPLLDIS為低電平時,系統(tǒng)直接采用外部時鐘作為系統(tǒng)時鐘;當(dāng)XPLLDIS為高電平時,外部時鐘經(jīng)過PLL倍頻后,為系統(tǒng)提供時鐘。系統(tǒng)通過鎖相環(huán)控制寄存器來選擇鎖相環(huán)的工作模式和倍頻系數(shù),如表2所示。

表2 鎖相環(huán)控制寄存器位定義

該接口板采用30M石英晶體提供時鐘,XPLLDIS引腳上拉使能PLL模塊,倍頻選擇最大的XCLKIN×5=150MHz。

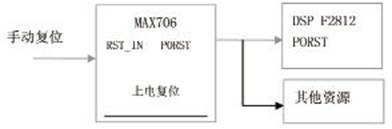

復(fù)位電路

復(fù)位電路會中斷F2812的執(zhí)行,復(fù)位板上資源,同時使處理器從0x3FF000地址開始執(zhí)行指令序列。F2812的復(fù)位可由外部復(fù)位管腳引起。

F2812外部復(fù)位源采用MAX706芯片進(jìn)行復(fù)位,MAX706復(fù)位的產(chǎn)生條件有以下3種情況:

a. 上電復(fù)位,當(dāng)Vcc>4.40V(典型值)時產(chǎn)生復(fù)位,并保持200ms復(fù)位有效;

b. 掉電復(fù)位,當(dāng)Vcc<4.40V(典型值)時產(chǎn)生復(fù)位,此時可防止對存儲器進(jìn)行錯誤寫入;

c. 手動復(fù)位,當(dāng)手動復(fù)位信號有效,產(chǎn)生復(fù)位,用于調(diào)試。

MAX706的復(fù)位信號形成F2812的上電復(fù)位輸入,使系統(tǒng)所有資源復(fù)位。復(fù)位電路如圖7所示。

串行總線處理電路

本模塊串行數(shù)據(jù)的接收和發(fā)送都采用TL16C554協(xié)議芯片來完成,RS422和RS232總線傳輸通過不同的接口芯片完成電平轉(zhuǎn)換,其功能框圖如圖8所示。

圖6 DSP時鐘輸入電路

圖7 復(fù)位電路

圖8 串行數(shù)據(jù)功能實現(xiàn)電路

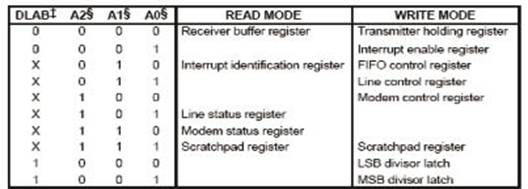

16C554通過對各個寄存器的編程完成串行數(shù)據(jù)的初始化及傳輸,在上電初始化時,本模塊將串行數(shù)據(jù)初始化為數(shù)據(jù)位8位,停止位1位,無奇偶校驗位,波特率為115.2KBPS,在完成上電BIT后,主機(jī)可通過改變雙口存儲器的初始化參數(shù)來滿足自身對串行數(shù)據(jù)格式的約定,16C554各寄存器地址分配如表3,各個寄存器對應(yīng)的訪問地址為該串行通道分配的基地址加上偏移地址,即:各寄存器訪問地址=BASE+[A2A1A0]16。

表3 協(xié)議芯片寄存器地址分配

串行協(xié)議芯片通過有效的初始化才能實現(xiàn)串行數(shù)據(jù)的正確接收和發(fā)送,在進(jìn)行初始化的時候確保串行通道沒有接收和發(fā)送數(shù)據(jù)。其初始化流程如表4所示。

表4 串行協(xié)議芯片初始化

控制邏輯電路

控制邏輯電路負(fù)責(zé)整個DSP數(shù)據(jù)處理模塊上控制和狀態(tài)信號的產(chǎn)生,負(fù)責(zé)PCI總線時序控制和邏輯譯碼。該邏輯功能由CPLD可編程邏輯器件實現(xiàn),邏輯描述由VHDL語言完成。控制邏輯電路主要完成以下功能:

a. TMS320F2812總線時序支持電路;

b.系統(tǒng)總線接口時序支持電路;

c.地址譯碼;

d.地址轉(zhuǎn)換及地址三態(tài)控制;

e.實現(xiàn)對數(shù)據(jù)總線管理邏輯的控制;

f.系統(tǒng)總線復(fù)位。

結(jié)束語

根據(jù)以上原理,我們研制了該智能接口板,通用性強,接口簡單,可以滿足大多數(shù)應(yīng)用條件,經(jīng)使用證明設(shè)計合理,穩(wěn)定可靠。