本設(shè)計(jì)選用具有高集成度、低功耗、短開發(fā)周期的FPGA來完成此項(xiàng)設(shè)計(jì),以實(shí)現(xiàn)系統(tǒng)的ASIC為研究背景,具有很強(qiáng)的現(xiàn)實(shí)意義和廣闊的市場(chǎng)空間。 采用xilinx公司Spartan 3E系列FPGA作為核心控制器件,這款器件采用90ns的先進(jìn)工藝,最大容量50萬門,可支持32位的RISC處理器,具有128 Mbit 并行Flash,足以滿足設(shè)計(jì)的要求。該項(xiàng)目利用嵌入式軟核實(shí)現(xiàn)系統(tǒng)的管理,利用硬件實(shí)現(xiàn)識(shí)別算法,保證了系統(tǒng)功能的完整性與識(shí)別的正確性。

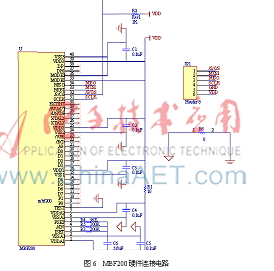

本設(shè)計(jì)中采用的是富士通的MBF200指紋傳感器,MBF200硬件框圖如圖6所示,采用SPI模式,所以MBF200與FPGA只通 MISO,MOSI,/S/C/S,SCLK四個(gè)端口相連接。 /S/C/S為MBF200的使能端,SCLK為MBF200的系統(tǒng)時(shí)鐘,當(dāng)需要采集指紋信號(hào)時(shí),F(xiàn)PGA向/S/C/S發(fā)送低電平,則MBF200開始工作。FPGA通過MOSI向MBF200發(fā)送控制命令,控制MBF200的數(shù)據(jù)輸出方式及傳輸模式。VDD[3:1]為數(shù)字電源輸入,VDDA[2:1]為模擬電源輸入,VSS[3:1]為數(shù)字地,VSSA[2:1]為模擬地,所以如圖所接。而為了防止數(shù)字信號(hào)對(duì)模擬信號(hào)的干擾,用 10歐電阻隔開。并且數(shù)字電源輸入與相應(yīng)的數(shù)字地之間均接有電容用來閣除非直流信號(hào)。為了防止數(shù)字地與信號(hào)地之間的干擾,本設(shè)計(jì)采用0歐電阻隔離。0歐電阻相當(dāng)于很窄的電流通路,能夠有效地限制環(huán)路電流,使噪聲得到抑制。電阻在所有頻帶上都有衰減作用(0歐電阻也有阻抗),這點(diǎn)比磁珠強(qiáng)。

MODE[1:0]引腳是用來設(shè)定MBF200所用接口模式的,在本設(shè)計(jì)中,置MODE[1:0]為01,選定SPI傳輸模式。 在SPI模式當(dāng)中,AIN,ISET,F(xiàn)EST三個(gè)接口都不會(huì)用上,但根據(jù)MBF200內(nèi)部電路結(jié)構(gòu),最好接電阻與地相接。