淺析IC測(cè)試開(kāi)發(fā)流程及量產(chǎn)數(shù)據(jù)對(duì)產(chǎn)品設(shè)計(jì)的影響

伍鳳娟1,王媛媛2

(西安科技大學(xué) 電氣與控制工程學(xué)院,陜西 西安 710054)

摘要:集成電路行業(yè)作為信息產(chǎn)業(yè)的基礎(chǔ),其應(yīng)用領(lǐng)域上至國(guó)防軍工下至家用電器。測(cè)試技術(shù)是檢測(cè)集成電路質(zhì)量好壞的重要環(huán)節(jié),對(duì)集成電路進(jìn)行測(cè)試可有效提高芯片的成品率。測(cè)試的主要目的是保證芯片在惡劣環(huán)境下能完全實(shí)現(xiàn)設(shè)計(jì)規(guī)格書(shū)所規(guī)定的功能及性能指標(biāo)。主要論述半導(dǎo)體后道測(cè)試對(duì)產(chǎn)品工藝的影響,旨在降低測(cè)試成本,提高測(cè)試質(zhì)量及測(cè)試精度。

關(guān)鍵詞:半導(dǎo)體;集成電路測(cè)試;量產(chǎn)數(shù)據(jù);產(chǎn)品工藝

中圖分類號(hào):TN407文獻(xiàn)標(biāo)識(shí)碼:ADOI: 10.19358/j.issn.1674 7720.2016.20.008

引用格式:伍鳳娟,王媛媛. 淺析IC測(cè)試開(kāi)發(fā)流程及量產(chǎn)數(shù)據(jù)對(duì)產(chǎn)品設(shè)計(jì)的影響[J].微型機(jī)與應(yīng)用,2016,35(20):31 33.

0引言

近年來(lái),我國(guó)集成電路產(chǎn)業(yè)已成為半導(dǎo)體行業(yè)所關(guān)注的焦點(diǎn)。其中集成電路測(cè)試作為設(shè)計(jì)、制造和封裝的有力技術(shù)支撐起著舉足輕重的作用。集成電路測(cè)試水平的高低直接決定著集成電路性能、質(zhì)量的好壞,因此受到業(yè)界的高度重視[1]。在集成電路領(lǐng)域,幾乎所有的芯片在出貨之前都要經(jīng)過(guò)幾道嚴(yán)格的測(cè)試,包括CP測(cè)試、FT測(cè)試及QA測(cè)試。每一道測(cè)試都會(huì)產(chǎn)生一系列的測(cè)試數(shù)據(jù),由于測(cè)試程序通常是由一系列測(cè)試項(xiàng)目組成的,從各個(gè)方面對(duì)芯片進(jìn)行充分檢測(cè),不僅可以判斷芯片性能是否符合標(biāo)準(zhǔn),是否可以進(jìn)入市場(chǎng),而且能夠從測(cè)試結(jié)果的詳細(xì)數(shù)據(jù)中充分、定量地反映出每顆芯片從結(jié)構(gòu)、功能到電氣特性的各種指標(biāo)。

1集成電路測(cè)試開(kāi)發(fā)流程

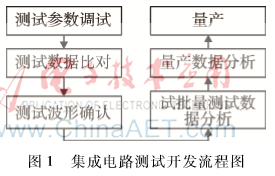

集成電路測(cè)試主要分為兩大類:參數(shù)測(cè)試和功能測(cè)試。根據(jù)集成電路設(shè)計(jì)和制造過(guò)程中對(duì)測(cè)試的需求,可分為設(shè)計(jì)驗(yàn)證測(cè)試、晶圓測(cè)試、封裝測(cè)試、可靠性測(cè)試[2]。針對(duì)不同類型的芯片,需要測(cè)試的具體項(xiàng)目會(huì)有所不同。如:運(yùn)算放大器類產(chǎn)品通常需要測(cè)試靜態(tài)電流ICC、失調(diào)電壓VIO、失調(diào)電流IB、電壓增益GV、電源抑制比PSRR、共模抑制比CMRR等;電源管理類產(chǎn)品需要測(cè)試基準(zhǔn)電壓Vref、工作頻率Fosc、啟動(dòng)電壓Vst、關(guān)斷電壓Vuvlo等。這些測(cè)試項(xiàng)是產(chǎn)品電氣特性的直接體現(xiàn),更是產(chǎn)品質(zhì)量的靈魂[3]。集成電路測(cè)試開(kāi)發(fā)就是針對(duì)這些測(cè)試項(xiàng)進(jìn)行準(zhǔn)確、快速、穩(wěn)定的測(cè)試。具體開(kāi)發(fā)流程如圖1所示。

(1)測(cè)試參數(shù)調(diào)試

利用集成電路專用的測(cè)試系統(tǒng)開(kāi)發(fā)平臺(tái),按照產(chǎn)品設(shè)計(jì)指標(biāo)及產(chǎn)品設(shè)計(jì)要求完成對(duì)待測(cè)芯片各測(cè)試項(xiàng)的調(diào)試,直至所有測(cè)試結(jié)果均分布在產(chǎn)品特性的Limit區(qū)間內(nèi)。集成電路各測(cè)試項(xiàng)的測(cè)試結(jié)果分布情況如圖2所示。

(2)測(cè)試數(shù)據(jù)比對(duì)

取一定數(shù)量的待測(cè)芯片,將經(jīng)過(guò)測(cè)試參數(shù)調(diào)試后所得的測(cè)試數(shù)據(jù)與樣品數(shù)據(jù)作差值比對(duì),若差值在容許范圍內(nèi)則測(cè)試系統(tǒng)給出的測(cè)試結(jié)果為Pass,否則為Fail。測(cè)試數(shù)據(jù)與樣品數(shù)據(jù)比對(duì)結(jié)果如圖3所示。

(3)測(cè)試波形確認(rèn)

為了確保測(cè)試程序正確可靠,需要對(duì)波形進(jìn)行確認(rèn)。通常情況下取一顆芯片,針對(duì)具體測(cè)試項(xiàng),將通過(guò)示波器觀察到的調(diào)試波形與樣品波形作比對(duì),從而確保波形一致性。某芯片的調(diào)試波形與樣品波形的比對(duì)圖如圖4所示。

以上三步做完之后,一個(gè)基本的測(cè)試程序開(kāi)發(fā)流程就完成了。接下來(lái)分析量產(chǎn)測(cè)試數(shù)據(jù)對(duì)產(chǎn)品工藝的影響。

2集成電路量產(chǎn)測(cè)試數(shù)據(jù)對(duì)產(chǎn)品工藝的影響

集成電路工藝的不斷演進(jìn)及設(shè)計(jì)技術(shù)的不斷提高,使集成電路測(cè)試技術(shù)面臨雙重挑戰(zhàn):制造工藝發(fā)展所帶來(lái)的測(cè)試質(zhì)量提高(包括新的故障類型、新的測(cè)試向量生成方法和可靠性保障等)和設(shè)計(jì)規(guī)模不斷發(fā)展所帶來(lái)的測(cè)試成本增加[4](包括不斷延長(zhǎng)的測(cè)試時(shí)間、不斷增長(zhǎng)的測(cè)試數(shù)據(jù)以及對(duì)新型測(cè)試設(shè)備的要求)。當(dāng)芯片出貨量巨大時(shí),所有這些產(chǎn)品的測(cè)試數(shù)據(jù)整合在一起就能夠在很大程度上反映出整個(gè)產(chǎn)品在設(shè)計(jì)和工藝制造上的一系列問(wèn)題,而這些問(wèn)題是難以在實(shí)驗(yàn)室通過(guò)對(duì)小批量產(chǎn)品進(jìn)行分析所獲得的。很多經(jīng)驗(yàn)豐富的設(shè)計(jì)公司都非常重視對(duì)實(shí)際量產(chǎn)數(shù)據(jù)的追蹤和分析,通過(guò)對(duì)這些測(cè)試數(shù)據(jù)的合理分析和利用,就能夠找到該產(chǎn)品在設(shè)計(jì)和生產(chǎn)工藝上存在的各種問(wèn)題,從而幫助設(shè)計(jì)人員和生產(chǎn)廠改善產(chǎn)品的性能和良率,甚至規(guī)避未來(lái)可能出現(xiàn)的產(chǎn)品設(shè)計(jì)質(zhì)量隱患。然而,遺憾的是國(guó)內(nèi)很多設(shè)計(jì)公司往往忽略了這一點(diǎn),或者即使意識(shí)到了量產(chǎn)測(cè)試數(shù)據(jù)的重要性,卻也不知道從哪里入手、怎樣去分析這些數(shù)據(jù)。因此,如何分析利用這些數(shù)據(jù)非常重要。

2.1量產(chǎn)數(shù)據(jù)與產(chǎn)品良率的關(guān)系

首先需要糾正的一個(gè)誤區(qū)是:很多設(shè)計(jì)公司在追蹤產(chǎn)品測(cè)試數(shù)據(jù)時(shí)只關(guān)心產(chǎn)品最終的良率,這顯然是不夠的。產(chǎn)品的某些突發(fā)工藝問(wèn)題并不一定直接反映在產(chǎn)品最終良率變化上,所以在觀察產(chǎn)品良率的同時(shí)必須追蹤各個(gè)fail bin的比例變化。當(dāng)某個(gè)fail bin的比例突發(fā)或漸進(jìn)地發(fā)生明顯變化的時(shí)候,就需要設(shè)計(jì)人員對(duì)其進(jìn)行深入調(diào)查,因?yàn)檫@很可能是導(dǎo)致產(chǎn)品品質(zhì)波動(dòng)的一個(gè)重要因素。

其次,測(cè)試程序的所有項(xiàng)目中除了純數(shù)字電路的測(cè)試只返回Pass/Fail信息外,其他項(xiàng)目結(jié)果往往都含有具體的測(cè)試數(shù)值,這些數(shù)據(jù)都反映了一顆芯片自身的某些特性,所以也必須加以恰當(dāng)?shù)赜?jì)算和分析。比較常用的方法除了計(jì)算每批產(chǎn)品的各個(gè)測(cè)試數(shù)值的平均值外,還需要通過(guò)計(jì)算正態(tài)分布的標(biāo)準(zhǔn)方差來(lái)獲得Cp/Cpk值。只有當(dāng)這些統(tǒng)計(jì)結(jié)果和歷史數(shù)據(jù)都基本吻合時(shí),才可以大致認(rèn)為該產(chǎn)品的品質(zhì)是可接受和可控的。實(shí)驗(yàn)證明,為保證產(chǎn)品良率,應(yīng)盡量使Cp>3.3、Cpk>1.3,否則很可能會(huì)導(dǎo)致良率低下或不穩(wěn)定造成的各種損失。

最后,通常會(huì)被嚴(yán)重忽略卻又至關(guān)重要的一項(xiàng)指標(biāo)是結(jié)果一致性確認(rèn)。很多產(chǎn)品由于出貨量巨大,往往需要多臺(tái)測(cè)試機(jī)同時(shí)進(jìn)行測(cè)試,每臺(tái)測(cè)試機(jī)有多個(gè)測(cè)試工位[5]。由于硬件有可能發(fā)生各種異常甚至事故,影響測(cè)試結(jié)果,因此測(cè)試人員必須隨時(shí)確認(rèn)各臺(tái)測(cè)試機(jī)以及測(cè)試工位之間的測(cè)試結(jié)果是否一致[6]。通常情況下,某臺(tái)設(shè)備的某個(gè)工位發(fā)生問(wèn)題導(dǎo)致良率下降往往會(huì)被總體良率數(shù)據(jù)所“淹沒(méi)”。若測(cè)試人員只關(guān)注總體良率的變化而不注重硬件之間的結(jié)果一致性指標(biāo),這些問(wèn)題就會(huì)被忽略,從而導(dǎo)致經(jīng)濟(jì)上的一系列損失。

2.2Wafer級(jí)別CP測(cè)試數(shù)據(jù)分析

與基于分離芯片的FT測(cè)試最大的不同是:CP測(cè)試是以Wafer為基本單位的,其測(cè)試結(jié)果數(shù)據(jù)不僅僅是每個(gè)die的測(cè)試結(jié)果,還包含了各個(gè)數(shù)據(jù)在整個(gè)Wafer甚至整個(gè)Lot內(nèi)的分布信息[7]。這些信息是和硅片加工的工藝條件緊密結(jié)合的,能夠給設(shè)計(jì)人員和工藝工程師提供大量的量產(chǎn)信息,這是FT測(cè)試結(jié)果所望塵莫及的。

最典型的一個(gè)CP數(shù)據(jù)分析方法是對(duì)Wafer面內(nèi)測(cè)試結(jié)果分布傾向的統(tǒng)計(jì)。由于單枚Wafer的面內(nèi)測(cè)試結(jié)果分布受隨機(jī)因素影響較大,因此將多枚Wafer的數(shù)據(jù)根據(jù)MAP圖疊加在一起進(jìn)行統(tǒng)計(jì)和計(jì)算[8]。圖5所示為某款芯片的CP測(cè)試良率面內(nèi)分布示意圖。由圖可明顯看出該Wafer中間良率和周邊良率的不同,通過(guò)此信息可反推生產(chǎn)工藝上存在的問(wèn)題,然而這些重要現(xiàn)象僅靠觀察每片Wafer的整體良率是無(wú)法及時(shí)發(fā)現(xiàn)的。

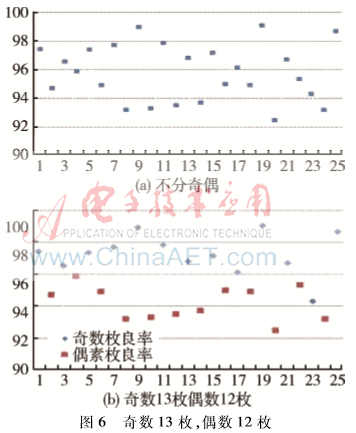

此外,還要確認(rèn)Wafer之間以及Lot之間測(cè)試數(shù)據(jù)的變化。該指標(biāo)可直接反映出Wafer之間的生產(chǎn)工藝穩(wěn)定性,若Fab廠的生產(chǎn)工藝不穩(wěn)定或發(fā)生過(guò)突發(fā)事故,就很容易從這個(gè)指標(biāo)看出問(wèn)題所在。圖6為L(zhǎng)ot內(nèi)25枚Wafer的良率分布圖。

圖6(a)中,除了良率波動(dòng)較大以外,很難看出其他的相關(guān)信息,而從圖6(b)中就很容易發(fā)現(xiàn)Wafer的良率在單數(shù)枚和偶數(shù)枚上的明顯差距:?jiǎn)螖?shù)13枚Wafer的平均良率為97.29%,而偶數(shù)12枚Wafer的良率只有94.16%。如果產(chǎn)品工程師對(duì)Fab工藝有足夠了解,就可以從數(shù)據(jù)上推測(cè),良率問(wèn)題很可能和生產(chǎn)線上某臺(tái)雙腔設(shè)備故障有關(guān)。因?yàn)槿绻O(shè)備有兩個(gè)腔對(duì)Wafer進(jìn)行單枚輪流作業(yè)(比如一些干刻和CVD設(shè)備),必然是單數(shù)枚Wafer在一個(gè)腔加工而雙數(shù)枚在另一個(gè)腔加工,一旦某個(gè)腔內(nèi)工藝條件出現(xiàn)問(wèn)題,就會(huì)發(fā)生上述良率分布異常的現(xiàn)象。可見(jiàn), Wafer間良率變化對(duì)產(chǎn)品工藝影響很大。

3結(jié)論

在集成電路測(cè)試開(kāi)發(fā)初期,要根據(jù)測(cè)試流程嚴(yán)格比對(duì)確認(rèn),確保測(cè)試開(kāi)發(fā)的可靠性、精度及穩(wěn)定性。只有在前期進(jìn)行足夠的驗(yàn)證工作,才能在正式量產(chǎn)中做到高質(zhì)量、低成本。同時(shí),作為信息寶庫(kù)重要數(shù)據(jù)的量產(chǎn)測(cè)試數(shù)據(jù)往往被很多設(shè)計(jì)公司所忽視,因此要高度重視對(duì)量產(chǎn)測(cè)試數(shù)據(jù)的分析,及時(shí)預(yù)判可能出現(xiàn)的異常信息并做出改進(jìn),從而提高產(chǎn)品工藝及質(zhì)量。

參考文獻(xiàn)

[1] 俞建峰,陳翔,楊雪瑛.我國(guó)集成電路測(cè)試技術(shù)現(xiàn)狀及發(fā)展策略[J].中國(guó)測(cè)試,2009,35(3):1-5.

[2] 劉新福,杜占平,李為民. 半導(dǎo)體測(cè)試技術(shù)原理與應(yīng)用[M].北京:冶金工業(yè)出版社,2007.

[3] 夏開(kāi)峰. 數(shù)據(jù)挖掘技術(shù)在半導(dǎo)體測(cè)試管理系統(tǒng)中的應(yīng)用[J].信息與電腦,2010(12):147.

[4] 汪天偉. 混合集成電路測(cè)試硬件電路測(cè)試板的設(shè)計(jì)[D].成都:電子科技大學(xué),2013.

[5] MORAVEK O, HOFFMAN K.Measurement and simulation of Coaxial to Microstrip ransitions radiation properties and substrate influence[J].Radio Engineering,2012,2(25):568-572.

[6] JJG(軍工)32 2014.模擬集成電路測(cè)試系統(tǒng)檢定規(guī)程[S].北京:國(guó)家國(guó)防科技工業(yè)局,2014-05-20.

[7] 秦國(guó)林,許斌,羅俊.集成電路圓片級(jí)可靠性測(cè)試[J].微電子學(xué),2013,20(1):144-145.

[8] 王曄.SoC芯片并行測(cè)試中幾個(gè)值得關(guān)注的問(wèn)題[J].半導(dǎo)體技術(shù),2010,35(12):1199-1203.