1 引言

對于邏輯芯片的嵌入存儲(chǔ)器來說,嵌入式SRAM 是最常用的一種,其典型的應(yīng)用包括片上緩沖器、高速緩沖存儲(chǔ)器、寄存器堆等。除非用到某些特殊的結(jié)構(gòu),標(biāo)準(zhǔn)的六管單元(6T)SRAM 對于邏輯工藝有著很好的兼容性。對于小于2Mb 存儲(chǔ)器的應(yīng)用,嵌入式SRAM 可能有更好的成本效率并通常首先考慮。

Xilinx 公司SRAM型FPGA 主要由配置存儲(chǔ)器、布線資源、可編程I/O、可編程邏輯單元CLB、塊存儲(chǔ)器BRAM 和數(shù)字時(shí)鐘管理模塊組成。它包含了分布式RAM,位于CLB中。每個(gè)CLB包含了16 × 1bit的SRAM結(jié)構(gòu)。BRAM的加入既增加了RAM的容量,也可構(gòu)成大型LUT,更完善了CLB 的功能。

2 BRAM塊劃分

現(xiàn)代數(shù)字系統(tǒng)對存儲(chǔ)器容量的存儲(chǔ)速率要求越來越高,讀訪問時(shí)間就是一個(gè)重要參數(shù),它是從地址信號的出現(xiàn)到存儲(chǔ)在該地址上的數(shù)據(jù)在輸出端出現(xiàn)的時(shí)間延遲。提高BRAM 讀取速度的一個(gè)有效辦法是減小位線和字線上的總負(fù)載電容,這可以通過減少連接在同一字線和位線上的存儲(chǔ)單元數(shù)目來實(shí)現(xiàn),即采用存儲(chǔ)陣列分塊技術(shù)。本電路采用設(shè)計(jì)多個(gè)BRAM的方法,每個(gè)BRAM都有自己的譯碼電路、敏感放大器和數(shù)據(jù)通道,各個(gè)BRAM 獨(dú)立工作,每個(gè)BRAM 的讀取時(shí)間得到了大大提高。

3 BRAM塊設(shè)計(jì)

3.1 BRAM與布線資源接口

FPGA 中每個(gè)BRAM塊都嵌在內(nèi)部連線結(jié)構(gòu)中,與BRAM 直接相連的有RAMLINE、VLONG 和GLOBAL。左邊32根RAMLINE提供BRAM的地址輸入,也可以提供控制信號(CLK、WE、ENA、RST)的輸入。左邊兩組16 根RAMLINE 一起布線提供BRAM雙端口的數(shù)據(jù)輸入,右邊兩組RAMLINE提供BRAM雙端口數(shù)據(jù)輸出通道。4 根GLOBLE全局時(shí)鐘線優(yōu)化用作時(shí)鐘輸入,提供較短的延遲和最小的失真。VLONG也被專門用作BRAM中WE、ENA、RST的控制輸入。RAMLINE 為BRAM專有布線,如從水平方向的SINGLE、UNIHEX、BIHEX通過可編程開關(guān)矩陣PSM 把信號輸送到RAMLINE 上,進(jìn)而送到BRAM 用作地址、數(shù)據(jù)。而BRAM 的輸出也通過RAMLINE最終送到HLONG上。

圖1 BRAM周圍布線

相鄰BRAM 的RAMLINE 也可通過三態(tài)門連到下一級的RAMLINE,于是整列中的BRAM 可共享RAMLINE 上的數(shù)據(jù)。每個(gè)BRAM與FPGA其他電路的相連主要通過水平方向的4 組主要互連線完成。

3.2 BRAM內(nèi)部設(shè)計(jì)

BRAM為真正的雙端口RAM,兩個(gè)端口完全獨(dú)立,每個(gè)端口可以配置為讀寫端口,并可以把BRAM配置成特定的數(shù)據(jù)寬度。

3.2.1 可配置數(shù)據(jù)位寬實(shí)現(xiàn)方法

配置邏輯中三位控制信號WIDTH_SEL《0∶2》連到BRAM中,同時(shí)對地址寬度、數(shù)據(jù)寬度進(jìn)行控制。

由于BRAM可以實(shí)現(xiàn)1、2、4、8、16 位的任意位寬,所以地址總線寬度、數(shù)據(jù)總線寬度都必須滿足其中任意一種模式下的要求。于是設(shè)計(jì)時(shí)使地址總線寬度為各種模式下的最大值,即1位時(shí)的地址寬度《11∶0》,其他模式下可使不用的地址位使能無效,進(jìn)而獲得所需的地址位。數(shù)據(jù)總線寬度也設(shè)置為各種情況下的最大值,即16 位時(shí)的數(shù)據(jù)寬度《15∶0》,其他情況下選擇有用的數(shù)據(jù)位進(jìn)行存儲(chǔ)。

表1可見WIDTH_SEL《0∶2》對地址使能的控制,主要在于對地址《11∶8》的控制,其他位地址《7∶0》則一直有效。

表1 不同數(shù)據(jù)位寬的地址使能

由WIDTH_SEL《0∶2》另外譯碼產(chǎn)生一組數(shù)據(jù)控制信號,分別為S_1、S_2、S_4、S_8、S_16 控制數(shù)據(jù)如何分配到位線上。這當(dāng)中* 根位線實(shí)行了分片,每片4 根:

S_1有效:DI《0》可分配到16片中的任何一片上。

S_2有效:DI《0∶1》可分配到《0∶1》、《2∶3》、《4∶5》?任何相鄰兩片上,每片1 位數(shù)據(jù)。

S_4有效:DI《0∶3》可分配到《0∶3》、《4∶7》、《8∶11》、《12∶15》任何相鄰四片上,每片1 位數(shù)據(jù)。

S_8 有效:DI《0∶7》可分配到《0∶7》或《8∶15》 8片上,每片1 位數(shù)據(jù)。

S_16 有效:DI《0∶15》剛好分配到16片上,每片1 位數(shù)據(jù)。

至于上述究竟存儲(chǔ)到哪些片上以及具體存儲(chǔ)到片內(nèi)哪根位線上則由列譯碼控制。

1 引言

對于邏輯芯片的嵌入存儲(chǔ)器來說,嵌入式SRAM 是最常用的一種,其典型的應(yīng)用包括片上緩沖器、高速緩沖存儲(chǔ)器、寄存器堆等。除非用到某些特殊的結(jié)構(gòu),標(biāo)準(zhǔn)的六管單元(6T)SRAM 對于邏輯工藝有著很好的兼容性。對于小于2Mb 存儲(chǔ)器的應(yīng)用,嵌入式SRAM 可能有更好的成本效率并通常首先考慮。

Xilinx 公司SRAM型FPGA 主要由配置存儲(chǔ)器、布線資源、可編程I/O、可編程邏輯單元CLB、塊存儲(chǔ)器BRAM 和數(shù)字時(shí)鐘管理模塊組成。它包含了分布式RAM,位于CLB中。每個(gè)CLB包含了16 × 1bit的SRAM結(jié)構(gòu)。BRAM的加入既增加了RAM的容量,也可構(gòu)成大型LUT,更完善了CLB 的功能。

2 BRAM塊劃分

現(xiàn)代數(shù)字系統(tǒng)對存儲(chǔ)器容量的存儲(chǔ)速率要求越來越高,讀訪問時(shí)間就是一個(gè)重要參數(shù),它是從地址信號的出現(xiàn)到存儲(chǔ)在該地址上的數(shù)據(jù)在輸出端出現(xiàn)的時(shí)間延遲。提高BRAM 讀取速度的一個(gè)有效辦法是減小位線和字線上的總負(fù)載電容,這可以通過減少連接在同一字線和位線上的存儲(chǔ)單元數(shù)目來實(shí)現(xiàn),即采用存儲(chǔ)陣列分塊技術(shù)。本電路采用設(shè)計(jì)多個(gè)BRAM的方法,每個(gè)BRAM都有自己的譯碼電路、敏感放大器和數(shù)據(jù)通道,各個(gè)BRAM 獨(dú)立工作,每個(gè)BRAM 的讀取時(shí)間得到了大大提高。

3 BRAM塊設(shè)計(jì)

3.1 BRAM與布線資源接口

FPGA 中每個(gè)BRAM塊都嵌在內(nèi)部連線結(jié)構(gòu)中,與BRAM 直接相連的有RAMLINE、VLONG 和GLOBAL。左邊32根RAMLINE提供BRAM的地址輸入,也可以提供控制信號(CLK、WE、ENA、RST)的輸入。左邊兩組16 根RAMLINE 一起布線提供BRAM雙端口的數(shù)據(jù)輸入,右邊兩組RAMLINE提供BRAM雙端口數(shù)據(jù)輸出通道。4 根GLOBLE全局時(shí)鐘線優(yōu)化用作時(shí)鐘輸入,提供較短的延遲和最小的失真。VLONG也被專門用作BRAM中WE、ENA、RST的控制輸入。RAMLINE 為BRAM專有布線,如從水平方向的SINGLE、UNIHEX、BIHEX通過可編程開關(guān)矩陣PSM 把信號輸送到RAMLINE 上,進(jìn)而送到BRAM 用作地址、數(shù)據(jù)。而BRAM 的輸出也通過RAMLINE最終送到HLONG上。

圖1 BRAM周圍布線

相鄰BRAM 的RAMLINE 也可通過三態(tài)門連到下一級的RAMLINE,于是整列中的BRAM 可共享RAMLINE 上的數(shù)據(jù)。每個(gè)BRAM與FPGA其他電路的相連主要通過水平方向的4 組主要互連線完成。

3.2 BRAM內(nèi)部設(shè)計(jì)

BRAM為真正的雙端口RAM,兩個(gè)端口完全獨(dú)立,每個(gè)端口可以配置為讀寫端口,并可以把BRAM配置成特定的數(shù)據(jù)寬度。

3.2.1 可配置數(shù)據(jù)位寬實(shí)現(xiàn)方法

配置邏輯中三位控制信號WIDTH_SEL《0∶2》連到BRAM中,同時(shí)對地址寬度、數(shù)據(jù)寬度進(jìn)行控制。

由于BRAM可以實(shí)現(xiàn)1、2、4、8、16 位的任意位寬,所以地址總線寬度、數(shù)據(jù)總線寬度都必須滿足其中任意一種模式下的要求。于是設(shè)計(jì)時(shí)使地址總線寬度為各種模式下的最大值,即1位時(shí)的地址寬度《11∶0》,其他模式下可使不用的地址位使能無效,進(jìn)而獲得所需的地址位。數(shù)據(jù)總線寬度也設(shè)置為各種情況下的最大值,即16 位時(shí)的數(shù)據(jù)寬度《15∶0》,其他情況下選擇有用的數(shù)據(jù)位進(jìn)行存儲(chǔ)。

表1可見WIDTH_SEL《0∶2》對地址使能的控制,主要在于對地址《11∶8》的控制,其他位地址《7∶0》則一直有效。

表1 不同數(shù)據(jù)位寬的地址使能

由WIDTH_SEL《0∶2》另外譯碼產(chǎn)生一組數(shù)據(jù)控制信號,分別為S_1、S_2、S_4、S_8、S_16 控制數(shù)據(jù)如何分配到位線上。這當(dāng)中* 根位線實(shí)行了分片,每片4 根:

S_1有效:DI《0》可分配到16片中的任何一片上。

S_2有效:DI《0∶1》可分配到《0∶1》、《2∶3》、《4∶5》?任何相鄰兩片上,每片1 位數(shù)據(jù)。

S_4有效:DI《0∶3》可分配到《0∶3》、《4∶7》、《8∶11》、《12∶15》任何相鄰四片上,每片1 位數(shù)據(jù)。

S_8 有效:DI《0∶7》可分配到《0∶7》或《8∶15》 8片上,每片1 位數(shù)據(jù)。

S_16 有效:DI《0∶15》剛好分配到16片上,每片1 位數(shù)據(jù)。

至于上述究竟存儲(chǔ)到哪些片上以及具體存儲(chǔ)到片內(nèi)哪根位線上則由列譯碼控制。

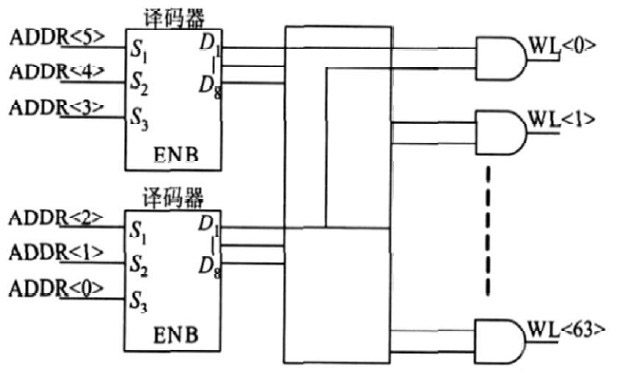

3.2.2 譯碼控制

行譯碼采用了常用的3-8 譯碼器,3-8 譯碼器內(nèi)由與門組成。第一級用兩個(gè)3-8 譯碼器,輸入端接入行地址ADDR《5∶0》,第二級用64 個(gè)與門把第一級譯碼進(jìn)一步譯出來,可實(shí)現(xiàn)64 行中選出1 行。

圖2 64 選1 行譯碼

列譯碼相對較復(fù)雜,首先將列地址分為兩組,一組用于片選譯,一組用于片內(nèi)譯碼。片選地址由ADDR《11∶8》組成,片內(nèi)譯碼由ADDR《7∶6》組成。

片選地址譯碼由地址和地址使能組成,而地址使能則是由WIDTH_SEL《0∶2》配置決定的。

圖3 片選譯碼

譯碼所得的A《11∶8》_DEC《0∶15》即可實(shí)現(xiàn)片選存儲(chǔ)。當(dāng)配置為1 位時(shí),4 位地址均有效,譯出的16位中只有1 位有效,只能選擇16 片中的1 片。當(dāng)配置為2 位時(shí),ADDR《11》使能無效,譯出16位中有連續(xù)2 位有效,能選擇16 片中連續(xù)2 片。當(dāng)配置為4 位時(shí),譯出16 位中有連續(xù)4 位有效,能選擇16 片中連續(xù)4 片。配置為8 位就能選擇16 片中的上8 片或下8 片。配置為16 位,4 個(gè)地址均無效,譯出的16 位全有效,16 片全選。經(jīng)過了片選的一級譯碼,列譯碼還需經(jīng)過第二級的片內(nèi)譯碼。

圖4 片內(nèi)譯碼

A《11∶8》_DEC與A7 譯碼均為低有效,A6譯碼為高有效。之所以能夠用或門譯碼,是因?yàn)闆]被譯碼的一對BL 和BLN 位線上的數(shù)據(jù)是不會(huì)被寫入存儲(chǔ)單元的,如A7《0》為1,A《11∶8》_DEC為1,BL《0》與BLN《0》均為1,即使字線打開了,它們也是不會(huì)被寫入存儲(chǔ)陣列的。而被譯碼選中的一對位線,BL與BLN 互補(bǔ),它們上的數(shù)據(jù)即可被寫入存儲(chǔ)單元。

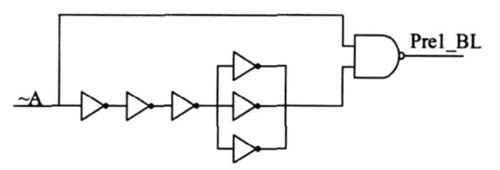

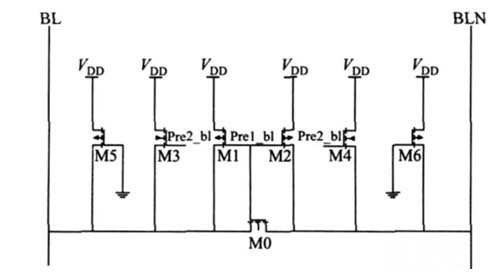

3.2.3 位線充電電路

對位線的充電共有兩對充電管和一對上拉管,寬長比在設(shè)計(jì)上也是有講究的。上拉管一直開啟,為倒比管。柵極接平衡管的M1 和M2 時(shí)序要求較高,因?yàn)樗鼈兊膶掗L比較大,為主要充電管。在BRAM總使能信號ENA和時(shí)鐘CLK有效時(shí)工作,進(jìn)行預(yù)充電。在CLK 下降沿,M1 和M2 短暫關(guān)閉可執(zhí)行讀操作。M1、M2和平衡管都在Pre1_BL信號控制下工作。

Pre1_BL 需在數(shù)據(jù)線與位線之間的開關(guān)管打開時(shí)關(guān)閉,不影響數(shù)據(jù)的讀操作。Pre1_BL信號受到數(shù)據(jù)線與位線的開關(guān)管控制信號A 的約束,圖4 的結(jié)構(gòu)即可避免Pre1_BL與A的時(shí)序沖突,在A有效時(shí),Pre1_BL無效,且當(dāng)A 關(guān)閉時(shí),Pre1_BL 延遲開啟。

而M3 和M4 管則由Pre2_BL信號控制,Pre2_BL由BRAM全局信號ENA、CLK 和WE 一起控制。由于BRAM 在進(jìn)行寫操作時(shí),也可鏡像地輸出寫入的數(shù)據(jù),即也做了讀操作。為了更好地在寫入時(shí)也讀出,且滿足頻率要求,有必要增加這一充電管。

圖5 Pre1_BL 信號產(chǎn)生電路

圖6 位線充電電路

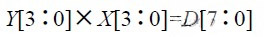

4 BRAM應(yīng)用

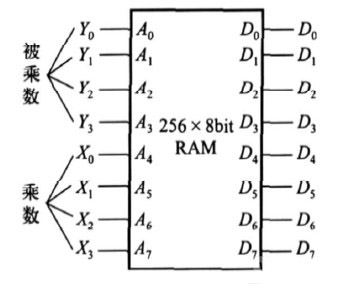

作為隨機(jī)存取存儲(chǔ)器,BRAM 除了實(shí)現(xiàn)一般的存儲(chǔ)器功能外,還可實(shí)現(xiàn)不同數(shù)據(jù)寬度的存儲(chǔ),且可用作ROM,以實(shí)現(xiàn)組合邏輯函數(shù)。當(dāng)初始化了BRAM后,一組地址輸入就對應(yīng)了一組數(shù)據(jù)的輸出,根據(jù)數(shù)據(jù)和地址的對應(yīng)關(guān)系,就能實(shí)現(xiàn)一定的函數(shù)功能,BRAM 之所以能實(shí)現(xiàn)函數(shù)邏輯,原因是它擁有足夠的存儲(chǔ)單元,可以把邏輯函數(shù)所有可能的結(jié)果預(yù)先存入到存儲(chǔ)單元中。如實(shí)現(xiàn)4 × 4 二進(jìn)制乘法器:

即由地址來查找數(shù)據(jù),如同LUT。在FPGA 中,還可用BRAM來實(shí)現(xiàn)FIFO中的存儲(chǔ)體模塊,CLB實(shí)現(xiàn)控制邏輯,設(shè)計(jì)緊湊,小巧靈活。

圖7 4 位乘法器

5 結(jié)論

如今系統(tǒng)越來越高級,數(shù)字電路也高度集成,存儲(chǔ)器也越來越多地應(yīng)用于嵌入式芯片中。本文設(shè)計(jì)了一種應(yīng)用于FPGA 的嵌入式存儲(chǔ)器結(jié)構(gòu),符合一般的雙端SRAM 功能,且具有FPGA 功能塊的可配置選擇,靈活性很高。