距離測(cè)量是測(cè)試技術(shù)中的一項(xiàng)基本測(cè)試技術(shù),,其幾乎貫穿于工程實(shí)踐的每個(gè)領(lǐng)域,。在軍事航天領(lǐng)域,由于其特殊的需求,,對(duì)測(cè)距系統(tǒng)的量程,、實(shí)時(shí)性和精度要求越來(lái)越高,而擴(kuò)頻測(cè)距由于其抗干擾能力強(qiáng),、精度高,、作用范圍廣,、隱蔽性好、適應(yīng)性強(qiáng),、全天候等優(yōu)勢(shì),,在測(cè)距系統(tǒng)中得到了重視。

擴(kuò)頻測(cè)距也稱偽碼測(cè)距,,它是采用一個(gè)較長(zhǎng)周期的PN碼序列作為發(fā)射信號(hào),,將它與目標(biāo)反射或轉(zhuǎn)發(fā)回來(lái)的PN碼序列的相位進(jìn)行比較,即比較兩個(gè)碼序列相差的碼片數(shù),,從而看出其時(shí)間差,,換算出發(fā)射機(jī)與目的地之間的距離。如果碼片選得很窄,,即碼速率做得很高,,那么就可以完成高精度的測(cè)距。但隨著碼速率的提高和碼周期的加長(zhǎng),,傳統(tǒng)的捕獲時(shí)間將達(dá)到不可容忍的地步,,所以需要考慮快速捕獲算法。

由擴(kuò)頻碼的自相關(guān)函數(shù)可知,,只有在t’=(t-τ)時(shí),,擴(kuò)頻解調(diào)輸出V(t)的信號(hào)最大。根據(jù)τ就能算出兩地的距離![]() ,,c為電磁波傳播速度,。

,,c為電磁波傳播速度,。

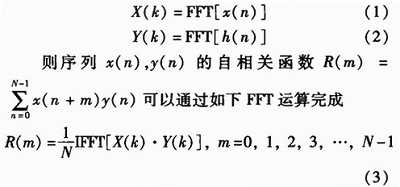

由于計(jì)算兩序列的自相關(guān)函數(shù)![]() 需要用循環(huán)卷積代替自相關(guān)函數(shù)來(lái)計(jì)算擴(kuò)頻測(cè)距系統(tǒng)中的碼片偏移,可以節(jié)省運(yùn)算時(shí)間(大約為1/114),,加快捕獲過(guò)程,。設(shè)x(n),y(n)分別為現(xiàn)有發(fā)射PN碼與反射回來(lái)的PN碼,,序列長(zhǎng)度為N,,對(duì)它們分別做N點(diǎn)FFT,記

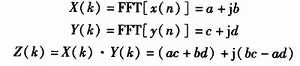

需要用循環(huán)卷積代替自相關(guān)函數(shù)來(lái)計(jì)算擴(kuò)頻測(cè)距系統(tǒng)中的碼片偏移,可以節(jié)省運(yùn)算時(shí)間(大約為1/114),,加快捕獲過(guò)程,。設(shè)x(n),y(n)分別為現(xiàn)有發(fā)射PN碼與反射回來(lái)的PN碼,,序列長(zhǎng)度為N,,對(duì)它們分別做N點(diǎn)FFT,記

可知R(m)為現(xiàn)有發(fā)射PN碼與反射回來(lái)的PN碼之間的相關(guān)值序列,,長(zhǎng)度為N,,可知當(dāng)R(m)中最大值的序列號(hào)減1即為碼片差。

1 仿真方案設(shè)計(jì)

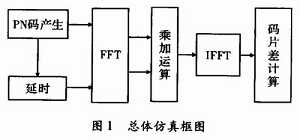

首先由m序列發(fā)生器產(chǎn)生出兩路序列長(zhǎng)度為N的PN碼,,其中一路經(jīng)過(guò)延時(shí)模塊以后與另一路分別進(jìn)入FFT模塊進(jìn)行FFT運(yùn)算,,將進(jìn)行FFT后的兩組數(shù)據(jù)運(yùn)算后進(jìn)入IFFT模塊得出序列組,由序列組得出兩路序列之間的碼片偏移數(shù),,從而算出其時(shí)延,。系統(tǒng)總體框圖如圖1所示。

2 主要模塊仿真結(jié)果

2.1 PH碼產(chǎn)生模塊

本設(shè)計(jì)選取的PN碼為63位,本征多項(xiàng)式為x6+x+1,。該P(yáng)N碼產(chǎn)生器由VHDL語(yǔ)言編寫,,其仿真結(jié)果如圖2所示。

2.2 FFT轉(zhuǎn)換模塊

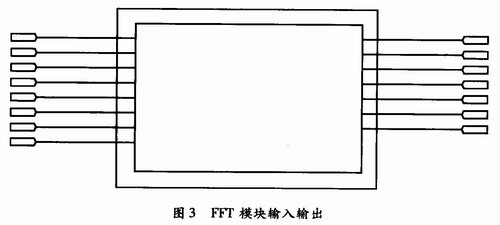

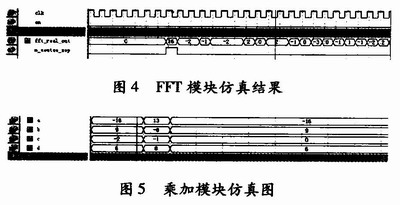

該模塊是本設(shè)計(jì)的核心模塊,,由輸入緩沖器,、FFT運(yùn)算器、控制器構(gòu)成,,完成對(duì)數(shù)據(jù)的FFT變換,。將PN碼發(fā)生器產(chǎn)生的數(shù)據(jù)存入輸入緩沖器中,在控制器的控制下,,F(xiàn)FT運(yùn)算模塊從輸入緩沖器中讀取出數(shù)據(jù)值進(jìn)行FFT變換,,然后得出輸出數(shù)據(jù)。圖3所示為FFT模塊的輸入輸出關(guān)系,。fft_imag_out,,fft_real_out分別為輸出數(shù)據(jù)的實(shí)部、虛部和修正因子,,m_soutoe_sop為輸出數(shù)據(jù)的起始位,。

2.3 計(jì)算模塊

設(shè)兩路信號(hào)進(jìn)行FFT后的數(shù)據(jù)為

可見對(duì)進(jìn)行FFT變換后需要進(jìn)行的運(yùn)算處理其實(shí)質(zhì)是一個(gè)乘加,一個(gè)乘減和一個(gè)加法運(yùn)算,,其中乘加運(yùn)算仿真結(jié)果如圖4,、圖5所示。

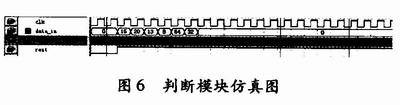

2.4 判斷模塊

判斷模塊的主要功能是對(duì)IFFT后的序列的最大值進(jìn)行判斷,,得出其最大值所在的序列號(hào)減1就為其碼片差τ,。clk為時(shí)鐘信號(hào),rest為開始信號(hào),,data_in為輸入數(shù)據(jù),data_out為輸入數(shù)據(jù)data_in中最大值所在的序列號(hào)減1,。圖6為判斷模塊仿真結(jié)果,。

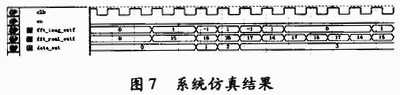

2.5 系統(tǒng)總設(shè)計(jì)圖及仿真結(jié)果

本設(shè)計(jì)采用自頂向下的設(shè)計(jì)方法,利用VHDL語(yǔ)言描述出擴(kuò)頻測(cè)距快速捕獲的各個(gè)功能模塊,。圖7所示為總體仿真結(jié)果,,圖中fft_imag_ outf,fft_real_outf為ifft后的數(shù)據(jù),,data_out為輸出數(shù)據(jù),,由此可見,仿真結(jié)果與設(shè)定的τ=3一樣,,驗(yàn)證了本設(shè)計(jì)的可行性,。

3 結(jié)束語(yǔ)

采用FFT代替自相關(guān)函數(shù)計(jì)算擴(kuò)頻系統(tǒng)中的碼片偏移可節(jié)省硬件計(jì)算時(shí)間。經(jīng)過(guò)硬件的優(yōu)化設(shè)計(jì)與仿真,,在Altera Straix II系列FPGA上,,時(shí)鐘頻率達(dá)到109.1 MHz,,捕獲時(shí)間和計(jì)算時(shí)間大約在2μs,捕獲時(shí)間提高,。此外,,由于擴(kuò)頻技術(shù)可以極大地抑制突發(fā)干擾和脈沖干擾,所以擴(kuò)頻測(cè)距比起傳統(tǒng)的測(cè)距方法,,如激光測(cè)距,,超聲測(cè)距等方法能適用于更惡劣的環(huán)境,如衛(wèi)星測(cè)控,,而由于使用快速捕獲技術(shù),,可進(jìn)一步提高實(shí)時(shí)性,在對(duì)測(cè)距實(shí)時(shí)性要求更高的引信技術(shù)中也可以采用,。