摘要:為了取代傳統(tǒng)利用單片機驅動微型打印機,使用Altera公司的FPGA芯片EP3C225Q240C8N設計驅動打印機的硬件控制電路,并正確控制微型打印機的工作時序。軟件使用硬件描述語言VHDL實現(xiàn)對微型打印機的時序控制,并通過QuartusⅡ軟件平臺下栽到FPGA調(diào)試通過,證明該方法行之有效,完全可以取代傳統(tǒng)利用單片機來驅動微型打印機,且抗干擾性好,可靠性高,具有較強的可移植性。

關鍵詞:微型打印機;VHDL;時序;FPGA

0 引言

FPGA即現(xiàn)場可編程邏輯陣列。是在CPLD的基礎上發(fā)展起來的新型高性能可編程邏輯器件。FPGA的集成度很高,其器件密度從數(shù)萬門到數(shù)千萬門不等,可以完成極其復雜的時序與組合邏輯電路功能,適用于高速、高密度的高端數(shù)字邏輯電路設計領域。新一代的FPGA甚至集成了中央處理器(CPLU)或數(shù)字處理器(DSP)內(nèi)核,在一片F(xiàn)PGA上進行軟硬件協(xié)同設計,為實現(xiàn)片上可編程系統(tǒng)(SOPC)提供了強大的硬件支持。對微型打印機的驅動,傳統(tǒng)方法是使用單片機是實現(xiàn)對其的時序控制。隨著FPGA在各領域的普及使用,以及對微型打印機的需要,因此要實現(xiàn)FP-GA對微型打印機的時序控制。

當前各ASIC芯片制造商都相繼開發(fā)了用于各自目的的HDL語言,但是大多數(shù)都為標準化和通用化。惟一被公認的是美國國防部開發(fā)的VHDL語言,它已成為IEEE STD_1076標準。另外從近期HDL語言發(fā)展的動態(tài)來看,許多公司研制的硬件電路設計工具業(yè)都逐漸向VHDL語言靠攏,使得他們的硬件電路設計工具也能支持VHDL語言。

VHDL語言可以支持自上而下和基于庫的設計方法,而且還支持FPGA的設計。

1 微型打印機簡介

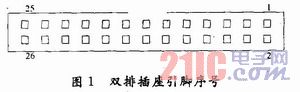

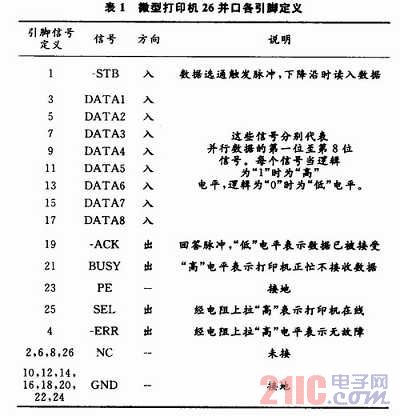

RD-DH型微型打印機采用熱敏加熱點陣打印方式,是一款體積小,打印速度快的打印輸出設備。該型打印機可采用標準并行接口,RS232串行接口,TTL電平串口,485接口,USB接口,打印速度達到50 m/s,分辨率為8點/mm,384點/行,打印紙張采用57 mm熱敏紙。可打印國標一、二級漢字庫中全部漢字和西文字、圖標共8 178個。微型打印機并行接口與CENTRONICS標準接口兼容,可直接由微機并口或單片機控制。其26線雙排插座引腳序號如圖1所示。此26個并口各引腳信號定義如表1所示。

注:“入”表示輸入到打印機;“出”表示從打印機輸出,信號的邏輯電平為TTL電平。

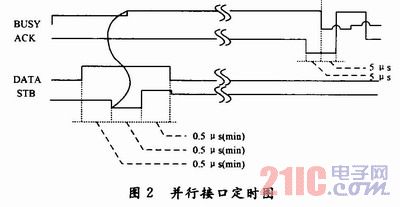

對打印機的驅動主要是對其工作時序進行正確的控制,RD-DH型并行接口定時圖如圖2所示。

2 總體系統(tǒng)設計

使用Altera公司的CyelonⅢ系列的FPGA芯片EP3C25Q240C8N實現(xiàn)對RD-DH型微型打印機的硬件電路控制,使用QuartusⅡ開發(fā)工具,通過VHDL語言實現(xiàn)對微型打印機的軟件功能實現(xiàn)。

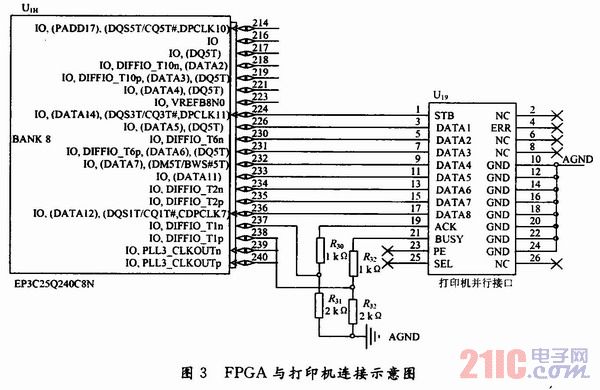

2.1 硬件電路設計

如圖3所示為打印機與FPGA的連接示意圖。DATA1~DATA8表示打印機的8個數(shù)據(jù)位,他們的邏輯‘1’表示高電平,邏輯‘O’表示低電

平;-STB為數(shù)據(jù)選通觸發(fā)脈沖,下降沿時讀入數(shù)據(jù);-ACK為回答脈沖,低電平表示數(shù)據(jù)已被接受;BUSY為高電平時表示打印機正忙,此時不接收數(shù)據(jù)。由于-ACK和BUSY輸出的是5 V的TTL電平,而FPGA的I/O口標準為3.3 V LVCMOS電平,因此這兩個信號作為FPGA的輸入信號時,要進行分壓,保證電路正常運行。

2.2 軟件設計

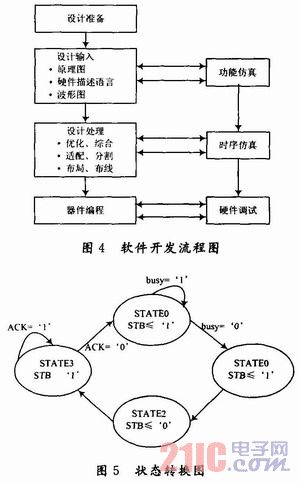

軟件平臺采用Altera公司的FPGA開發(fā)平臺QuartusⅡ。QuartusⅡ提供了一種與器件結構無關的設計環(huán)境,設計者不需要精通器件的內(nèi)部結構,只需要運用自己熟悉的輸入工具(如原理圖輸入或數(shù)字電路描述語言輸入)進行設計,利用QuartusⅡ可以將這些設計轉換為最終結構所需要的格式。有關結構的詳細知識已寫入開發(fā)工具軟件,設計人員無需手工優(yōu)化自己的設計。軟件的開發(fā)流程如圖4所示。

使用VHDL硬件描述語言來進行軟件設計。對微型打印機的驅動主要是對其工作時序進行正確的控制,利用VHDL常見的狀態(tài)機來實現(xiàn)對打印機的工作時序的控制,根據(jù)時序圖1所示的時序,狀態(tài)機使用4個狀態(tài),狀態(tài)轉換圖如圖5所示。

初始狀態(tài)STATE0時,數(shù)據(jù)選通觸發(fā)脈沖信號STB置‘1’(高電平),檢測打印機是否正忙,如果打印機為空閑狀態(tài)(busy=‘0’),轉入下一狀態(tài)STATE1,否則(busy=‘1’)繼續(xù)執(zhí)行STATE0;在狀態(tài)STATE1,將數(shù)據(jù)寫入打印機,直接轉入下一狀態(tài);在狀態(tài)STATE2,將數(shù)據(jù)選通觸發(fā)脈沖信號STB置‘O’,打印機讀數(shù)據(jù),轉入下一狀態(tài);在狀態(tài)STATE3,檢測數(shù)據(jù)是否已經(jīng)被接受,若數(shù)據(jù)已被接受(ACK=‘O’),打印機轉入初始狀態(tài)STATE0,等待接受新數(shù)據(jù),若數(shù)據(jù)未被接受(ACK=‘1’),繼續(xù)執(zhí)行STATE3直到數(shù)據(jù)被接受。

3 結語

使用FPGA與VHDL硬件描述語言設計的微型打印機驅動,通過系統(tǒng)調(diào)試能夠完成對打印機的時序控制,目前已經(jīng)在某型測試儀中正常使用。該設計系統(tǒng)控制簡單,抗干擾性強,可靠性高,移植性較好,能夠用于任何使用FPGA芯片的系統(tǒng)中,具有一定的應用前景。