0 引 言

直接數(shù)字頻率合成( Dir ect Dig ital Frequency Synthesis,DDS) 是一種新型的頻率合成技術(shù),它把信號發(fā)生器的頻率穩(wěn)定度、準(zhǔn)確度提高到與基準(zhǔn)頻率相同的水平,并且可以在很寬的頻率范圍內(nèi)進(jìn)行精細(xì)的頻率調(diào)節(jié)。在現(xiàn)代通信領(lǐng)域中,DDS 的應(yīng)用極其廣泛。實(shí)現(xiàn)DDS 常用的方法是采用專用的DDS 芯片,控制部分采用獨(dú)立的MCU ,這樣設(shè)計(jì)出來的系統(tǒng)的集成度和擴(kuò)展性不盡人意。隨著大規(guī)模現(xiàn)場可編程門陣列的推出,SOPC 的不斷發(fā)展,設(shè)計(jì)人員可以在FPGA 的嵌入式軟核處理器上設(shè)計(jì)各種系統(tǒng),滿足用戶需求。本文基于SOPC 技術(shù)設(shè)計(jì)直接數(shù)字頻率合成器,選用A ltera公司的新一代FPGA( Cyclone Ⅱ) 為核心,利用FPGA的邏輯單元實(shí)現(xiàn)相位累加等數(shù)字邏輯功能,在ROM 中分別放入正弦表、方波表、三角波" title="三角波">三角波表、鋸齒波" title="鋸齒波">鋸齒波表,用軟核CPU 做控制,實(shí)現(xiàn)頻率、相位、波形選擇等。這樣可以大大減小處理器外圍擴(kuò)展電路數(shù)目,還提高了系統(tǒng)的穩(wěn)定性和抗干擾能力,節(jié)省了內(nèi)部資源。

1 系統(tǒng)方案設(shè)計(jì)

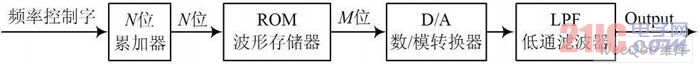

系統(tǒng)采用SOPC 設(shè)計(jì)方案。整體系統(tǒng)框圖如圖1所示,它由頻率預(yù)置電路、波形選擇、波形頻率控制、累加器" title="累加器">累加器、存儲波形數(shù)據(jù)的存儲器和D/ A 轉(zhuǎn)換電路、濾波電路組成。累加器模塊由10 位加法器與10 位寄存器級聯(lián)而成。波形存儲器中放入正弦波" title="正弦波">正弦波、方波、三角波、鋸齒波的數(shù)據(jù)。

圖1 整體系統(tǒng)框圖

1. 1 DDS 基本工作原理

DDS 的基本原理是利用采樣定理,通過查表法產(chǎn)生波形。一個完整DDS 結(jié)構(gòu)圖如圖2 所示。

圖2 DDS 結(jié)構(gòu)圖

相位累加器在每一個時鐘上升沿與頻率控制字K累加一次,當(dāng)累加器計(jì)數(shù)大于2N 時,相位累加器相當(dāng)于進(jìn)行一次取模運(yùn)算。在每一個時鐘周期內(nèi),根據(jù)送給ROM 的地址,取出ROM 中與該地址相對應(yīng)的波形的數(shù)據(jù),讀取出ROM 中的數(shù)據(jù)后通過D/ A 轉(zhuǎn)換器,將數(shù)字量轉(zhuǎn)換成模擬量,通過低通濾波電路,可輸出一個平滑的波形。

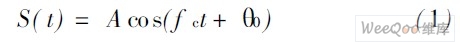

假設(shè)頻率為f c 的載波,它的時域表達(dá)式為:

其相位表達(dá)式為:

輸出頻率f 0 與時鐘頻率f clk之間的關(guān)系滿足:

當(dāng)K = 1 時,DDS 有最小頻率輸出,因此DDS 的步長為f clk / 2N ,最大輸出頻率為f clk / 2。在本設(shè)計(jì)中,將N 設(shè)定為10 位,M 設(shè)定為12 位,相位累加器在時鐘的控制下,以步長K 進(jìn)行累加,輸出N 位二進(jìn)制碼,并以其作為波形ROM 的地址,對波形存儲器ROM 尋址,波形存儲器ROM 輸出的數(shù)據(jù)經(jīng)過D/ A 轉(zhuǎn)換成階梯波后,經(jīng)過低通濾波器平滑后,便得到合成后的波形了,合成后的波形形狀取決于波形選取和ROM 中的數(shù)據(jù)。

1. 2 D/ A 轉(zhuǎn)換器

從DDS 核輸出的是一個數(shù)字信號,需要將數(shù)字信號轉(zhuǎn)換成模擬信號,才能便于觀察。DAC 有電壓和電流輸出兩種,其輸出的信號并不能真正連續(xù)可變,而是以其絕對分辨率為最小單位,所以它的輸出實(shí)際上是一個階梯模擬信號,所以需要將D/ A 輸出的信號通過低通濾波器平滑后得到純凈的模擬信號。在該設(shè)計(jì)中用到型號為AD9742 的D/ A 轉(zhuǎn)換器,AD9742 是具有12 位、低功耗、轉(zhuǎn)換速度可達(dá)到100 Mb/ s 的D/ A 轉(zhuǎn)換器。

1. 3 基于SOPC 的硬件架構(gòu)

系統(tǒng)開發(fā)包括硬件部分和軟件部分,而硬件部分是由SOPC 開發(fā)工具搭建而成。SOPC Builder 生成NIOS 嵌入式處理器,NIOS 嵌入式處理器開發(fā)工具允許用戶配置多個CPU ,在標(biāo)準(zhǔn)庫中添加外圍電路,也可以由用戶自定義外設(shè),綜合處理自定義系統(tǒng),這樣使設(shè)計(jì)變得更加靈活。

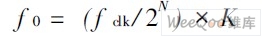

打開SOPC Builder 后分別添加CPU,PIO 輸入( 10 個按鍵用作頻率字的輸入、1 個按鍵用作確認(rèn)、4 個按鍵用作波形的選擇) ,存儲器( FLASH,SRAM 和SDRAM) ,PIO 輸出( 10 位作為ROM 的地址、2 位作為ROM 塊的選擇、7 位為LED 段碼、1 位為LED 的選通端) 和定時器。所有組件添加完后的硬件架構(gòu)圖如圖3 所示。

圖3 SOPC 硬件架構(gòu)圖

SOPC Builder 生成之后,在Quartus 軟件中可以添加生成之后的CPU 模塊,而DDS 模塊是用VHDL 語言編寫而成,DDS 模塊圖如圖4 所示。其中的ROM 大小為12 1 024,共設(shè)置4 塊ROM 分別存儲正弦波、方波、三角波、鋸齒波。波形數(shù)據(jù)是由Mat lab軟件計(jì)算出來的,并將數(shù)據(jù)以. mif 文件格式存儲。累加器的輸出為波形存儲器的地址,進(jìn)行波形的相位 幅值轉(zhuǎn)換后,作為輸出的波形的幅值。10 位的尋址ROM 相當(dāng)于將一個周期的信號進(jìn)行離散化,形成具有1 024 個樣值的序列。累加器產(chǎn)生的地址通過波形的地址分配讀取不同存儲器中的數(shù)據(jù),然后將讀出來的數(shù)據(jù)經(jīng)過D/ A 轉(zhuǎn)換器,轉(zhuǎn)換成模擬信號輸出。

圖4 DDS 模塊圖

2 軟件設(shè)計(jì)

NIOS 完整的開發(fā)環(huán)境是NIOS 處理器與用戶的接口界面。使用NIOS IDE 可以完成所有的軟件開發(fā)任務(wù),包括程序的編輯,編譯和調(diào)試。硬件提取層( HAL) 支持通用I/ O 器件,可以通過編寫標(biāo)準(zhǔn)C 程序訪問硬件,HA L 減少了對硬件寄存器的訪問,直接與外圍器件進(jìn)行通信或控制。不同的外圍硬件需要不同程度的HAL 的支持,需要運(yùn)行HAL 的軟件驅(qū)動器。DDS 系統(tǒng)控制在NIOS IDE 環(huán)境下用標(biāo)準(zhǔn)C 語言實(shí)現(xiàn),通過編寫代碼、編譯、鏈接、調(diào)試、下載幾個步驟完成整個設(shè)計(jì)。

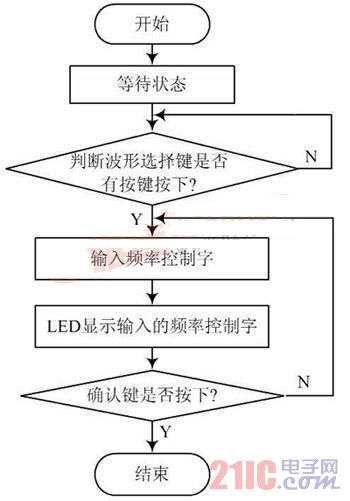

打開IDE 開發(fā)環(huán)境后,第一步需要做的就是新建一個工程,將SOPC Builder 生成的. ptf 添加之后,系統(tǒng)根據(jù)該硬件的地址分配情況自動生成相應(yīng)的頭文件,該頭文件定義了各個組件的基地址。當(dāng)SOPC 系統(tǒng)發(fā)生變化,IDE 將在用戶編譯和運(yùn)行應(yīng)用程序時重新對HAL 進(jìn)行編譯。整個軟件編寫的流程圖如圖5 所示。

圖5 軟件流程圖

3 系統(tǒng)調(diào)試過程與結(jié)果

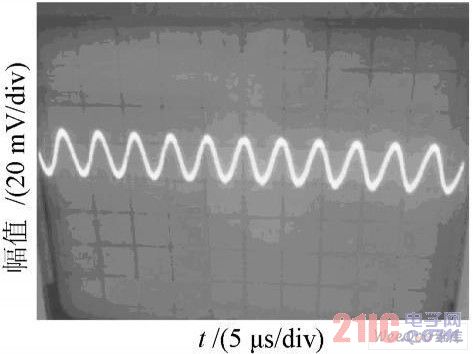

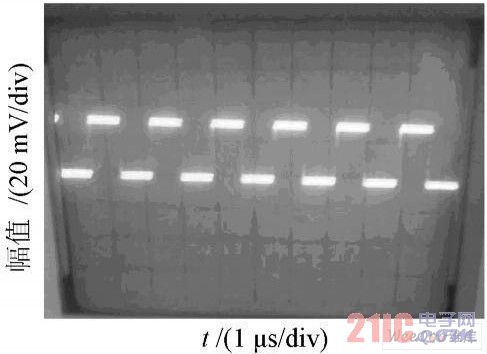

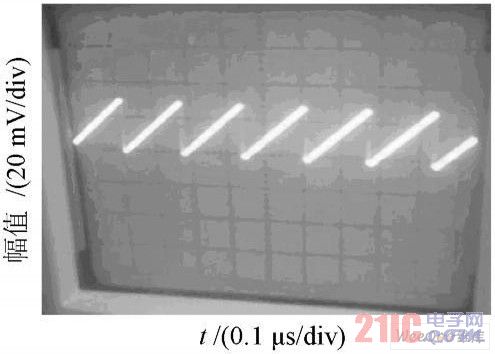

系統(tǒng)時鐘為50 MHz,當(dāng)波形選擇鍵選為正弦波,頻率字設(shè)置為5 時,數(shù)碼管上顯示5,按下確認(rèn)鍵后,數(shù)碼管顯示”-“,通過示波器,可以觀察到輸出波形如圖6所示,橫軸為時間檔,縱軸為幅值。當(dāng)波形選擇鍵選為方波,頻率字設(shè)置為10 時,數(shù)碼管上先顯示1,后顯示0,按下確認(rèn)鍵之后,數(shù)碼管顯示“-”,這樣在示波器上觀察到的波形如圖7 所示。按照上面的操作過程,三角波和鋸齒波的波形分別如圖8,圖9 所示。

圖6 正弦波波形

圖7 方波波形

圖8 三角波波形

圖9 鋸齒波波形

4 結(jié) 論

本文所設(shè)計(jì)的是頻率字的預(yù)置與波形的選擇,是通過鍵盤輸入的,因此能夠得到規(guī)定范圍內(nèi)的任意頻率的波形,這樣可以很好地滿足變頻信號的情況,實(shí)用性較強(qiáng)。實(shí)驗(yàn)所調(diào)試出的波形清晰,干擾小。采用SOPC 方法實(shí)現(xiàn),使設(shè)計(jì)變得非常靈活。該設(shè)計(jì)只實(shí)現(xiàn)了任意頻率的波形輸入,還需要實(shí)現(xiàn)相位累加,設(shè)計(jì)才會變得更加完美。