1 設(shè)計(jì)要求

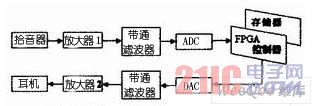

設(shè)計(jì)并制作一個(gè)數(shù)字化語(yǔ)音存儲(chǔ)" title="語(yǔ)音存儲(chǔ)">語(yǔ)音存儲(chǔ)與回放系統(tǒng),,其示意圖如圖1所示。

圖1 數(shù)字化語(yǔ)音存儲(chǔ)與回放系統(tǒng)示意圖

(1)放大器1的增益為46dB,,放大器2的增益為40dB,,增益均可調(diào);

(2)帶通濾波器:通帶為300Hz~3.4kHz;

(3)ADC:采樣頻率fs=8kHz,,字長(zhǎng)=8位,;

(4)語(yǔ)音存儲(chǔ)時(shí)間≥10s;

(5)DAC:變換頻率fc=8kHz,,字長(zhǎng)=8位,;

(6)回放語(yǔ)音質(zhì)量良好。

不能使用單片語(yǔ)音專用芯片實(shí)現(xiàn)本系統(tǒng),。

2 數(shù)字化語(yǔ)音存儲(chǔ)與回放系統(tǒng)硬件電路

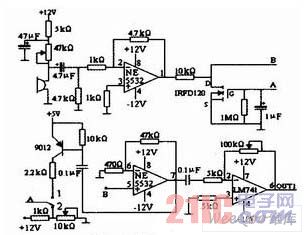

2.1 放大器1即音頻信號(hào)放大電路

音頻信號(hào)放大電路如圖2所示,。第一級(jí)放大(-4.7)倍。IRD120實(shí)現(xiàn)自動(dòng)增益控制,,當(dāng)開(kāi)關(guān)打到1的位置是增益自動(dòng)控制,,當(dāng)開(kāi)關(guān)打到2的位置是手動(dòng)控制。增益自動(dòng),、手動(dòng)控制是利用場(chǎng)效應(yīng)管工作在可變電阻區(qū),,漏源電阻受柵源電壓控制的特性。第二級(jí)放大(+101)倍,。第三級(jí)放大倍數(shù)可調(diào),,最大(-20)倍,保證ADC0809滿量程轉(zhuǎn)換,。

圖2 音頻信號(hào)放大電路

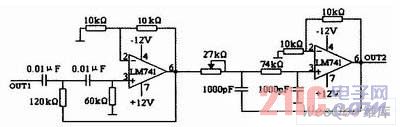

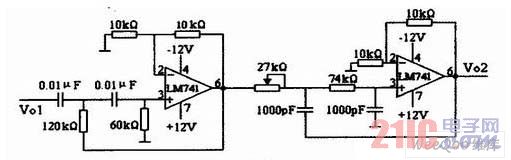

2.2 帶通濾波器

帶通濾波器如圖3所示,。實(shí)測(cè)帶通300~3300Hz。保證語(yǔ)音信號(hào)不失真地通過(guò)濾波器,,濾除帶外的低頻信號(hào)和高次諧波,。

圖3 帶通濾波器

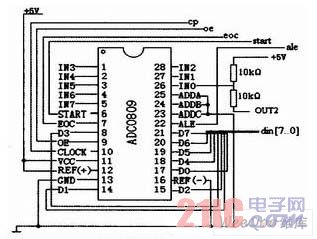

2.3 模數(shù)轉(zhuǎn)換(ADC)電路

ADC電路如圖4所示。題目要求采樣頻率fs=8kHz,,字長(zhǎng)=8位,,可選擇轉(zhuǎn)換時(shí)間不超過(guò)125 μs的8位A/D轉(zhuǎn)換芯片,ADC0809的轉(zhuǎn)換時(shí)間為100μs,,可選用ADC0809,。音頻信號(hào)經(jīng)過(guò)放大,、濾波送給ADC0809 ADC電路,,將模擬量轉(zhuǎn)換為數(shù)字量,再經(jīng)可編程器件送給存儲(chǔ)芯片,。cp,、oe、eoc,、start,、ale、din[7..0]接圖9。

圖4 ADC電路

2.4 語(yǔ)音存儲(chǔ)電路

存儲(chǔ)芯片HM628128D管腳如圖5所示,。HM628128D可存儲(chǔ)8位131072字,,5V供電,靜態(tài)RAM,。語(yǔ)音存儲(chǔ)時(shí)間≥10s,。HM628128D在數(shù)字化語(yǔ)音存儲(chǔ)與回放系統(tǒng)硬件電路中的接線如表1所示。HM628128D讀寫功能如表2所示,。

圖5 HM628128D管腳

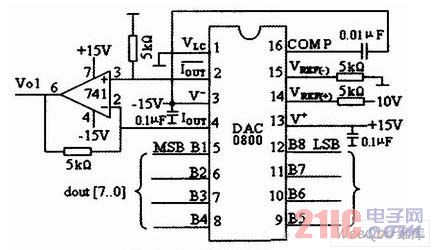

2.5 數(shù)模轉(zhuǎn)換(DAC)電路

DAC如圖6所示,。題目要求變換頻率fc=8kHz,字長(zhǎng)=8位,,可選擇轉(zhuǎn)換時(shí)間不超過(guò)125μs的8位D/A轉(zhuǎn)換芯片,,DAC0800的轉(zhuǎn)換時(shí)間為100ns,可選用DAC0800,。存儲(chǔ)芯片輸出的數(shù)字量經(jīng)可編程器件圖9送給DAC0800 DAC電路,,將數(shù)字量轉(zhuǎn)換為模擬量。

圖6 DAC0800 DAC電路

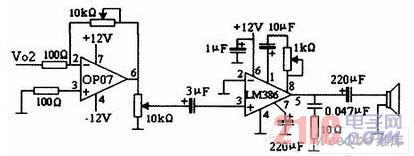

2.6 帶通濾波器和功率放大器

帶通濾波器2如圖7所示,。放大器2和功率放大器如圖8所示,。圖6、圖7,、圖8連接起來(lái)就可以獲得音頻信號(hào),。

圖7 帶通濾波器2

圖8 放大器2和功率放大器

3 數(shù)字化語(yǔ)音存儲(chǔ)與回放系統(tǒng)軟件電路

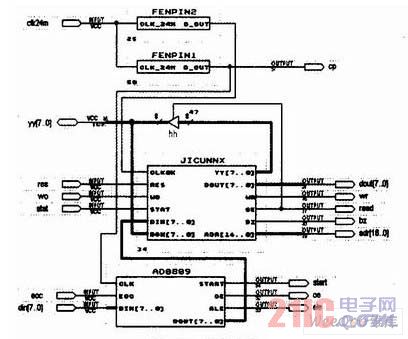

3.1 FPGA" title="FPGA">FPGA外部接線

FPGA外部接線如圖9所示。clk24m接24MHz晶振,,cp接圖4 ADC0809 ADC電路,,yy[7..0]接圖1.5 HM628128D,res接按鍵開(kāi)關(guān)res為0時(shí)地址復(fù)位為0,,wo接高低電平開(kāi)關(guān)wo為0錄音wo為1放音,,stat接高低電平開(kāi)關(guān),開(kāi)始錄音或放音,。dout[7..O]接圖6,,wr、read,、adr[16..O]接圖5HM628128D,,bz接發(fā)光指示燈顯示錄音或放音工作狀態(tài),其余端接圖4 ADC0809 ADC電路,。

圖9 FPGA外部接線

4 結(jié)論

此課題的創(chuàng)新點(diǎn)在于用FPGA控制數(shù)字化語(yǔ)音存儲(chǔ)與回放,,取代了以往用單片機(jī)去控制;同時(shí)此課題綜合了數(shù)電,、模電,、DAC,、CAD、FPGA等多方面電子知識(shí),,對(duì)學(xué)生做課程設(shè)計(jì),、電子實(shí)驗(yàn)有著很大的實(shí)用性。同時(shí)此課題可作為產(chǎn)品開(kāi)發(fā),,成本低,、可靠性高,將會(huì)有一定的市場(chǎng)。