摘要:為了提高系統(tǒng)的集成度和可靠性,降低功耗和成本,增強系統(tǒng)的靈活性,提出一種采用非常高速積體電路的硬件描述語言(VHDL語言)來設(shè)計數(shù)字基帶傳輸系統(tǒng)的方法。詳細闡述數(shù)字基帶傳輸系統(tǒng)中信號碼型的設(shè)計原則,數(shù)字基帶傳輸系統(tǒng)中信號編碼原理和譯碼原理;采用硬件描述語言來設(shè)計數(shù)字基帶信號編碼器和譯碼器并進行仿真;采用原理圖設(shè)計方法設(shè)計數(shù)字基帶傳輸系統(tǒng)并仿真;整個系統(tǒng)的設(shè)計在Quar-tusⅡ平臺上完成,并在Altera公司的ACEX1K-EP1K30TC144-1芯片上實現(xiàn)。

關(guān)鍵詞:數(shù)字通信;基帶傳輸系統(tǒng);VHDL;FPGA

0 引言

現(xiàn)代通信系統(tǒng)中,數(shù)字通信系統(tǒng)所占的比例越來越大,系統(tǒng)的數(shù)字化、集成化是未來發(fā)展的方向。隨著超大規(guī)模集成電路的誕生,各種數(shù)字通信的專用芯片也相繼問世,電路的集成化程度越來越高,設(shè)備的體積也越來越小,但是這些數(shù)字通信的專用芯片在價格上非常昂貴,給通信設(shè)備成本帶來很大壓力。近幾年,FPGA(Field Programmable Gate Array)的推出,給數(shù)字通信電路的設(shè)計帶來了更多的方便,擺脫了數(shù)字通信專用芯片功能單一、價格昂貴的缺點。目前實際的數(shù)字通信系統(tǒng)中,數(shù)字基帶系統(tǒng)在應(yīng)用上雖不如數(shù)字頻帶傳輸系統(tǒng)廣泛,但仍有相當多的應(yīng)用范圍。因此,本文設(shè)計的方案采用FPGA來實現(xiàn)數(shù)字基帶傳輸系統(tǒng)。

1 數(shù)字基帶信號編、譯碼原理

數(shù)字信號的傳輸方式有兩種:一種是基帶傳輸,另一種是頻帶傳輸。在基帶傳輸系統(tǒng)中,因為信道往往存在隔直流電容或耦合變壓器,使得基帶信號中的低頻和直流成分難于通過。因此,并非所有原始基帶數(shù)字信號都能在信道中傳輸。為了在傳輸信道中獲得優(yōu)良的傳輸特性,一般要將信號變換成適合于信道傳輸特性的傳輸碼(又叫線路碼),即進行適當?shù)拇a型變換。

通常,在設(shè)計數(shù)字基帶信號碼型時應(yīng)考慮以下原則:

(1)碼型中低頻、高頻分量盡量少;

(2)碼型中應(yīng)包含定時信息,以便定時提取;

(3)碼型變換設(shè)備要簡單可靠;

(4)碼型具有一定檢錯能力,若傳輸碼型有一定的規(guī)律性,就可根據(jù)這一規(guī)律性來檢測傳輸質(zhì)量,以便做到自動檢測;

(5)編碼方案對發(fā)送消息類型不應(yīng)有任何限制,適合于所有的二進制信號,這種與信源統(tǒng)計特性無關(guān)的特性稱為對信源具有透明性;

(6)低誤碼增殖,誤碼增殖是指單個數(shù)字傳輸錯誤在接收端解碼時,造成錯誤碼元的平均個數(shù)增加,從傳輸質(zhì)量要求出發(fā),希望它越小越好;

(7)高的編碼效率。

以上幾點并不是任何基帶傳輸碼型均能完全滿足的,常常是根據(jù)實際要求滿足其中的一部分。

數(shù)字基帶信號碼型種類繁多,其中HDB3碼(High Density Bipolar),即三階高密度雙極性碼,具有不含直流成分,低頻成分少,提取同步時鐘方便,有內(nèi)在檢錯能力等優(yōu)點,成為廣泛應(yīng)用于基帶傳輸系統(tǒng)中的碼型。ITU-T G.703規(guī)定2 Mb/s,8 Mb/s和34 Mb/s的數(shù)字接口均采用HDB3碼,因此以HDB3碼為例進行分析。

HDB3碼又稱四連“0”取代碼,它是AMI(Alternative Mark Inverse,傳號交替反轉(zhuǎn))碼的改進型。在AMI碼中,如果連續(xù)的較長的一段序列為“0”碼,則接收端會因為長時間無交替變化波形的控制而失去同步信號,而HDB3碼克服了AMI碼的上述缺點。此外,HDB3碼還具有頻譜能量主要集中在基波頻率以下,占用頻帶較窄等特點。

1.1 編碼原理

在消息的二進制代碼序列中:

(1)當連“0”碼的個數(shù)不大于3時,編碼規(guī)則為“1”碼變?yōu)?ldquo;+1”、“-1”交替脈沖,“0”碼仍為“0”。

(2)當代碼序列中出現(xiàn)4個連“0”碼或超過4個連“0”碼時,把連“0”段按4個“0”分節(jié),即“0000'’,并使第4個“0”碼變?yōu)?ldquo;1”碼,用V脈沖表示,這樣可以消除長連“0”現(xiàn)象。為了便于識別V脈沖,使V脈沖極性與前一個“1”脈沖極性相同,這樣就破壞了AMI碼極性交替的規(guī)律,所以V脈沖為破壞脈沖,把V脈沖和前3個連“0”稱為破壞節(jié)“000V”。

(3)為了使脈沖序列仍不含直流分量,則必須使相鄰的破壞點V脈沖極性交替。

(4)為了保證(2),(3)兩個條件的成立,必須使相鄰的破壞點之間有奇數(shù)個“1”碼。如果原序列中破壞點之間的“1”碼為偶數(shù)個,則必須補為奇數(shù),即將破壞節(jié)中的第一個“0”碼變?yōu)?ldquo;1”,用B脈沖表示,這時的破壞節(jié)變?yōu)?ldquo;B00V”形式。B脈沖極性與前一個“1”脈沖極性相反,而B脈沖極性與V脈沖極性相同。

1.2 譯碼原理

雖然編碼規(guī)則比較復雜,但是它的譯碼原理卻比較簡單。從上述編碼原理看出,每一個破壞符號V總是與前一非0符號同極性(包括B在內(nèi))。這就是說,在接收端譯碼時,由兩個相鄰的同極性碼找到破壞脈沖V,同極性碼中后面那個碼就是V碼。由V碼向前的第三個碼如果不是0碼,表明它是B碼,把V碼和B碼去掉后留下的都是信碼,再進行全波整流,將所有的-1變成+1后就得到原消息代碼。

2 編、譯碼模塊的設(shè)計與仿真

編、譯碼模塊的設(shè)計是在QuartusⅡ軟件開發(fā)平臺上,采用VHDL語言來實現(xiàn)的。

2.1 編碼模塊的設(shè)計

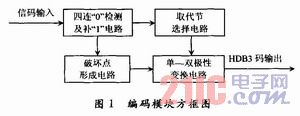

編碼模塊的方框圖如圖1所示。

四連“0”檢測及補“1”電路 根據(jù)編碼規(guī)則,當輸入的信號遇到四連“0”碼的時候,四連“0”碼將由取代節(jié)“B00V”或者“000V”取代。因此,首先要檢測出哪些是四連“0”碼,哪些是非四連“0”碼。在檢測出四連“0”碼后,還要將破壞脈沖V加入在第四個0的位置上。

取代節(jié)選擇電路 當需要用取代節(jié)代替四連“0”碼時,應(yīng)判斷采用哪一種取代節(jié),即選擇四連“0”碼中第一個0碼變?yōu)锽碼,還是變?yōu)?碼。如果傳號數(shù)為奇數(shù),采用“000V”取代;如果傳號數(shù)為偶數(shù),則采用“B00V”取代。

破壞點形成電路 將補放的“1”碼變成破壞點,使后續(xù)的V碼與前面相鄰的“1”碼極性相同,破壞了交替反轉(zhuǎn)的規(guī)律,形成了破壞點。

單—雙極性變換電路 HDB3碼極性形成電路有兩個功能:一是正常傳號“B”正負交替極性的形成;二是破壞點“V”脈沖的正負交替極性的形成,并輸出HDB3碼。

2.2 譯碼模塊的設(shè)計

譯碼模塊的方框圖如圖2所示。

破壞點檢測電路 即找V碼,在s消息的二進制代碼中,若找出相鄰兩個同極性的碼元,則可以確定后一個碼元必為V碼。

取代節(jié)去除電路 在V碼出現(xiàn)時刻將信碼流中的V碼及其前面的第三位碼置為“0”,即去掉取代節(jié)。

雙—單極性變換電路 進行全波整流,將“+1”和“-1”還原為1。變換后的碼元即為原信息碼。

2.3 編碼模塊的仿真

根據(jù)圖1所示的編碼模塊方框圖在QuartusⅡ平臺上用VHDL語言編程,編譯通過后可進行仿真。

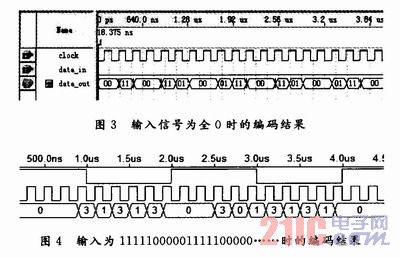

當輸入信碼為全“0”碼時,編碼結(jié)果為0-100-1+100+1-100-1+100+1……的序列,如圖3所示。圖中clock為時鐘信號,data_in為輸入信碼,data_out為編碼后的結(jié)果。data_out為00,表示“0”電平;data_out為01(十進制數(shù)字為1),表示“+1”電平;data_out為11(十進制數(shù)字為3),表示“-1”電平。

當輸入信碼為11111000001111100000……時,編碼結(jié)果為-1+1-1+1-1000-10+1-1+1-1+1000+1……的序列,如圖4所示。

由圖3,圖4可知,編碼結(jié)果完全正確。

2.4 譯碼模塊的仿真

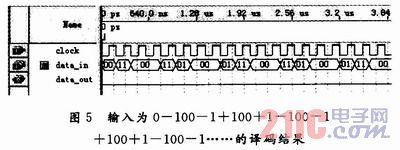

根據(jù)圖2所示,譯碼模塊方框圖在QuartusⅡ平臺上用VHDL語言編程,經(jīng)編譯后可進行仿真。為了將譯碼結(jié)果與原始信號進行比較,將圖3,圖4的編碼結(jié)果作為譯碼器的輸入信號進行譯碼,將譯碼結(jié)果與以上的原始信號進行比較。

當輸入的HDB3碼為0-100-1+100+1-100-1+100+1-100-1+100+1……譯碼結(jié)果為全“0”碼,如圖5所示。圖中clock為時鐘信號,data_in為輸入HDB3碼,data_out為輸出的信碼。data_in為00,表示“0”電平;data_in為01,表示“+1”電平;data_in為11,表示“-1”電平。

將譯碼結(jié)果與編碼前的原始信號做比較,可看出兩者是一致的。

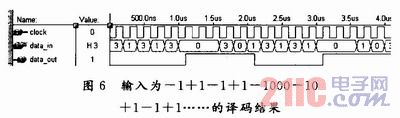

讓輸入信號data_in為31313000301313100010……,譯碼的結(jié)果為11111000001111100000……,如圖6所示。

將譯碼結(jié)果與編碼前的原始信號做比較,可看出兩者仍是一致的。

3 數(shù)字基帶系統(tǒng)設(shè)計與仿真

3.1 數(shù)字基帶系統(tǒng)的設(shè)計

HDB3編譯碼數(shù)字基帶系統(tǒng)的設(shè)計是在QuartusⅡ平臺上,采用原理圖的方式來實現(xiàn)的。首先,分別創(chuàng)建HDB3編碼模塊和譯碼模塊符號文件;然后新建基帶系統(tǒng)頂層文件;再在頂層文件中分別調(diào)入HDB3編碼模塊和譯碼模塊符號文件;按要求連線后,即得到HDB3編譯碼數(shù)字基帶系統(tǒng)電路。

3.2 數(shù)字基帶系統(tǒng)的仿真

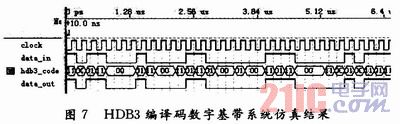

將以上原理圖進行編譯后,即可進行仿真。使輸入信碼為10110001000011000000111000001011,系統(tǒng)傳輸結(jié)果如圖7所示。圖中,clock為時鐘信號,data_in為輸入信碼,hdb3_code為系統(tǒng)傳輸用的HDB3碼,da_ta_out為輸出信碼。由圖可知,系統(tǒng)的輸出與輸入完全一致。

3.3 數(shù)字基帶系統(tǒng)的調(diào)試

當整個系統(tǒng)通過程序仿真后,將程序下載到ACEX1K-EP1K30TC144-1芯片,從而完成整個數(shù)字基帶系統(tǒng)的設(shè)計。調(diào)試時把發(fā)送部分與接收部分連接起來進行系統(tǒng)調(diào)試,檢測各測試點信號是否正確,在調(diào)試中,硬軟件要結(jié)合起來。由于芯片可以高度集成,問題一般出現(xiàn)在軟件上,故在調(diào)試中軟件參數(shù)的更改是最重要的。

4 結(jié)語

采用FPGA技術(shù)實現(xiàn)數(shù)字基帶傳輸系統(tǒng),包括編碼器的設(shè)計與仿真、譯碼器的設(shè)計與仿真以及整個數(shù)字基帶傳輸系統(tǒng)的設(shè)計與仿真。最后,在Altera公司的ACEX1K-EP1K30TC144-1芯片上加以實現(xiàn)。整個系統(tǒng)具有結(jié)構(gòu)簡單,性能穩(wěn)定,有效性好,可靠性高等優(yōu)點。除此之外,其優(yōu)點還體現(xiàn)在設(shè)計者不受芯片結(jié)構(gòu)的影響,避免了重復設(shè)計,縮短了開發(fā)周期;設(shè)計的模塊化,提高了軟硬件的組合度,使設(shè)計成果可以重復利用;在選擇實現(xiàn)系統(tǒng)目標器件的類型、規(guī)模、硬件結(jié)構(gòu)等方面,具有更大的自由度;總的設(shè)計方案和功能結(jié)構(gòu)被確定后,就可以進行多人多任務(wù)的并行工作方式,擴大了設(shè)計規(guī)模,提高了設(shè)計效率。