0 引言

正弦信號源在實驗室和電子工程設(shè)計中有著十分重要的作用,而傳統(tǒng)的正弦信號源根據(jù)實際需要一般價格昂貴,低頻輸出時性能不好且不便于自動調(diào)節(jié),工程實用性較差。本文的設(shè)計以較低的成本制作正弦信號發(fā)生器,可用作核磁共振中引發(fā)磁場測量儀的激勵一般的正弦信號,也可作為調(diào)制用的教學(xué)演示信號源。

正弦信號發(fā)生器主要由兩部分組成:正弦波信號發(fā)生器和產(chǎn)生調(diào)幅、調(diào)頻、鍵控信號。正弦波信號發(fā)生器采用直接數(shù)字頻率合成DDS技術(shù),在CPLD上實現(xiàn)正弦信號查找表和地址掃描,經(jīng)D/A輸出可得到正弦信號。具有頻率穩(wěn)定度高,頻率范圍寬,容易實現(xiàn)頻率步進100 Hz。全數(shù)字化結(jié)構(gòu)便于集成,輸出相位連續(xù),頻率、相位和幅度均可實現(xiàn)程控。

調(diào)幅、調(diào)頻、鍵控信號的產(chǎn)生可采用調(diào)頻、調(diào)幅專用芯片能分剮實現(xiàn),但是該方法實現(xiàn)的調(diào)頻調(diào)幅功能,對于某一特定頻率和特定的調(diào)制度、頻偏效果較好,在載波頻率可變和調(diào)制度、頻偏要求任意設(shè)定的情況下難以實現(xiàn)。本文利用CPLD和單片機AT89S52不僅可以實現(xiàn)頻率范圍可調(diào)的正弦波信號,而且在CPLD內(nèi)部加上相應(yīng)的數(shù)字控制算法就能方便地實現(xiàn)調(diào)頻FM,調(diào)幅AM和鍵控PSK、ASK數(shù)字調(diào)制功能有利于提高系統(tǒng)的整體性能和工作可靠性。正弦信號產(chǎn)生部分可在一片CPLD(EP1K30)中實現(xiàn),大大地簡化了硬件電路,便于功能擴展,并為進一步實現(xiàn)系統(tǒng)集成創(chuàng)造了條件。

1 理論分析與計算

1.1 正弦波形的產(chǎn)生

單向DDS由Nbit相位累加器和ROM只讀存儲器(正弦查找表)構(gòu)成的數(shù)控振蕩源(NCO),數(shù)模轉(zhuǎn)換器(DAC)、低通平滑濾波器(LPF)構(gòu)成,圖1所示為DDS的基本結(jié)構(gòu)。

圖1中fc為時鐘頻率,K為頻率控制字,N為相位累加器的字長,M為ROM地址線位數(shù),L為ROM數(shù)據(jù)線寬度,fo為輸出頻率。相位累加器由全加器和累加寄存器級聯(lián)組成。在時鐘頻率fc的控制下,對輸入頻率控制字K進行累加,累加滿量時就產(chǎn)生溢出。相位累加器的輸出對應(yīng)于該時刻合成周期信號的相位,并且這個相位是周期性的,在0~2π范圍內(nèi)變化。相位累加器位數(shù)為N,最大輸出為2N-1,對應(yīng)于2π的相位,累加1次就輸出1個相應(yīng)的相位碼,地址以查表方式,得到對應(yīng)相位的信號幅度值,經(jīng)過數(shù)模轉(zhuǎn)換,就可以得到一定頻率的信號輸出波形,低通濾波器對輸出的信號波形進行平滑處理,濾除雜波和諧波。由于控制字K經(jīng)過2N/K次累加,相位累加器滿量溢出,完成1個周期運算,所以輸出頻率fo由fc和K共同決定,即fo=fcK/2N且K《2N-1,得到DDS的最小分辨率可達fc/2N。理論上通過設(shè)定DDS相位累加器的位數(shù)N、頻率控制字K和時鐘頻率fc的值,就可以產(chǎn)生任一頻率的輸出。根據(jù)頻率步進100Hz的要求,選取累加器的位數(shù)為19位,計算出時鐘頻率fc應(yīng)為52.4288 MHz。步進的累計誤差通過軟件補償?shù)姆椒ㄟM行修正,利用現(xiàn)有的52.416 0 MHz晶振完全精確地實現(xiàn)步進100 Hz的要求。

圖1 基于DDS的正弦信號發(fā)生器的原理圖

1.2 產(chǎn)生模擬幅度調(diào)制信號

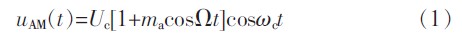

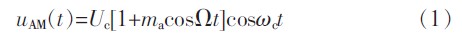

用調(diào)制信號去控制高頻振蕩的幅度,使其幅度的變化量隨調(diào)制信號成正比地變化,這一過程稱為幅度調(diào)制。若載波為uc=Uc cosωct,調(diào)制信號為f(t)=cosΩt,則調(diào)幅波為

普通調(diào)幅波利用模擬相乘器實現(xiàn),但是外圍電路復(fù)雜,改變調(diào)制度需改變電路元件的參數(shù),實現(xiàn)起來繁瑣。可以采用CPLD芯片結(jié)合DDS技術(shù)靈活的實現(xiàn)數(shù)字調(diào)幅,原理如圖2所示。

圖2 幅度調(diào)制原理圖

由DDS產(chǎn)生的波形信號作為載波,在單片機內(nèi)部作調(diào)制信號為1 kHz的正弦波形存儲表,根據(jù)鍵盤所設(shè)定的調(diào)制度ma(10%~100%)與存儲表中的數(shù)據(jù)相乘的結(jié)果送CPLD與DDS得到的波形相乘,再與DDS信號相加就產(chǎn)生相應(yīng)的數(shù)字調(diào)幅波編碼,經(jīng)D/A轉(zhuǎn)換得到模擬調(diào)幅信號。

1.3 產(chǎn)生模擬頻率調(diào)制信號

在連續(xù)波調(diào)制中,載波可表示為uc=Uc cosωct,調(diào)制信號為UΩ(t),調(diào)頻波是瞬時頻率的變化量與調(diào)制信號成正比,因此調(diào)頻波的瞬時角頻率除了載波角頻率ωc外,還附加一項和調(diào)制信號成正比的部分,式中kf為比例系數(shù),是單位調(diào)制信號強度引起的頻率變化。△ωf(t)的最大值△ωf稱為最大頻偏,反映在頻率上為f(t)=fc+△fcos(2πft),調(diào)頻波的表達式:

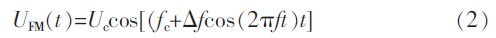

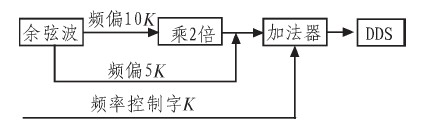

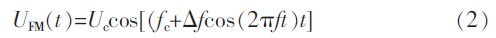

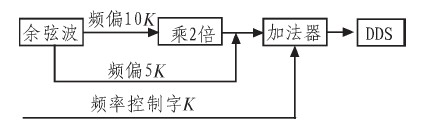

圖3為CPLD數(shù)字調(diào)頻電路,頻偏為5 K時的控制字是50,將余弦波形與50相乘,并與單片機傳遞的頻率控制字相加,送入DDS模塊經(jīng)D/A轉(zhuǎn)換就可以輸出調(diào)頻波,其設(shè)計原理圖如圖4所示。

圖3 CPLD數(shù)字調(diào)頻電路圖

圖4 頻率調(diào)制設(shè)計原理圖

0 引言

正弦信號源在實驗室和電子工程設(shè)計中有著十分重要的作用,而傳統(tǒng)的正弦信號源根據(jù)實際需要一般價格昂貴,低頻輸出時性能不好且不便于自動調(diào)節(jié),工程實用性較差。本文的設(shè)計以較低的成本制作正弦信號發(fā)生器,可用作核磁共振中引發(fā)磁場測量儀的激勵一般的正弦信號,也可作為調(diào)制用的教學(xué)演示信號源。

正弦信號發(fā)生器主要由兩部分組成:正弦波信號發(fā)生器和產(chǎn)生調(diào)幅、調(diào)頻、鍵控信號。正弦波信號發(fā)生器采用直接數(shù)字頻率合成DDS技術(shù),在CPLD上實現(xiàn)正弦信號查找表和地址掃描,經(jīng)D/A輸出可得到正弦信號。具有頻率穩(wěn)定度高,頻率范圍寬,容易實現(xiàn)頻率步進100 Hz。全數(shù)字化結(jié)構(gòu)便于集成,輸出相位連續(xù),頻率、相位和幅度均可實現(xiàn)程控。

調(diào)幅、調(diào)頻、鍵控信號的產(chǎn)生可采用調(diào)頻、調(diào)幅專用芯片能分剮實現(xiàn),但是該方法實現(xiàn)的調(diào)頻調(diào)幅功能,對于某一特定頻率和特定的調(diào)制度、頻偏效果較好,在載波頻率可變和調(diào)制度、頻偏要求任意設(shè)定的情況下難以實現(xiàn)。本文利用CPLD和單片機AT89S52不僅可以實現(xiàn)頻率范圍可調(diào)的正弦波信號,而且在CPLD內(nèi)部加上相應(yīng)的數(shù)字控制算法就能方便地實現(xiàn)調(diào)頻FM,調(diào)幅AM和鍵控PSK、ASK數(shù)字調(diào)制功能有利于提高系統(tǒng)的整體性能和工作可靠性。正弦信號產(chǎn)生部分可在一片CPLD(EP1K30)中實現(xiàn),大大地簡化了硬件電路,便于功能擴展,并為進一步實現(xiàn)系統(tǒng)集成創(chuàng)造了條件。

1 理論分析與計算

1.1 正弦波形的產(chǎn)生

單向DDS由Nbit相位累加器和ROM只讀存儲器(正弦查找表)構(gòu)成的數(shù)控振蕩源(NCO),數(shù)模轉(zhuǎn)換器(DAC)、低通平滑濾波器(LPF)構(gòu)成,圖1所示為DDS的基本結(jié)構(gòu)。

圖1中fc為時鐘頻率,K為頻率控制字,N為相位累加器的字長,M為ROM地址線位數(shù),L為ROM數(shù)據(jù)線寬度,fo為輸出頻率。相位累加器由全加器和累加寄存器級聯(lián)組成。在時鐘頻率fc的控制下,對輸入頻率控制字K進行累加,累加滿量時就產(chǎn)生溢出。相位累加器的輸出對應(yīng)于該時刻合成周期信號的相位,并且這個相位是周期性的,在0~2π范圍內(nèi)變化。相位累加器位數(shù)為N,最大輸出為2N-1,對應(yīng)于2π的相位,累加1次就輸出1個相應(yīng)的相位碼,地址以查表方式,得到對應(yīng)相位的信號幅度值,經(jīng)過數(shù)模轉(zhuǎn)換,就可以得到一定頻率的信號輸出波形,低通濾波器對輸出的信號波形進行平滑處理,濾除雜波和諧波。由于控制字K經(jīng)過2N/K次累加,相位累加器滿量溢出,完成1個周期運算,所以輸出頻率fo由fc和K共同決定,即fo=fcK/2N且K《2N-1,得到DDS的最小分辨率可達fc/2N。理論上通過設(shè)定DDS相位累加器的位數(shù)N、頻率控制字K和時鐘頻率fc的值,就可以產(chǎn)生任一頻率的輸出。根據(jù)頻率步進100Hz的要求,選取累加器的位數(shù)為19位,計算出時鐘頻率fc應(yīng)為52.4288 MHz。步進的累計誤差通過軟件補償?shù)姆椒ㄟM行修正,利用現(xiàn)有的52.416 0 MHz晶振完全精確地實現(xiàn)步進100 Hz的要求。

圖1 基于DDS的正弦信號發(fā)生器的原理圖

1.2 產(chǎn)生模擬幅度調(diào)制信號

用調(diào)制信號去控制高頻振蕩的幅度,使其幅度的變化量隨調(diào)制信號成正比地變化,這一過程稱為幅度調(diào)制。若載波為uc=Uc cosωct,調(diào)制信號為f(t)=cosΩt,則調(diào)幅波為

普通調(diào)幅波利用模擬相乘器實現(xiàn),但是外圍電路復(fù)雜,改變調(diào)制度需改變電路元件的參數(shù),實現(xiàn)起來繁瑣。可以采用CPLD芯片結(jié)合DDS技術(shù)靈活的實現(xiàn)數(shù)字調(diào)幅,原理如圖2所示。

圖2 幅度調(diào)制原理圖

由DDS產(chǎn)生的波形信號作為載波,在單片機內(nèi)部作調(diào)制信號為1 kHz的正弦波形存儲表,根據(jù)鍵盤所設(shè)定的調(diào)制度ma(10%~100%)與存儲表中的數(shù)據(jù)相乘的結(jié)果送CPLD與DDS得到的波形相乘,再與DDS信號相加就產(chǎn)生相應(yīng)的數(shù)字調(diào)幅波編碼,經(jīng)D/A轉(zhuǎn)換得到模擬調(diào)幅信號。

1.3 產(chǎn)生模擬頻率調(diào)制信號

在連續(xù)波調(diào)制中,載波可表示為uc=Uc cosωct,調(diào)制信號為UΩ(t),調(diào)頻波是瞬時頻率的變化量與調(diào)制信號成正比,因此調(diào)頻波的瞬時角頻率除了載波角頻率ωc外,還附加一項和調(diào)制信號成正比的部分,式中kf為比例系數(shù),是單位調(diào)制信號強度引起的頻率變化。△ωf(t)的最大值△ωf稱為最大頻偏,反映在頻率上為f(t)=fc+△fcos(2πft),調(diào)頻波的表達式:

圖3為CPLD數(shù)字調(diào)頻電路,頻偏為5 K時的控制字是50,將余弦波形與50相乘,并與單片機傳遞的頻率控制字相加,送入DDS模塊經(jīng)D/A轉(zhuǎn)換就可以輸出調(diào)頻波,其設(shè)計原理圖如圖4所示。

圖3 CPLD數(shù)字調(diào)頻電路圖

圖4 頻率調(diào)制設(shè)計原理圖

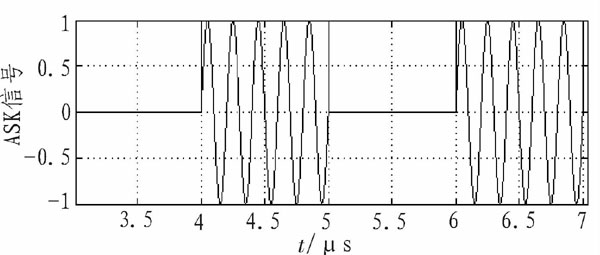

1.4 產(chǎn)生二進制PSK、ASK信號

用數(shù)字基帶信號去控制高頻正弦波的幅度就是振幅鍵控調(diào)制ASK。在CPLD內(nèi)部只需要根據(jù)所設(shè)定的二進制基帶序列碼對產(chǎn)生的DDS波形進行處理,二進制基帶序列為1時波形通過,序列為0時輸出0,仿真波形如圖5所示。

圖5 二進制ASK仿真波形圖

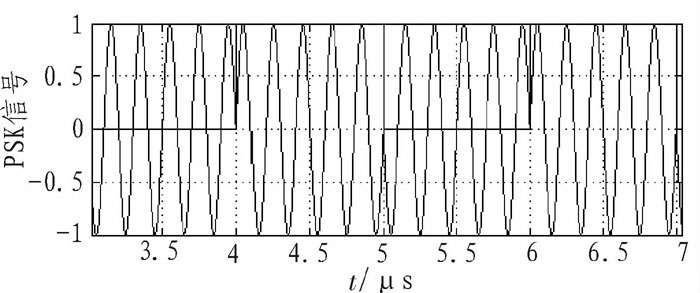

移相鍵控PSK是數(shù)字基帶信號去控制載波的相位。它是利用載波不同相位或相位變化來傳遞信息的。PSK的實現(xiàn)方法是根據(jù)數(shù)字基帶信號的兩個電平(或符號)使載波相位在兩個不同的數(shù)值之間切換,兩個載波相位通常相差180°。波形如圖6所示。

圖6 二進制PSK仿真波形圖

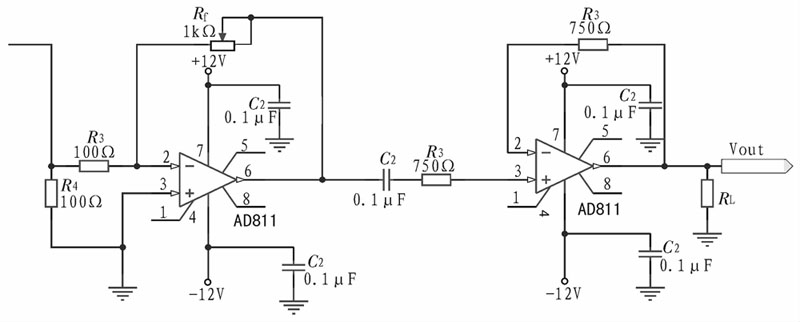

1.5 輸出信號調(diào)理部分

D/A轉(zhuǎn)換電路如圖7所示,選用的是12位高速D/A器件AD9713,該器件具有更好的靜態(tài)性能和動態(tài)特性。AD9713B更新速率可達100MS/ s。由于該D/A轉(zhuǎn)換器是針對DDS、波形重構(gòu)和高質(zhì)量圖像信號處理等應(yīng)用而設(shè)計的,這款芯片在動態(tài)特性方面表現(xiàn)特別突出,并且具有優(yōu)良的諧波抑制能力。AD9713輸出滿量程電流輸出是由VCONTROLAMP IN和RSET決定的,圖7中AD9713采用內(nèi)部參考電壓,輸出滿量程電流為-20 mA。

圖7 D/A轉(zhuǎn)換電路

幅度調(diào)節(jié)電路是由放大器組成。高頻信號放大要求放大器有足夠的輸出電壓轉(zhuǎn)換速率,在正弦波的情況下,放大器所需要的最大擺率SR=2πω=2πAf,其中ω為信號的角頻率,A為信號幅度,f為頻率。此外,幅度調(diào)節(jié)電路要求帶低阻負載,放大器的電流輸出能力也是個重要參數(shù),要在50 Ω負載上輸出6 V信號,則放大器至少要有120 mA的連續(xù)電流輸出能力。考慮以上原因,本文選擇AD公司的高速運放AD811作為輸出放大器,它是一個寬帶高速電流反饋型運算放大器,其各項參數(shù)非常適合上述指標(biāo):小信號帶寬(G=+2時)達120 MHz,電壓擺率SR為2 500 V/μs,全諧波失真THD為-74 dB(10 MHz),輸出電流達100 mA,其短路輸出電流可達150mA。

幅度調(diào)節(jié)電路如圖8所示,圖中R3和R4起分流作用,限制用于I/V轉(zhuǎn)換的電流,1個電流反饋的高速放大電路。它把AD9713輸出的電流轉(zhuǎn)換成電壓,通過反饋電阻Rf的電流決定AD811輸出的幅度為6 V。為了增大后級的帶負載能力設(shè)計了后級電壓跟隨,模擬輸出的最后部分是濾波電路,濾波器的選擇主要取決于系統(tǒng)所要輸出的波形,在50 Ω的負載電阻上的電壓峰峰值為6±1 V。

圖8 幅度調(diào)節(jié)電路

1.6 頻率值的接收與顯示

鍵盤、顯示部分用來實現(xiàn)用戶與單片機的交互。系統(tǒng)采用中斷查詢的方式接收通過鍵盤輸入的頻率值。該頻率值一方面送到數(shù)碼顯示接口進行顯示,另一方面轉(zhuǎn)化成頻率控制字送往相位累加模塊。

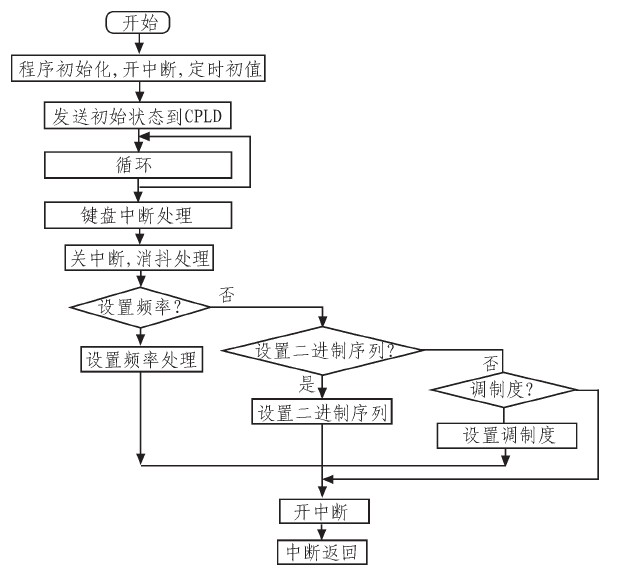

2 系統(tǒng)軟件設(shè)計

單片機程序采用C語言,在Keil uV2環(huán)境下編譯,用WAVE6000L仿真器調(diào)試CPLD在MAXPLUSⅡ下開發(fā),采用VHDL語言編程。

關(guān)于CPLD部分,相位測量儀和數(shù)字移相信號發(fā)生器采用ALTERA公司的EP1K30TC144-3FPGA芯片,原理圖已經(jīng)在前面的分析中。關(guān)于單片機部分,程序流程圖如圖9所示。

圖9 程序流程圖

3 功能及指標(biāo)測試

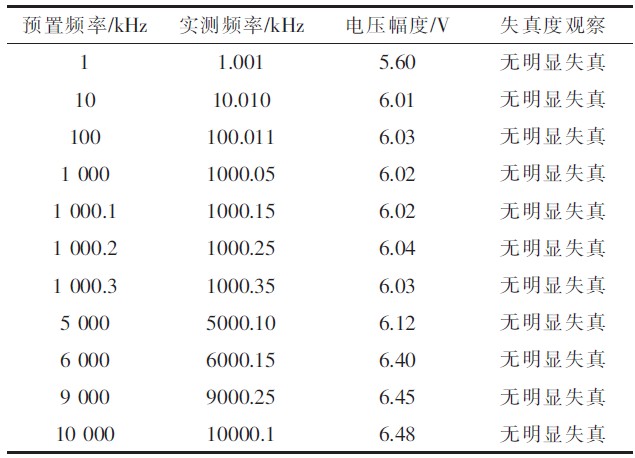

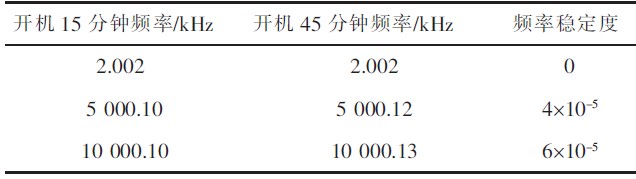

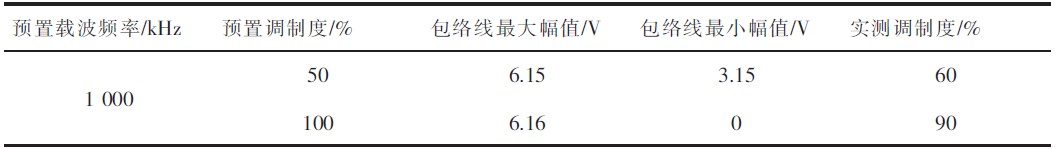

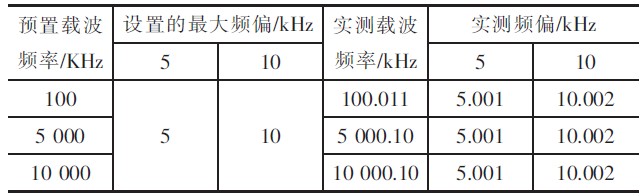

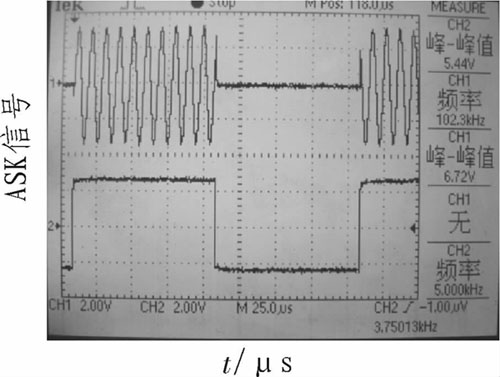

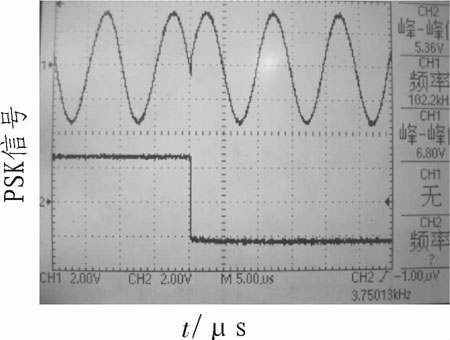

利用測試儀器:EE1641B1型函數(shù)信號發(fā)生器/計數(shù)器,直流穩(wěn)壓電源GPS-3303C、60 MHz示波器TDS1002,高頻測試儀等對設(shè)計的信號發(fā)生器進行性能測試。正弦波的頻率范圍、步進、在50 Ω負載上的輸出電壓幅度,失真度測量如表1所示,頻率穩(wěn)定度測量如表2所示,步進為10%的幅度調(diào)制測試如表3所示,調(diào)制信號為1 kHz的頻率調(diào)制測試如圖10所示,二進制PSK、ASK如圖11和圖12所示。

表1 正弦波實驗觀察結(jié)果

表2 正弦波頻率穩(wěn)定度測試結(jié)果

表3 正弦波幅度調(diào)制測試結(jié)果

圖10 正弦波頻率調(diào)制測試結(jié)果

圖11 ASK信號測試圖

圖12 PSK信號測試圖

經(jīng)過測試可以得到,本文設(shè)計的系統(tǒng)可達以下性能指標(biāo):

1)正弦波輸出頻率范圍 1 kHz~10 MHz。

2)具有頻率設(shè)置功能,頻率步進100 Hz。

3)輸出信號頻率穩(wěn)定度優(yōu)于10-4。

4)輸出電壓幅度在50 Ω負載電阻上的電壓峰-峰值Vopp≥1 V。

5)失真度用示波器觀察時無明顯失真。

綜合分析各項指標(biāo)的測試結(jié)果發(fā)現(xiàn),該設(shè)計頻率變化范圍大,信號穩(wěn)定度高,失真度好,達到了性能良好的設(shè)計要求。

4 結(jié)論

以CPLD和單片機AT89S52為基礎(chǔ),采用DDS技術(shù)實現(xiàn)的正弦信號發(fā)生器在保證輸出穩(wěn)定的正弦波頻率情況下能夠?qū)崿F(xiàn)頻率可調(diào),失真度小,頻率步進小,精確度高等特點,產(chǎn)生的正弦信號源可以廣泛運用于教學(xué)或一般工業(yè)以及實驗場合,測試結(jié)果表明本文提出的正弦信號發(fā)生器的設(shè)計是有效的,易于工程實現(xiàn)且具有一定的實用性。