頻譜分析儀按實(shí)現(xiàn)方式可分為模擬式和數(shù)字式兩種,前者以模擬濾波器為基礎(chǔ),后者則以數(shù)字濾波器和FFT分析為基礎(chǔ)。相比之下,模擬式頻譜分析儀不能獲得實(shí)時(shí)頻譜,且由于模擬濾波器會受到非線性、溫漂、老化等影響,測量精度不高; 而數(shù)字式頻譜分析儀由于其基于數(shù)字濾波器,故而形狀因子小,頻率分辨率高,穩(wěn)定性好,可以獲得很窄的分析帶寬,而測量精度較高; 而且由于它基于高速ADC技術(shù)、數(shù)字信號處理技術(shù)、FFT分析等進(jìn)行設(shè)計(jì),因而具有多種譜分析能力。隨著現(xiàn)場可編程門陣列(FPGA) 器件、DSP器件等在芯片邏輯規(guī)模和處理速度等方面性能的迅速提高,數(shù)字式頻譜儀的測量速度更快、實(shí)時(shí)性也更強(qiáng)。

在數(shù)字中頻式頻譜儀中,分辨率帶寬濾波是數(shù)字中頻處理模塊設(shè)計(jì)的關(guān)鍵,它決定了頻譜分析的有效信號帶寬,同時(shí)表征頻譜儀在響應(yīng)中明確分離出兩個(gè)輸入信號的能力,是頻譜儀的主要技術(shù)指標(biāo)之一。為了滿足信號的實(shí)時(shí)性和精度要求,通常以高速A/D采樣得到數(shù)字中頻信號,但其數(shù)據(jù)率過高,故其成為數(shù)字處理的瓶頸。一般需要使用數(shù)字正交解調(diào)技術(shù)將信號搬移至基帶,然后通過多速率信號處理技術(shù)來設(shè)計(jì)抽取濾波器,以降低數(shù)據(jù)率,最終實(shí)現(xiàn)數(shù)字FIR濾波器。

本文采用數(shù)字下變頻技術(shù),并基于FPGA硬件設(shè)計(jì)數(shù)字中頻處理模塊,調(diào)用不同的IP核進(jìn)行設(shè)計(jì),同時(shí)采用參數(shù)可配置的結(jié)構(gòu)來實(shí)現(xiàn)可變抽取率濾波器和分辨率帶寬數(shù)字濾波器。由于IP核是經(jīng)過了嚴(yán)格的性能測試并且進(jìn)行了優(yōu)化,時(shí)序穩(wěn)定,因而可以滿足系統(tǒng)高速與實(shí)時(shí)性處理的要求。

1 數(shù)字下變頻原理

全數(shù)字中頻處理技術(shù)是軟件無線電中的關(guān)鍵技術(shù)之一,它主要應(yīng)用于將中頻信號下變頻至基帶信號,在降低采樣率的同時(shí),該技術(shù)可保證所需要的信號不被混疊,因而十分方便于后續(xù)更多基帶信號處理技術(shù)的使用。全數(shù)字中頻技術(shù)包含數(shù)字正交解調(diào)技術(shù)和多抽樣率信號處理技術(shù)兩部分。

1.1 數(shù)字正交解調(diào)

正交解調(diào)也稱為正交變頻,它主要通過數(shù)字混頻實(shí)現(xiàn),設(shè)輸入中頻信號為:

![]()

其中,信號中心頻率遠(yuǎn)大于信號帶寬B,且信號的采樣速率滿足奈奎斯特定理,即f0>>B,fs>2B。那么,經(jīng)過正交變換后,該信號的基帶調(diào)制信號為:

式中,ZBI (t) 稱為I信號,ZBQI (t) 稱為Q信號。由式(2) 可以看出,基帶信號ZBI (t)、ZBQI(t)只包含振幅和相位信息且頻率為零,因此,正交解調(diào)過程就是從中頻信號x (t) 獲得基帶信號的過程。

正交解調(diào)過程的系統(tǒng)模塊為正交雙通道結(jié)構(gòu),分別稱為I通道和Q通道。由于輸入和正交本振、混頻器均由數(shù)字實(shí)現(xiàn),故具有集成度高、一致性好的特點(diǎn),可以獲得很好的通道一致性,而采用數(shù)控振蕩器也使得相位的正交性也得到很好的保證。

1.2 多抽樣率信號處理

由于對中頻信號的采樣率較高,而基帶信號處理一般只需在較低的采樣率下進(jìn)行,因此,經(jīng)數(shù)字正交解調(diào)后的基帶信號都處于嚴(yán)重的過采樣狀態(tài),必須進(jìn)行采樣率之間的轉(zhuǎn)換,以降低數(shù)據(jù)流速率,這種信號采樣率的變化就是基于多速率信號處理技術(shù)。

整數(shù)倍的抽取可使信號采樣率降低整數(shù)倍,其抽取倍數(shù)為D。由于抽取降低了信號的采樣率,所以,抽取后的信號可能不再滿足奈奎斯特采樣條件而產(chǎn)生混疊。而為了保證所需信號不失真,抽取前,一般先用數(shù)字低通濾波器根據(jù)抽取后的采樣率對信號進(jìn)行帶限處理,以使濾波器的截止頻率ωc為所需要信號的最大帶寬B,當(dāng)抽取前采樣率fs1與抽取后采樣率fs2滿足fs2=fs1/D≥2B時(shí),信號抽取后就不會產(chǎn)生混疊。

1.3 頻譜儀多抽取率濾波器原理

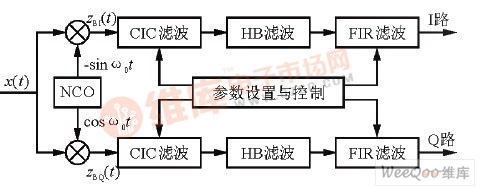

數(shù)字中頻式頻譜分析儀的分辨率帶寬是通過多抽樣率濾波器設(shè)計(jì)實(shí)現(xiàn)的。針對下變頻后依然過采樣的數(shù)據(jù)流,則需要以不同速率的濾波和抽取,以獲得不同的實(shí)時(shí)分析帶寬。這樣,實(shí)際的抽取率變化范圍很大,例如,當(dāng)需要較窄的分辨率帶寬時(shí),其抽取率很高,要求采用多級的濾波和抽取來逐步降低采樣率,這樣也降低了對每一級抗混疊濾波器的要求。由于ADC是在中頻進(jìn)行采樣,數(shù)據(jù)率和采樣率是一致的,而FIR濾波器無法保證高采樣率低帶寬的設(shè)計(jì),因此,要先通過CIC (梳狀濾波器) 和HB (半帶濾波器) 濾波抽取器進(jìn)行大的抽取,使數(shù)據(jù)率快速降下來,再由FIR濾波器進(jìn)行濾波。結(jié)合正交解調(diào),數(shù)字下變頻的結(jié)構(gòu)框圖如圖1所示。

圖1 數(shù)字下變頻器結(jié)構(gòu)框圖

CIC (梳狀) 濾波器的系數(shù)都為1,而且只有加法運(yùn)算,沒有乘法運(yùn)算,因而硬件實(shí)現(xiàn)非常容易,同時(shí)可以達(dá)到很高的處理速率,很適合作抽取系統(tǒng)中第一級抽取和進(jìn)行大的抽取因子。但單級CIC濾波器的過渡帶和阻帶衰減特性不好,通常需要采用多級級聯(lián)方式來加大濾波器旁瓣電平衰減。選用5級級聯(lián)時(shí),阻帶衰減約為67.3dB,可以滿足第一級濾波器衰減要求。雖然CIC抽取率較高,但其頻率響應(yīng)3dB有效帶寬很窄。而要保證有效帶寬基本不變,且繼續(xù)降低抽取率,其后級可以采用半帶濾波器。

HB (半帶) 濾波器的系數(shù)幾乎一半為零,其濾波時(shí)的運(yùn)算量可減少一半。而其抽取因子固定為2,因此,經(jīng)過N級HB濾波器后,可以使采樣率降低2N倍。多級濾波抽取后的頻率響應(yīng)在通帶內(nèi)無交疊,它只在過渡帶邊緣有交集,因而具有很好的抗混疊效果。

通過CIC和HB多組濾波器的濾波抽取,基帶信號被降到了較低的采樣率,可以適于FIR處理。

由于FIR濾波器的階數(shù)較高,可以設(shè)計(jì)成過渡帶小、阻帶衰減高且具有很好波形因子的頻率響應(yīng),以滿足頻譜分析儀對分辨率帶寬濾波器的特別要求。

2 數(shù)字中頻處理邏輯

近年來,F(xiàn)PGA器件在工藝及邏輯規(guī)模方面的快速發(fā)展和成本的不斷降低,利用FPGA器件來實(shí)現(xiàn)高速專業(yè)數(shù)字下變頻模塊已經(jīng)成為系統(tǒng)設(shè)計(jì)中的常用方法。FPGA芯片中不僅集成了大量的可編程邏輯資源,還包含了豐富的數(shù)字信號處理的硬核和固核資源,故能滿足多種系統(tǒng)的數(shù)字應(yīng)用和設(shè)計(jì),且IP核資源豐富,實(shí)現(xiàn)起來靈活快速,性能穩(wěn)定,可以滿足高速時(shí)序要求。

FPGA IP核是預(yù)先設(shè)計(jì)好的功能模塊,一般采用參數(shù)可配置的結(jié)構(gòu),并可以通過Core Gener-ator工具調(diào)用。數(shù)字下變頻的設(shè)計(jì)可用正交數(shù)字解調(diào)的數(shù)控振蕩器(NCO) 和乘法器,并分別調(diào)用IP核DDS Compiler 4.0和Multiplier 11.2來實(shí)現(xiàn),其中DDS Compiler可以提供SINE和COSINE兩個(gè)通道。在抽取濾波設(shè)計(jì)中,圖1所示的多組濾波器均可通過調(diào)用IP核(CIC Compiler 1.3和FIR Compiler5.0) 來實(shí)現(xiàn)。CIC Compiler 1.3可提供輸入數(shù)據(jù)采樣率、工作頻率、以及可編程抽取等多種參數(shù)的設(shè)定; HB濾波器和FIR 濾波器均采用FIRCompiler 5.0,該IP核可以導(dǎo)入*.coe格式的濾波系數(shù),并通過導(dǎo)入不同的系數(shù)來區(qū)分不同類型的濾波器。它同時(shí)提供有不同濾波器結(jié)構(gòu)類型的設(shè)定,包括乘累加結(jié)構(gòu)、基于DA算法結(jié)構(gòu)和多相濾波結(jié)構(gòu)以及輸入數(shù)據(jù)采樣率和工作頻率等基本濾波器參數(shù)的設(shè)定。

數(shù)字下變頻模塊的整體設(shè)計(jì)如圖2所示,由于I、Q兩路對稱,為了方便,這里只描述Q路的數(shù)字下變頻實(shí)現(xiàn)過程。本設(shè)計(jì)采用Xilinx公司的Spartan–3A–DSP系列FPGA芯片來實(shí)現(xiàn),它整合了DSP48A模塊,并含有豐富的乘法器資源,適合數(shù)字信號處理模塊的實(shí)現(xiàn),且成本和功耗都很低。

圖2 數(shù)字下變頻模塊整體設(shè)計(jì)

處理模塊按數(shù)字下變頻原理,可依次實(shí)現(xiàn)正交解調(diào)、抽取濾波和FIR濾波,最終得到基帶信號。該模塊共有三個(gè)輸入,信號輸入為A/D轉(zhuǎn)換器的輸出序列,位數(shù)14-bit,采樣率為100MSPS,中心頻率為21.4MHz,這決定了數(shù)字中頻中NCO輸出位數(shù)可同設(shè)為14 -bit,輸出頻率設(shè)為21.4MHz。

時(shí)鐘輸入是A/D轉(zhuǎn)換器輸出序列的隨路時(shí)鐘,頻率為100MHz,可作為處理模塊的工作時(shí)鐘。

在FPGA設(shè)計(jì)平臺的ISE中,BUFG是全局緩沖,它連接的是芯片中的專用時(shí)鐘資源,目的是減少信號的傳輸延時(shí),提高驅(qū)動能力,這對于時(shí)序電路中的關(guān)鍵時(shí)鐘信號是非常重要的。DCM是數(shù)字時(shí)鐘管理單元,具有最小的時(shí)鐘延遲和抖動,故可采用DCM+BUFG方法將時(shí)鐘輸入分配為FPGA時(shí)鐘。而使用全局時(shí)鐘資源則可保證時(shí)序同步。

帶寬輸入為分辨率帶寬步進(jìn)輸入,它決定了待分析帶寬B (RBW) 和濾波器組的抽取。操作時(shí),首先可由待分析帶寬確定最后一級FIR濾波器的3dB帶寬和輸入采樣率,然后再根據(jù)A/D采樣率與FIR輸入采樣率的比值來確定CIC濾波器抽取因子和HB濾波器級聯(lián)級數(shù)。

另外,在模塊整體設(shè)計(jì)中,位數(shù)處理也是一個(gè)關(guān)鍵,它由帶寬步進(jìn)輸入決定,可調(diào)整各個(gè)部分的二進(jìn)制輸出位寬。因?yàn)闉V波的卷積運(yùn)算為乘累加運(yùn)算,這會導(dǎo)致濾波器的輸出位數(shù)增多,可在輸出精度和準(zhǔn)確度滿足要求的情況下,在正交解調(diào)和每一級濾波器后做位數(shù)處理,這樣的方法一是為了防止多余的輸出位數(shù)在后級濾波器中累加,從而節(jié)省FPGA邏輯資源; 二是為了調(diào)整濾波器組的輸出幅度,以避免在不同帶寬選擇時(shí)輸出幅度不一致。

3 分辨率帶寬設(shè)計(jì)

本設(shè)計(jì)的分辨率帶寬范圍為1kHz~3MHz,按1–3–10步進(jìn)變換,共8個(gè)檔位。分辨率帶寬步進(jìn)輸入如表1所列,每一個(gè)步進(jìn)均決定了相應(yīng)的CIC抽取因子和HB的級聯(lián)級數(shù),同時(shí)也決定了最后一級FIR濾波器的輸入數(shù)據(jù)和相應(yīng)采樣率。

表1 抽取因子分配表(采樣率100MSPS)

抽取濾波的目的是將正交解調(diào)后的高速率基帶信號降低到合適的信號速率,以便常用的基帶處理技術(shù)使用。在此設(shè)定基帶信號采樣率與分辨率帶寬步進(jìn)為5倍的關(guān)系,以計(jì)算對應(yīng)的I、Q基帶信號的采樣率,進(jìn)而確定處理模塊總的抽取率。由于IP核的抽取率參數(shù)只能為整數(shù),所以,要通過對理想抽取率取整,應(yīng)盡量滿足RBW與基帶信號采樣率的比例關(guān)系。而對于低抽取率的檔位,只通過CIC抽取就可以完成,但要對HB濾波器進(jìn)行旁路控制,即HB級聯(lián)抽取為1。通過濾波器旁路控制和抽取因子可編程實(shí)現(xiàn)寬范圍抽取因子的調(diào)整,進(jìn)而控制數(shù)據(jù)流采樣,也可以實(shí)現(xiàn)分析帶寬的變采樣率控制。

在圖2所示的整體設(shè)計(jì)框圖中,CIC濾波器是抽取部分的第一級,可實(shí)現(xiàn)高速抽取,但其通帶、阻帶特性的可控性不強(qiáng)。通過IP核可設(shè)置抽取率(R) 和級數(shù)(N) 等參數(shù),而且操作簡單。

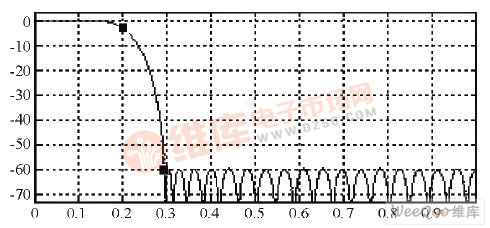

HB濾波器是抽取部分的第二級,單級抽取因子固定為2,有3級級聯(lián)和5級級聯(lián)兩種情況,各級均采用歸一化頻率設(shè)計(jì)方法,以避免重復(fù)設(shè)計(jì)。通常采用MATLAB的FDATOOL工具來設(shè)計(jì)濾波器,并以RBW濾波器輸入信號采樣率的2倍作為歸一化參考頻率,同時(shí)保證FIR濾波器通帶頻率范圍內(nèi)的信號無衰減。由于FIR濾波器的通帶設(shè)定為0.2,且HB濾波器在此主要做為抽取濾波器,故設(shè)通帶頻率上限為0.21,濾波器階數(shù)為19階,圖3所示是半帶濾波器(HB) 的頻率響應(yīng)曲線。半帶濾波系數(shù)為對稱系數(shù)且有將近一半的系數(shù)為零,19個(gè)濾波系數(shù)只有6個(gè)參與乘法計(jì)算,故不會消耗大量的乘法器資源,另外,抽取部分I、Q兩路的數(shù)據(jù)流速率較高,故采用乘累加結(jié)構(gòu)搭建HB濾波器,以滿足高速的時(shí)序處理要求。

在設(shè)計(jì)各個(gè)分辨率帶寬步進(jìn)輸入所對應(yīng)的RBW濾波器時(shí),為了節(jié)約FPGA邏輯資源和簡化設(shè)計(jì),也可以采用歸一化頻率設(shè)計(jì)方法,這樣可以使I、Q支路各設(shè)計(jì)一個(gè)RBW濾波器。由于FIR濾波器的輸入采樣率fs越大,濾波器的最小階數(shù)越高,因而選擇3dB帶寬與采樣率按0.2的歸一化比例來設(shè)計(jì)濾波器的頻率響應(yīng),且FIR濾波器不進(jìn)行抽取,其輸入采樣率等于I、Q基帶信號采樣率。根據(jù)I、Q路信號的歸一化帶寬0.20可設(shè)定RBW濾波器的通帶頻率上限為0.20,阻帶頻率下限為0.29,濾波器階數(shù)為47 階,阻帶衰減為60dB,波形因子SF60/3 =B60dB/B3dB =0.29/0.20≈1.45,圖4所示FIR濾波器的頻率響應(yīng)曲線。

將生成的*.coe格式的濾波系數(shù)可以導(dǎo)入FPGA中所調(diào)用的IP核中,考慮到FPGA乘法器資源有限,由于輸入數(shù)據(jù)經(jīng)前面抽取,其數(shù)據(jù)率已降低,這里采用基于DA算法結(jié)構(gòu)來搭建RBW濾波器。

圖3 半帶濾波器(HB) 頻率響應(yīng)

圖4 分辨率濾波器(FIR) 頻率響應(yīng)

4 結(jié)束語

采用FPGA硬件并調(diào)用各類IP核來實(shí)現(xiàn)全數(shù)字中頻技術(shù)的應(yīng)用方法,其時(shí)序性能穩(wěn)定,可以很好的滿足高速、實(shí)時(shí)的信號處理要求。在頻譜儀分辨率帶寬設(shè)計(jì)中,結(jié)合范圍為1kHz~3MHz的可程控分析帶寬,可以采用多速率信號處理技術(shù)來降低數(shù)字信號的采樣率,并為數(shù)字幅度/相位檢波、視頻檢波、DSP開發(fā)以及實(shí)現(xiàn)FFT等后續(xù)信號的頻譜分析進(jìn)行準(zhǔn)備。該數(shù)字中頻處理模塊也能應(yīng)用于網(wǎng)絡(luò)分析、通信分析、雷達(dá)信號分析等其他設(shè)計(jì),而且可以有效減小系統(tǒng)體積,保證設(shè)計(jì)的可靠性。