二進制序列信號檢測器是一種能夠檢測輸入的一串二進制編碼,當(dāng)該二進制碼與事先設(shè)定的碼一致時,檢測電路輸出高電平,否則輸出低電平。該檢測電路可廣泛用于日常生產(chǎn)、生活及軍事。例如,可以用在密碼認(rèn)證中,當(dāng)輸入密碼與事先設(shè)定的密碼一致時,認(rèn)證成功。再如在軍事領(lǐng)域,比較關(guān)心的是敵方通信中某些感興趣的內(nèi)容,而通信數(shù)據(jù)是海量且加密的,沒有必要一一破譯,只要破譯部分關(guān)鍵詞后,就可在偵聽過程中,只檢測這些關(guān)鍵詞,一旦偵聽到,立即啟動記錄儀,記錄關(guān)鍵詞時段的通信內(nèi)容加以解密。在許多電子技術(shù)資料中也有一些序列信號檢測電路的設(shè)計,但設(shè)計方法單一、擴展性不強。下面通過實例來說明電路的3種設(shè)計方法。

設(shè)計任務(wù):設(shè)計一個二進制序列信號檢測器,它有一個輸入X,當(dāng)接收到的序列為1001,則在上述序列輸入最后一個1的同時,電路輸出Z=1,否則輸出為0,輸入序列可以重疊。例如:當(dāng)輸入X的序列為0100100101001(首位在左),對應(yīng)輸出Z=0000100100001。

1 用分立觸發(fā)器設(shè)計

觸發(fā)器的種類很多,其中雙端輸入的JK觸發(fā)器和單端輸入的D觸發(fā)器最具代表性。由于用D觸發(fā)器設(shè)計的電路更為簡單,故采用它來設(shè)計電路。

1.1 邏輯抽象

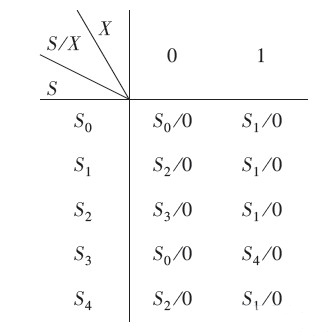

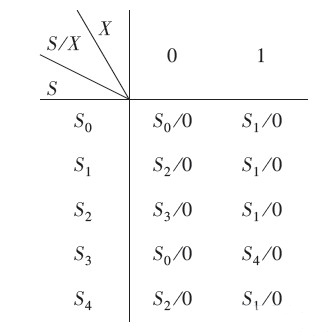

由于待檢測的序列為1001,故設(shè)電路在一直輸入0時的狀態(tài)為S0,輸入一個1以后的狀態(tài)為S1,連續(xù)輸入10以后的狀態(tài)為S2,連續(xù)輸入100后的狀態(tài)為S3,連續(xù)輸入1001后的狀態(tài)為S4。于是得到狀態(tài)轉(zhuǎn)換如圖1所示。

圖1 狀態(tài)轉(zhuǎn)換圖

選取第1、3行解釋其原理:S0表示接收到的是0,當(dāng)在此基礎(chǔ)上再接收到一個0后變?yōu)?0,而需要檢測的序列是1001,所以電路狀態(tài)仍然停留在S0上;當(dāng)電路在S0的基礎(chǔ)上接收到1后表示接收到1001序列中的第一個1,于是電路狀態(tài)轉(zhuǎn)為S1。同理S2表示已經(jīng)接收到10,當(dāng)在此基礎(chǔ)上接收到0后變?yōu)?00,電路轉(zhuǎn)到S3,但是接收到1后則變?yōu)?01,于是前面接收的兩位代碼失去作用,只有第3位的1可作為1001的第一位,所以電路狀態(tài)轉(zhuǎn)回S1。

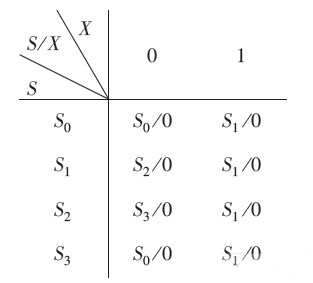

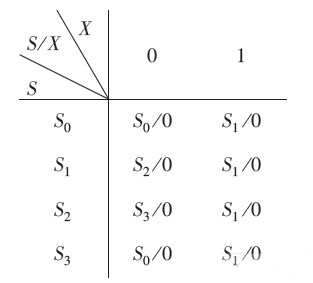

通過觀察狀態(tài)轉(zhuǎn)換表,可以發(fā)現(xiàn),S1和S4在同樣的輸入下有同樣的輸出,而且狀態(tài)轉(zhuǎn)移后得到同樣的次態(tài)。因此它們是等價的可以合并,于是,狀態(tài)轉(zhuǎn)換表可以化簡如圖2所示。

圖2 化簡后的轉(zhuǎn)換表

從物理概念上也不難理解這種情況。當(dāng)電路連續(xù)接收到1001后,輸出為1,但序列可以重疊,故最后一個1可作為下一個1001序列的第一位,所以電路在連續(xù)接收到1001后的狀態(tài)S4實際上就是S1。

1.2 編碼

由化簡后的狀態(tài)轉(zhuǎn)換表2可知,電路總共有4種狀態(tài)(S0~S3),而每個觸發(fā)器的輸出Q可以用0或1表示兩種狀態(tài),于是兩個觸發(fā)器的輸出Q1Q0的4種00、01、10、11就可以表示這4種狀態(tài)S0~S3。這個過程即為編碼。

二進制序列信號檢測器是一種能夠檢測輸入的一串二進制編碼,當(dāng)該二進制碼與事先設(shè)定的碼一致時,檢測電路輸出高電平,否則輸出低電平。該檢測電路可廣泛用于日常生產(chǎn)、生活及軍事。例如,可以用在密碼認(rèn)證中,當(dāng)輸入密碼與事先設(shè)定的密碼一致時,認(rèn)證成功。再如在軍事領(lǐng)域,比較關(guān)心的是敵方通信中某些感興趣的內(nèi)容,而通信數(shù)據(jù)是海量且加密的,沒有必要一一破譯,只要破譯部分關(guān)鍵詞后,就可在偵聽過程中,只檢測這些關(guān)鍵詞,一旦偵聽到,立即啟動記錄儀,記錄關(guān)鍵詞時段的通信內(nèi)容加以解密。在許多電子技術(shù)資料中也有一些序列信號檢測電路的設(shè)計,但設(shè)計方法單一、擴展性不強。下面通過實例來說明電路的3種設(shè)計方法。

設(shè)計任務(wù):設(shè)計一個二進制序列信號檢測器,它有一個輸入X,當(dāng)接收到的序列為1001,則在上述序列輸入最后一個1的同時,電路輸出Z=1,否則輸出為0,輸入序列可以重疊。例如:當(dāng)輸入X的序列為0100100101001(首位在左),對應(yīng)輸出Z=0000100100001。

1 用分立觸發(fā)器設(shè)計

觸發(fā)器的種類很多,其中雙端輸入的JK觸發(fā)器和單端輸入的D觸發(fā)器最具代表性。由于用D觸發(fā)器設(shè)計的電路更為簡單,故采用它來設(shè)計電路。

1.1 邏輯抽象

由于待檢測的序列為1001,故設(shè)電路在一直輸入0時的狀態(tài)為S0,輸入一個1以后的狀態(tài)為S1,連續(xù)輸入10以后的狀態(tài)為S2,連續(xù)輸入100后的狀態(tài)為S3,連續(xù)輸入1001后的狀態(tài)為S4。于是得到狀態(tài)轉(zhuǎn)換如圖1所示。

圖1 狀態(tài)轉(zhuǎn)換圖

選取第1、3行解釋其原理:S0表示接收到的是0,當(dāng)在此基礎(chǔ)上再接收到一個0后變?yōu)?0,而需要檢測的序列是1001,所以電路狀態(tài)仍然停留在S0上;當(dāng)電路在S0的基礎(chǔ)上接收到1后表示接收到1001序列中的第一個1,于是電路狀態(tài)轉(zhuǎn)為S1。同理S2表示已經(jīng)接收到10,當(dāng)在此基礎(chǔ)上接收到0后變?yōu)?00,電路轉(zhuǎn)到S3,但是接收到1后則變?yōu)?01,于是前面接收的兩位代碼失去作用,只有第3位的1可作為1001的第一位,所以電路狀態(tài)轉(zhuǎn)回S1。

通過觀察狀態(tài)轉(zhuǎn)換表,可以發(fā)現(xiàn),S1和S4在同樣的輸入下有同樣的輸出,而且狀態(tài)轉(zhuǎn)移后得到同樣的次態(tài)。因此它們是等價的可以合并,于是,狀態(tài)轉(zhuǎn)換表可以化簡如圖2所示。

圖2 化簡后的轉(zhuǎn)換表

從物理概念上也不難理解這種情況。當(dāng)電路連續(xù)接收到1001后,輸出為1,但序列可以重疊,故最后一個1可作為下一個1001序列的第一位,所以電路在連續(xù)接收到1001后的狀態(tài)S4實際上就是S1。

1.2 編碼

由化簡后的狀態(tài)轉(zhuǎn)換表2可知,電路總共有4種狀態(tài)(S0~S3),而每個觸發(fā)器的輸出Q可以用0或1表示兩種狀態(tài),于是兩個觸發(fā)器的輸出Q1Q0的4種00、01、10、11就可以表示這4種狀態(tài)S0~S3。這個過程即為編碼。

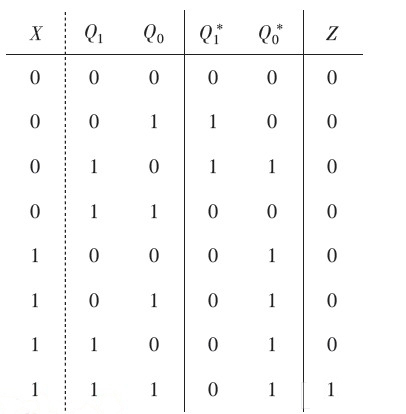

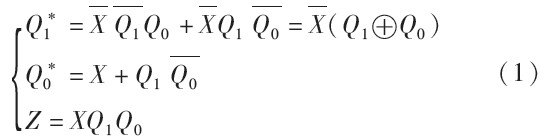

1.3 列真值表并寫出狀態(tài)方程

將化簡后的狀態(tài)轉(zhuǎn)換為表中各狀態(tài),用編碼表示即得到真值表,如圖3所示。其中表示Q1Q0的下一狀態(tài)。寫出關(guān)于X,Q1,Q0的方程,即電路的狀態(tài)方程,如式(1)所示。

圖3 真值表

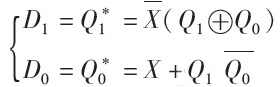

1.4 作邏輯電路圖

由于D觸發(fā)器的特性方程為Q*=D,從而 ,根據(jù)該方程就可以畫出邏輯電路圖,如圖4所示。

,根據(jù)該方程就可以畫出邏輯電路圖,如圖4所示。

圖4 序列碼檢測器邏輯電路圖

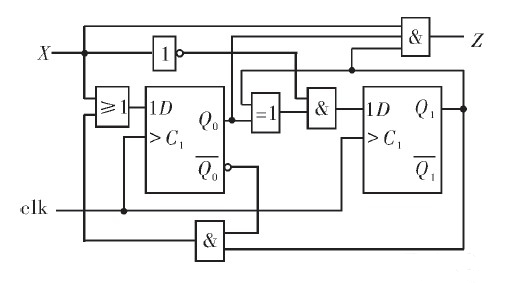

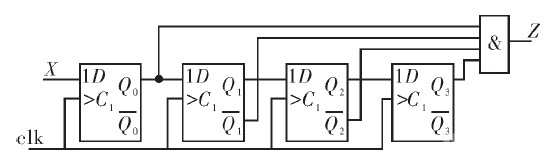

2 將觸發(fā)器接成移位寄存器進行設(shè)計

以上設(shè)計方法主要依靠電路的狀態(tài)轉(zhuǎn)換實現(xiàn)序列碼檢測,雖然所得電路簡單,但是設(shè)計過程較復(fù)雜,特別是當(dāng)需要檢測的序列碼位數(shù)較長時,工作量較大。為此,將觸發(fā)器接成移位寄存器的方式,可簡化電路設(shè)計,同時也便于擴展成位數(shù)更多的序列碼檢測器。用4個D觸發(fā)器接成的向右移位寄存器。電路如圖5所示。

圖5 移位寄存器型序列碼檢測器

由圖5可知, 。在移位脈沖clk作用下,輸入端X輸入的二進制碼依次向右移動,每當(dāng)出現(xiàn)一個完整的1001序列時,輸出端Z便出現(xiàn)高電平。這樣就實現(xiàn)了序列碼檢測的功能。

。在移位脈沖clk作用下,輸入端X輸入的二進制碼依次向右移動,每當(dāng)出現(xiàn)一個完整的1001序列時,輸出端Z便出現(xiàn)高電平。這樣就實現(xiàn)了序列碼檢測的功能。

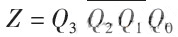

3 用中規(guī)模集成電路進行設(shè)計

既然用移位寄存器可以實現(xiàn)序列信號檢測,那么用集成移位寄存器加少量門電路同樣可以實現(xiàn),而且電路可靠性更高。用4位集成移位寄存器74LS194,實現(xiàn)的序列1001檢測器,如圖6所示。

圖6 用集成移位寄存器構(gòu)成序列碼檢測器

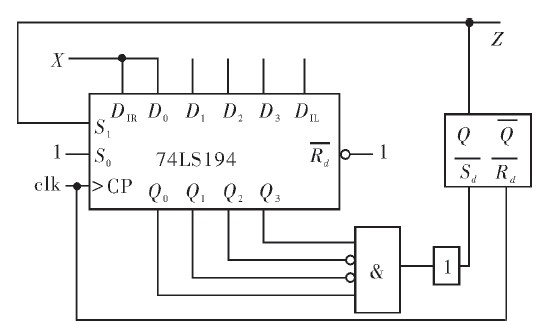

4 當(dāng)序列不可重疊時的電路設(shè)計

用以上3種方法設(shè)計出的電路,都是可序列重疊的序列碼檢測器,若要求被檢測的序列不可重疊,則在方法1中,只需要根據(jù)實際情況修改狀態(tài)轉(zhuǎn)換表即可。后面的設(shè)計原理及步驟不變。這種設(shè)計方法存在的問題仍然是當(dāng)待檢測的序列位數(shù)較長時,設(shè)計工作量大、電路可靠性降低。在采用第2、第3種方法設(shè)計時,需增加部分控制電路,為保證輸入與時鐘的同步性,需要使得每當(dāng)檢測出一個序列時,直接將序列的下一位置入寄存器最低位,同時置寄存器其余各位為序列碼最后一位的反碼以消除重疊代碼的影響。此外再用一個鎖存器使輸出高電平多保持0.5個時鐘周期,其優(yōu)點是:可以消除移位過程中的競爭冒險,使得輸出波形更穩(wěn)定、電路可靠性更高,電路如圖7所示。

圖7 用移位寄存器構(gòu)成的序列不可重疊的序列碼檢測器