0 引言

靜態(tài)隨機訪問存儲器(SRAM)最初作為CPU與內(nèi)存之間的緩存。近年來已廣泛應用于高性能通信網(wǎng)絡、便攜式設備以及SOC系統(tǒng)中,呈現(xiàn)出向高速器件與低功耗性能方向發(fā)展的趨勢。因此,設計高速低功耗的SRAM已成為現(xiàn)在SRAM技術的主流方向。靈敏放大器是SRAM的重要組成部分,它將位線上的微小信號差迅速放大到全擺幅模式,從而有效減小數(shù)據(jù)的讀出延遲,同時由于不需要對位線電容完全充放電,因此也在某種程度上降低了功耗。所以,對高性能靈敏放大器進行設計是得到高速低功耗SRAM的一個有效途徑。根據(jù)對位線上要進行處理的信號類型的不同,靈敏放大器可分為電壓型靈敏放大器和電流型靈敏放大器。由于電流型靈敏放大器直接檢測位線上的電流變化,不需要轉(zhuǎn)化為電壓信號,因此在速度上更具有優(yōu)勢,可滿足高速的要求。針對不同的應用層面,目前出現(xiàn)了多種電流型靈敏放大器的設計結構:有源負載PBT結構,其優(yōu)點是輸出不受電源電壓及偏置電壓的影響;基于電流鏡結構的電流靈敏放大器,可以應用在低壓非易失存儲器中;為了消除位線噪聲電流,而提出的采用位線漏電流補償技術的電流型靈敏放大器;單端偽差分電流靈敏放大器,旨在改善SRAM讀出操作時的穩(wěn)定性及延遲;為降低功耗而提出的由兩級放大(全局和局部放大)構成的全電流模式靈敏放大器以及APD靈敏放大器。

本文在分析目前廣泛應用的電流型靈敏放大器的基礎上,提出了一種改進型的結構,以提高靈敏放大器的速度為主要目標,兼顧考慮功耗,以實現(xiàn)速度和功耗之間合理的折衷。

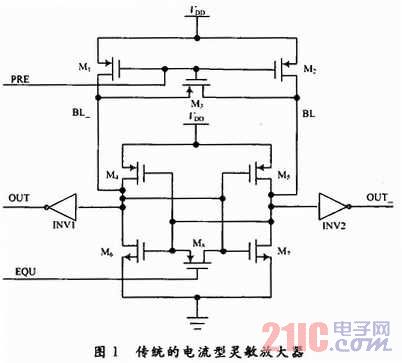

1 傳統(tǒng)的電流型靈敏放大器

傳統(tǒng)的電流型靈敏放大器是由4個晶體管構成的交叉耦合反相器單元,位線信號從漏極輸入,經(jīng)正反饋放大,再由漏極輸出,電路如圖1所示。靈敏放大器有2個工作階段:預充電和信號放大階段。預充電時,2個上拉P管將位線電壓拉至VDD,同時平衡管(M3)開啟,使位線電壓近似相等;當靈敏放大器使能信號有效時,便進入放大階段,檢測到位線上電流的變化差值并放大輸出。

![]()

2 改進的電流型靈敏放大器

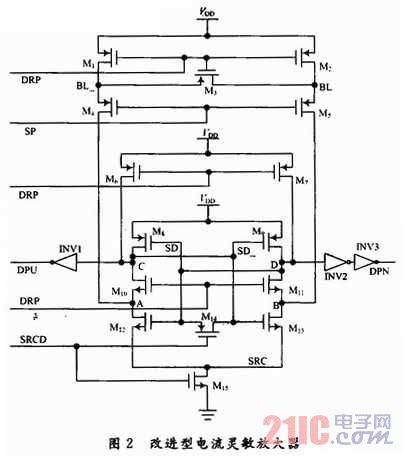

上述分析的靈敏放大器的輸入和輸出共用同一個端口,容易相互產(chǎn)生串擾,造成輸出結果錯誤,并且當該端口作為輸出端時,由于位線寄生電容較大,會浪費部分時間在對該電容進行充放電上,由靈敏放大器的延遲公式即式(1)可以看出,當位線電容Cbit增大時,延遲Td也將變大,不利于高速靈敏放大器的設計。所以可在原有電路結構的基礎上添加一對隔離管,并對外圍電路做一改進,具體結構如圖2所示。

當靈敏放大器進行放大時,隔離管(M10和M11)開啟,信號輸入和輸出端被隔斷,輸出時可以不必考慮端口的寄生電容,因此有效提高了靈敏放大器的速度;并且當靈敏放大器處于預充狀態(tài)時,隔離管關閉,這樣反相器的P管和N管就被隔離開,之間沒有通路,也就沒有漏電流,從而降低了電路的功耗。

另外電流型靈敏放大器的輸入為電流信號,故不需要在位線上建立較大的電壓差,即可快速放大差值信號。因此,從動態(tài)功耗即式(2)及式(1)可以看出,小的電壓擺幅△Vs可使電流型靈敏放大器的功耗與延遲同時減小。

![]()

此外,對靈敏放大器的時序控制也非常重要。若時序設置不當,有可能會造成靈敏放大器的讀出錯誤,相反若設計得當,不僅可以減小數(shù)據(jù)的讀出延遲,還可以有效地降低靈敏放大器的功耗。因此,需要對這部分做一特別考慮。

2.1 靈敏放大器的工作過程

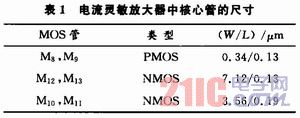

在預充電階段,DRP為“0”,此時M1,M2,M3,M6,M7管導通,M10,M11管關斷,位線BL和BL被上拉至電源電壓VDD,平衡管M3使兩邊的位線電壓處于近似相等的狀態(tài)。同時交叉耦合反相器的輸出端C,D也被上拉至VDD,使得在預充電時DPU為“0”,DPN為“1”。M4和M5管為電流傳輸管,由信號SP控制,在預充電時,SP為低電平,M4、M5導通,電流通過這2個管傳輸?shù)紸、B端,等待放大信號的到來。M10,M11關閉,將放大通路阻斷,此時靈敏放大器使能信號SRCD為低,M14導通,使C,D兩端電壓相互平衡,M15則關閉,從而切斷了電源到地之間的通路,使得靈敏放大器在預充電時沒有漏電流,進而降低了電路的功耗。這一階段是準備階段,即靈敏放大器為下一個放大操作做準備的過程。在放大模式下,首先DRP跳變?yōu)?ldquo;1”,結束預充電過程,同時M10、M11管導通。隨后SRCD變?yōu)楦唠娖剑琈16管導通,M14關閉,放大通路由此形成。之后SP變?yōu)楦唠娖剑瑢㈦娏鱾鬏敼荜P閉,此時A,B端之間的微小電流信號差通過正反饋被迅速放大成全擺幅的邏輯信號。當被放大的輸出信號穩(wěn)定后,靈敏放大器將重新進入到預充電狀態(tài)。在整個靈敏放大器電路中,M8、M9、M12和M13管構成的交叉耦合反相器是核心,其管子尺寸直接影響放大器的速度。因此,還需適當調(diào)整這4個管的尺寸從而最大化的提高靈敏放大器的速度。表1為核心管子的尺寸。

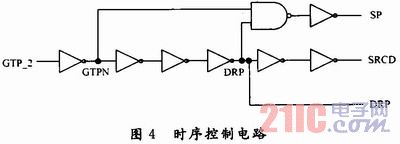

2.2 時序控制電路

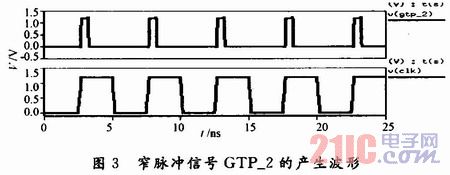

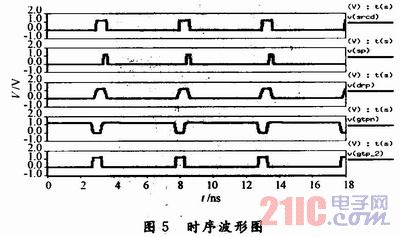

該靈敏放大器的時序控制信號包括:預充電控制信號DRP、電流傳輸信號SP、靈敏放大器使能信號SRCD。在外部看,整個靈敏放大器的時序基于一個GTP_2信號,該信號是由外部時鐘CLK產(chǎn)生的同步脈沖,即通過反饋把周期的時鐘信號變成一個周期的窄脈沖信號GTP_2,從圖3的波形中可以明顯看出。用該脈沖代替CLK控制SRAM的讀寫操作,可以盡可能地減少晶體管的開啟時間,從而有效降低了電路的功耗。

由于預充是為放大做準備的階段,因此預充電控制信號DRP要先于其它所有信號,以便在其它信號到來之前先對電路進行充電。在DRP跳變?yōu)楦唠娖街埃娏鱾鬏斝盘朣P以及使能SRCD都為低電平,SP為低保證位線高電平已傳輸至A、B端,而SRCD為低則將平衡管M14開啟。當電路進入到放大狀態(tài)時,DRP變?yōu)楦唠娖剑瑸榱吮WC位線電壓被充分傳輸至A、B兩端,SP應在DRP跳變后再變?yōu)楦唠娖健6谶M行信號放大之前,應使SRCD為高,關閉平衡管同時開啟尾電流源,并且關斷M14一定是在打開隔離管M10和M11之后進行的,因為若立即關斷平衡管,放大器兩邊輕微的失配就會觸發(fā)正反饋進行工作,從而導致讀出結果的錯誤。因此,信號SRCD可由DRP經(jīng)過反相器鏈延遲后形成,同時SRCD應先于SP變高,并且SP的高電平只需持續(xù)到下一次預充準備時,即DRP變?yōu)榈碗娖綍r,所以SP可由DRP和GTP_2的反信號相與產(chǎn)生。圖4即為控制該靈敏放大器工作的時序電路,由該電路產(chǎn)生的波形如圖5所示。

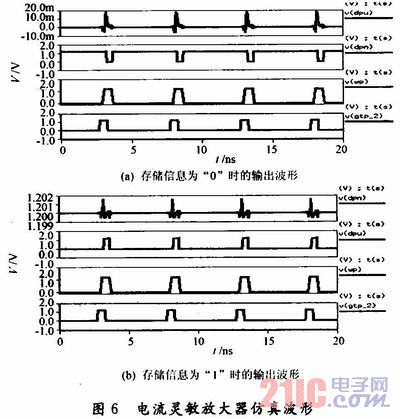

3 仿真結果

本設計采用SMIC 0.13μm數(shù)字工藝在HSpice下進行仿真,在位線BL和BL_上各加1個1 pF的電容來模擬大容量SRAM電路中的位線電容,并添加一個六管的存儲單元,輸出端各加1個50 pF的負載電容,字線WP用窄脈沖控制,仿真時工作電壓設為1.2 V,溫度為室溫。

圖6為改進后的電流型靈敏放大器的實際仿真波形。從圖中可以看出,在圖4時序電路的控制下,靈敏放大器的實際工作過程完全符合上述分析。如圖6(a),在預充電時由于位線被上拉至VDD,所以輸出DPN為高電平,而DPU為低電平;放大時,由于存儲單元存儲的信息為“0”,所以BL一側對寄生電容放電后電流略微減小進而與BL_側形成電流差值,之后由正反饋迅速放大,在輸出DPN端得到全擺幅的邏輯電平“0”,存儲數(shù)據(jù)被正確讀出。圖6(b)為存儲單元存儲信息為“1”時的輸出波形,分析同上,最后是在DPU端得到全擺幅的邏輯電平“1”。

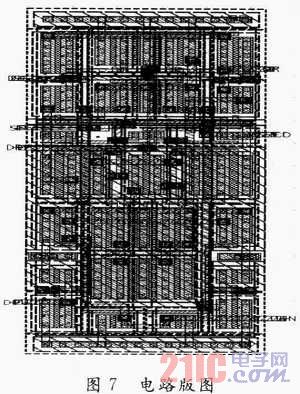

改進型電流靈敏放大器的版圖如圖7所示,面積為82.39μm2。版圖設計時特別考慮了器件的匹配性以及布局布線的合理性,盡可能減小寄生效應對電路性能的影響。對該靈敏放大器進行后仿真,結果顯示其放大延遲為0.344 ns,平均功耗為102μW。由此可見,本文設計的改進型的電流靈敏放大器可以實現(xiàn)高速低功耗的要求。

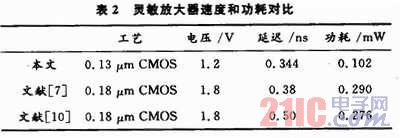

在工藝條件及工作電壓相近的前提下,將本文的靈敏放大器與文獻中提到的幾種靈敏放大器在速度和功耗上進行比較,見表2。結果表明,本文提出的改進型電流靈敏放大器無論在速度,還是在功耗上都較其它靈敏放大器更具有優(yōu)勢。速度為0.344 ns,與文獻提出的電流型靈敏放大器相比提高了9.47%,比文獻所示的放大器則提高了31.2%;功耗則較兩者分別降低了64.8%和63%。

4 結語

本文提出了一款改進的電流型靈敏放大器,其優(yōu)勢在于讀取速度快,功耗低,并且適合在低壓下工作。與文獻提出的電流靈敏放大器相比,速度分別提高了9.47%和31.2%,而功耗則降低了64.8%和63%。由于電流型靈敏放大器輸入阻抗小,并且本文在原有的基礎上加了一對隔離管,使得輸出不受負載電容的影響,同時優(yōu)化了四個核心管的尺寸,進而有效提高了靈敏放大器的速度;此外,對放大器的時序控制電路也做了細致合理的設置,在完成放大的基礎上盡量減少管子的開啟時間,從而減小靜態(tài)電流,達到了降低功耗的目的。因此,該靈敏放大器完全滿足高速低功耗的需求,更適合低電壓,大容量SRAM的應用。