摘要:為建立高速、高效、合理的CCD成像軟件系統(tǒng),設(shè)計TDI-CCD成像系統(tǒng)自頂向下的軟件設(shè)計結(jié)構(gòu)和模塊化設(shè)計方法,實現(xiàn)成像系統(tǒng)FPGA軟件解耦合,給出整體軟件設(shè)計結(jié)構(gòu)及其性能分析;在系統(tǒng)調(diào)試階段運行良好。實際運行結(jié)果表明,該軟件得各項性能指標達到設(shè)計要求。

關(guān)鍵詞:FPGA;CCD成像;模塊設(shè)計;解耦分析

CCD是一種廣泛應(yīng)用于成像系統(tǒng)中的光學傳感器,TDI-CCD利用延時積分的方法,通過對同一物體多次曝光,實現(xiàn)增強型光能采集的目的。同時,根據(jù)像移補償?shù)乃俣龋O(shè)計TDI-CCD的電荷轉(zhuǎn)移速率,能夠?qū)崿F(xiàn)電子學像移補償。本文闡述的成像系統(tǒng)以TDI-CCD為核心,利用FPGA實現(xiàn)CCD圖像數(shù)據(jù)整合功能的硬件系統(tǒng)。由于FPGA在資源、速度、效率、穩(wěn)定性等方面有很多優(yōu)勢,因此,采用FPGA實現(xiàn)高速、大規(guī)模、繼承性好的成像軟件,通過在軟件結(jié)構(gòu)、模塊和設(shè)計方法上的優(yōu)化,尋求更加合理設(shè)計方案,達到功能和性能的提升。本文將FPGA設(shè)計的一些指導(dǎo)性原則應(yīng)用于實際的系統(tǒng)設(shè)計中,給出了FPGA自頂向下的軟件結(jié)構(gòu)劃分,以及程序設(shè)計中的注意事項。通過對模塊接口信號的解耦處理,增強了系統(tǒng)的適應(yīng)性和穩(wěn)定性,該軟件系統(tǒng)在實際工程中已進行驗證。

1 成像系統(tǒng)結(jié)構(gòu)

成像系統(tǒng)以TDI-CCD為核心,采用FPGA作為核心數(shù)據(jù)處理單元,實現(xiàn)數(shù)據(jù)處理傳輸,其基本組成部分如圖1所示。

時序驅(qū)動單元采用FPGA產(chǎn)生驅(qū)動時序,通過硬件電路實現(xiàn)對CCD控制信號驅(qū)動;焦平面單元將CCD視頻信號經(jīng)過預(yù)放、濾波、相關(guān)雙采樣(CDS)、A/D轉(zhuǎn)換后輸入到圖像處理單元;圖像處理單元接收控制器指令,完成總體對成像系統(tǒng)的控制,以及圖像數(shù)據(jù)的整合傳輸?shù)裙δ埽?br />

2 成像軟件設(shè)計

成像系統(tǒng)軟件采用FPGA實現(xiàn)。軟件核心是圖像處理單元。該單元接收CCD行同步信號以及指令,完成數(shù)據(jù)處理功能;

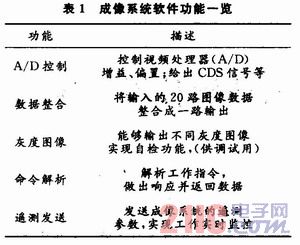

成像系統(tǒng)FPGA的主要功能如表1所示。成像系統(tǒng)在物理上分為3個電箱。圖像處理電箱獨立存在,并接收焦平面電箱的視頻信號和控制電箱工作指令,實現(xiàn)數(shù)據(jù)處理。根據(jù)系統(tǒng)邏輯功能劃分FPGA軟件結(jié)構(gòu),并將軟件設(shè)計規(guī)范應(yīng)用其中,優(yōu)化系統(tǒng)性能。圖像處理單元工作頻率高,數(shù)據(jù)處理復(fù)雜,不同的結(jié)構(gòu)劃分和設(shè)計方式對性能影響較大,因此,本文對圖像處理軟件設(shè)計進行詳細闡述。

2.1 FPGA軟件設(shè)計分析

可編程邏輯設(shè)計原則的合理應(yīng)用,為理解FPGA程序設(shè)計,實現(xiàn)高效、穩(wěn)定的數(shù)字系統(tǒng)提供了條件。

(1)資源與速率的平衡。資源和速率是FPGA設(shè)計的重要指標。通過合理的軟件結(jié)構(gòu)劃分,在高速數(shù)據(jù)處理區(qū)域采用速度優(yōu)先方法,即通過模塊復(fù)用、串/并轉(zhuǎn)換、數(shù)據(jù)流水化等方法實現(xiàn)高速數(shù)據(jù)傳輸;在低速處理區(qū)域,采用串行方式和組合邏輯,通過增加扇出實現(xiàn)資源的最優(yōu)化。

(2)系統(tǒng)與硬件匹配。FPGA內(nèi)部硬件資源決定設(shè)計的結(jié)構(gòu)和方法。采用BLOCK RAM或Distributed RAM,根據(jù)數(shù)據(jù)處理內(nèi)容、資源利用率要求決定使用方式;另外,利用全局信號線,實現(xiàn)全局變量處理;利用FPGA內(nèi)部IP和原語實現(xiàn)程序設(shè)計,改善程序架構(gòu)。

(3)同步設(shè)計。同步設(shè)計是資源與速度的體現(xiàn),在異步時鐘域數(shù)據(jù)處理時,采用FIFO轉(zhuǎn)存,解決同頻異相或異頻問題,實現(xiàn)數(shù)據(jù)讀取和傳輸。

(4)可靠性設(shè)計。軟件設(shè)計采用冗余和容錯性設(shè)計、簡化設(shè)計規(guī)模和減少軟件配置項;

2.2 圖像數(shù)據(jù)處理與分析

2.2.1 數(shù)據(jù)率和時鐘選擇

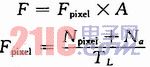

CCD圖像輸出數(shù)據(jù)率計算如下:

式中:F為輸出數(shù)據(jù)率;Fpixel為CCD像元轉(zhuǎn)移速率;A為量化等級;Npixel為像元數(shù);Na為啞像元數(shù);TL為行周期。根據(jù)指標計算,成像系統(tǒng)的數(shù)據(jù)率達到1 Gb/s以上,因此,數(shù)據(jù)傳輸采用10 b數(shù)據(jù)并行方式,滿足軟硬件設(shè)計預(yù)定的指標要求。

2.2.2 時鐘域分析

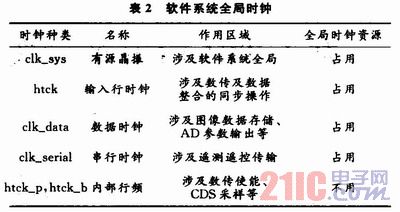

CCD圖像處理單元,主時鐘采用120 MHz有源晶振(elk_sys),通過FPGA內(nèi)部全局時鐘網(wǎng)絡(luò)(BUFG)實現(xiàn)全局走線;設(shè)計時不建議使用DCM。系統(tǒng)的主要時鐘如表2所示。

系統(tǒng)接收外部行同步時鐘,通過高頻主時鐘同步,并在FPGA內(nèi)產(chǎn)生內(nèi)部行頻,用于產(chǎn)生CDS信號及控制邏輯。通過分頻產(chǎn)生串行時鐘,完成遙控遙測信號的收發(fā);產(chǎn)生數(shù)據(jù)時鐘,完成數(shù)據(jù)采樣和傳輸;

2.2.3 成像系統(tǒng)軟件結(jié)構(gòu)及功能實現(xiàn)

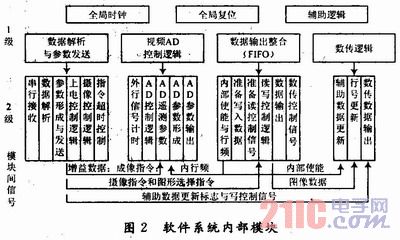

根據(jù)軟件系統(tǒng)功能,自頂向下劃分模塊,如圖2所示。為了保證模塊間信號的獨立性,增強了模塊解耦處理,具體的處理原則是:減少模塊IO數(shù)量,減少邏輯關(guān)聯(lián)程度,避免信號控制環(huán)路產(chǎn)生;存儲器與后續(xù)數(shù)據(jù)處理操作整合;模塊間避免數(shù)據(jù)傳輸,減少異步時鐘域的數(shù)據(jù)同步問題;采用脈沖電平邏輯實現(xiàn)模塊控制等。由于合理劃分了軟件模塊,方便了模塊化設(shè)計和仿真驗證,為后續(xù)的工作奠定了堅實的基礎(chǔ)。圖2中三級模塊沒有具體給出。

(1)數(shù)據(jù)解析模塊。通過RS 422解析串行指令,同時完成部分硬指令翻譯,并根據(jù)指令要求發(fā)送系統(tǒng)遙測參數(shù)。串行接收數(shù)據(jù)采用累加校驗,并對接收數(shù)據(jù)進行預(yù)存儲。校驗正確后,將數(shù)據(jù)以乒乓方式存入RAM,以保證讀/寫邏輯不沖突;校驗錯誤時,不轉(zhuǎn)存數(shù)據(jù)。根據(jù)不同的指令類型,對相應(yīng)的地址進行讀/寫操作,更新完畢后給出標志位。

(2)視頻控制模塊。輸出A/D參數(shù)、CDS信號和A/D輸出時鐘。A/D參數(shù)采用廣播方式,通過使能信號完成20路AD的配置;由外行信號htck同步A/D的控制邏輯以及CDS信號;由于數(shù)據(jù)處理速度較低,實現(xiàn)時,通過增加扇出、減少模塊復(fù)用,來降低資源利用率。CDS采樣脈沖的位置對信號質(zhì)量影響很大,需要精細調(diào)節(jié)。在設(shè)計時,采用FPGA內(nèi)部移位寄存器生成不同位置的采樣脈沖,在調(diào)試中實現(xiàn)精確對準。

(3)數(shù)據(jù)整合模塊。將輸入的20路圖像數(shù)據(jù)整合一路輸出。根據(jù)工作指令選擇灰度圖像或?qū)崟r圖像,并行存儲到相應(yīng)的fifo中;輸出時,通過控制讀使能信號,實現(xiàn)數(shù)據(jù)的循環(huán)讀取。設(shè)計FIFO時,仍然采用乒乓方式,通過標志信號使讀寫邏輯分離。相比RAM設(shè)計而言,避免了大規(guī)模地址線造成的亞穩(wěn)態(tài)問題,設(shè)計時序相對簡單。

(4)數(shù)據(jù)輸出模塊。根據(jù)衛(wèi)星指令將圖像數(shù)據(jù)按照規(guī)定格式輸出。設(shè)計時,需要注意數(shù)傳協(xié)議中各數(shù)據(jù)段數(shù)據(jù)的輸出時序。因此,良好的模塊規(guī)劃,更有利于程序的實現(xiàn)和驗證。

2.3 性能與設(shè)計要點

(1)FPGA內(nèi)部時鐘域分析有利于同步設(shè)計的實現(xiàn),在良好的時鐘分配下,能夠提高系統(tǒng)運行頻率,增加軟件可靠性。根據(jù)FPGA資源說明,每個slice有固定數(shù)量的觸發(fā)器和查找表(LUT)資源,合理利用可以降低器件資源的利用率。

(2)組合邏輯容易產(chǎn)生亞穩(wěn)態(tài),為系統(tǒng)帶來不確定因素,同時,組合邏輯延時也限制了系統(tǒng)的運行頻率。在頻率要求較高的模塊內(nèi)部,可以采用流水線技術(shù)降低組合邏輯規(guī)模。

(3)軟件結(jié)構(gòu)對系統(tǒng)性能和資源使用有很大的影響;不合理的結(jié)構(gòu)劃分不僅浪費資源,也不利于軟件的升級和維護。該軟件通過合理的結(jié)構(gòu)和接口信號劃分,力求達到模塊解耦的目的。通過詳細的接口時序說明,可以更好的進行軟件維護和更新,為后續(xù)開發(fā)奠定基礎(chǔ)。

2.4 關(guān)于軟件系統(tǒng)工作頻率和硬件速度的匹配

電路設(shè)計時,通過分析硬件電路的芯片參數(shù)和電路延時指導(dǎo)軟件設(shè)計。對于關(guān)鍵信號走線,除了可以在硬件上設(shè)置延時線外,F(xiàn)PGA內(nèi)部可以通過DLL倍頻時鐘,通過時鐘計數(shù)方式實現(xiàn)延時,或者通過FPGA內(nèi)部LUT和門邏輯實現(xiàn)組合邏輯延時設(shè)計。由于FPGA的端口速率有限,不同等級的FPGA芯片的處理速度也不同,因此,需要參考FPGA的參數(shù)特性設(shè)計系統(tǒng)結(jié)構(gòu),并確定端口數(shù)傳規(guī)則和內(nèi)部結(jié)構(gòu),同時,注意與外圍

硬件的匹配,以保證軟硬件可靠運行。

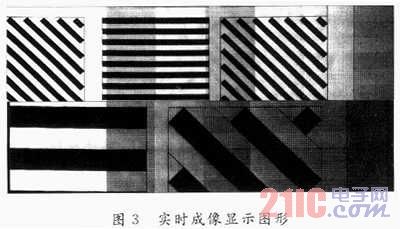

3 實時圖像效果評估

圖3給出了實驗室條件下的原始數(shù)據(jù)圖像。通過調(diào)整信號處理器的增益,調(diào)整相應(yīng)抽頭的灰度值,從而達到灰度均衡效果;通過觀察相應(yīng)的圖像數(shù)據(jù)可以得出,數(shù)據(jù)處理和成像效果達到預(yù)定指標要求。

4 結(jié)語

FPGA成像軟件是系統(tǒng)可靠運行的重要保障,其性能對整體分辨率的提高有著舉足輕重的作用。在給定的硬件條件下,通過高效設(shè)計FPGA軟件,能夠顯著提高系統(tǒng)性能。在成像軟件的數(shù)據(jù)處理方法上,仍然有很多方向,如實時圖像壓縮傳感,提高系統(tǒng)的傳輸能力;在FPGA內(nèi)部進行海量數(shù)據(jù)處理等。通過實驗證明,該軟件的實際運行速度達到要求。因為硬件處理速度的限制,若想提高軟件運行頻率,尋求更加合理的軟件系統(tǒng)結(jié)構(gòu)以及電子學分系統(tǒng)結(jié)構(gòu)將成為重要的研究內(nèi)容。