摘要:步進(jìn)電機(jī)是一種將電脈沖轉(zhuǎn)化為角位移的執(zhí)行機(jī)構(gòu),已廣泛應(yīng)用于各種自動(dòng)化控制系統(tǒng)中。為了提高對(duì)步進(jìn)電機(jī)的細(xì)分要求,提出了基于FPGA控制的步進(jìn)電機(jī)控制器方案。給出了用VHDL語(yǔ)言層次化設(shè)計(jì)各功能模塊的過(guò)程,利用QuartusⅡ進(jìn)行仿真,給出了仿真結(jié)果,并成功地在FPGA器件上驗(yàn)證了設(shè)計(jì)的可能性。采用FPGA器件和VHDL語(yǔ)言,只需修改模塊程序參數(shù),而無(wú)須修改硬件電路就能實(shí)現(xiàn)各種控制。該設(shè)計(jì)硬件結(jié)構(gòu)簡(jiǎn)單可靠,可根據(jù)實(shí)踐需要靈活方便進(jìn)行配置。

關(guān)鍵詞:步進(jìn)電機(jī);FGPA;控制器;QuartusⅡ

步進(jìn)電機(jī)是數(shù)字控制電機(jī),它將脈沖信號(hào)轉(zhuǎn)變成角位移,即給一個(gè)脈沖信號(hào),步進(jìn)電機(jī)就轉(zhuǎn)動(dòng)一個(gè)角度,因此非常適合對(duì)數(shù)字系統(tǒng)的控制。由于工業(yè)技術(shù)的不斷進(jìn)步,諸如自動(dòng)化控制、精密機(jī)械加工、航空航天技術(shù),以及所有要求高精度定位、自動(dòng)記錄、自動(dòng)瞄準(zhǔn)等的高新技術(shù)領(lǐng)域?qū)Σ竭M(jìn)電機(jī)的細(xì)分要求越來(lái)越高。實(shí)踐證明。步進(jìn)電機(jī)的細(xì)分驅(qū)動(dòng)技術(shù)可以減小步進(jìn)電機(jī)的步距角,提高電機(jī)運(yùn)行的平穩(wěn)性,增加控制的靈活性等。采用FPGA控制步進(jìn)電機(jī),利用其中的EAB可以構(gòu)成存放電機(jī)各相電流所需的控制波形數(shù)據(jù)表,利用FPGA設(shè)計(jì)的數(shù)字比較器可以同步產(chǎn)生多路PWM電流波形,并對(duì)多相步進(jìn)電機(jī)進(jìn)行靈活控制。當(dāng)改變控制波形表的數(shù)據(jù),增加計(jì)數(shù)器的位數(shù),提高計(jì)數(shù)精度后,就可以對(duì)

步進(jìn)電機(jī)的步進(jìn)轉(zhuǎn)角進(jìn)行任意細(xì)分,從而實(shí)現(xiàn)步進(jìn)轉(zhuǎn)角的精確控制。

1 步進(jìn)電機(jī)細(xì)分驅(qū)動(dòng)控制器工作原理

圖1是步進(jìn)電機(jī)細(xì)分驅(qū)動(dòng)控制器系統(tǒng)框圖。該系統(tǒng)由PWM計(jì)數(shù)器,波形ROM地址計(jì)數(shù)器,PWM波形ROM存儲(chǔ)器、比較器、功放電路等緝成。其中,PWM計(jì)數(shù)器在脈寬時(shí)鐘的作用下遞增計(jì)數(shù),產(chǎn)生階梯形上升的周期性鋸齒波,同時(shí)加載到各數(shù)字比較器的一端;PWM波形ROM輸出的數(shù)據(jù)A[3..0],B[3..0],C[3..0],D[3..0]分別加載到各數(shù)字比較器的另一端。當(dāng)PWM計(jì)數(shù)器的計(jì)數(shù)值小于波形ROM輸出的數(shù)值時(shí),比較器輸出低電平,當(dāng)PWM計(jì)數(shù)器的計(jì)數(shù)值大于波形ROM輸出數(shù)值時(shí),比較器輸出高電平。由此可輸出周期性的PWM波形。根據(jù)步進(jìn)電機(jī)8細(xì)分電流波形的要求,將各個(gè)時(shí)刻的細(xì)分電流波形所對(duì)應(yīng)的數(shù)值存放于波形ROM中,波形ROM的地址由地址計(jì)數(shù)器產(chǎn)生。通過(guò)對(duì)地址計(jì)數(shù)器進(jìn)行控制,可以改變步進(jìn)電機(jī)的旋轉(zhuǎn)方向、轉(zhuǎn)動(dòng)速度、工作/停止?fàn)顟B(tài)。FPGA產(chǎn)生的PWM信號(hào)控制各功率管驅(qū)動(dòng)電路的導(dǎo)通和關(guān)斷,其中PWM信號(hào)隨ROM數(shù)據(jù)而變化,改變輸出信號(hào)的占空比,即可實(shí)現(xiàn)限流及細(xì)分控制,最終使電機(jī)繞組呈現(xiàn)階梯形變化,從而實(shí)現(xiàn)步距細(xì)分的目的。輸出細(xì)分電流信號(hào)采用FPGA中LPM_ROM查表法,它是通過(guò)在不同地址單元內(nèi)寫(xiě)入不同的PWM數(shù)據(jù),用地址選擇來(lái)實(shí)現(xiàn)不同通電方式下的可變步距細(xì)分。

2 步進(jìn)電機(jī)細(xì)分驅(qū)動(dòng)控制器的FPGA實(shí)現(xiàn)

2.1 系統(tǒng)功能設(shè)計(jì)

運(yùn)用自上而下(top-down)的設(shè)計(jì)思路,將系統(tǒng)按功能逐層分割實(shí)現(xiàn)層次化設(shè)計(jì)。根據(jù)步進(jìn)電機(jī)細(xì)分控制框圖,將該系統(tǒng)分為PWM計(jì)數(shù)器(CNT8)、地址計(jì)數(shù)器(CNT24)、DEC2、PWM波形ROM、數(shù)字比較器(CMP3)、數(shù)據(jù)選擇器(BUSMUX)6個(gè)功能模塊,前3個(gè)模塊用VHDL語(yǔ)言編程描述各模塊的接口及電路功能;后3個(gè)模塊可選擇LPM庫(kù)中的適當(dāng)模塊,并為其設(shè)定適當(dāng)?shù)膮?shù),以滿足自己的需要。因而可在自己的項(xiàng)目中十分方便地調(diào)用優(yōu)秀電子工程技術(shù)人員的硬件設(shè)計(jì)成果。

CNT8是PWM計(jì)數(shù)器,在時(shí)鐘脈沖作用下遞增計(jì)數(shù),以產(chǎn)生階梯形上升的周期性鋸齒波,同時(shí)加載到四相步進(jìn)電機(jī)各相數(shù)字比較器的一端。圖2為它的仿真波形。

CNT24是可逆計(jì)數(shù)器,其U-D端即加減控制端作為控制電機(jī)正反轉(zhuǎn)的方向控制端。高電平時(shí)計(jì)數(shù)器加計(jì)數(shù),電動(dòng)機(jī)正轉(zhuǎn);低電平時(shí)計(jì)數(shù)器減計(jì)數(shù),電動(dòng)機(jī)反轉(zhuǎn)。計(jì)數(shù)器的模應(yīng)該等于電動(dòng)機(jī)運(yùn)行1個(gè)周期的拍數(shù)或拍數(shù)的整數(shù)倍(該處模等于32)。仿真波形如圖3所示。

DEC2為無(wú)細(xì)分時(shí)的電機(jī)控制模塊,控制雙四拍時(shí)的正反轉(zhuǎn)。

步進(jìn)電機(jī)的正、反轉(zhuǎn)控制可通過(guò)改變步進(jìn)電機(jī)各繞組的通電順序來(lái)改變轉(zhuǎn)向,當(dāng)四相雙四拍步進(jìn)電機(jī)的通電順為AB→BC→CD→DA→AB…時(shí),電機(jī)正轉(zhuǎn);當(dāng)其繞組按AD→DC→CB→BA→AD…的順序通電時(shí),電機(jī)反轉(zhuǎn)。因此,利用case語(yǔ)句編程來(lái)改變輸出脈沖的順序,以此改變步進(jìn)電機(jī)繞組的通電順序。用‘1’表示該繞組加電;用‘0’表示該繞組斷電。

圖4為DEC2反轉(zhuǎn)時(shí)的仿真波形。

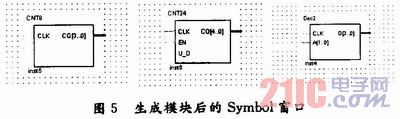

2.2 利用VHDL文件生成元器件

工程創(chuàng)建好以后,就可以用設(shè)計(jì)好的VHDL語(yǔ)言文件生成工程模塊。首先打開(kāi)CNT8.vhd文件,點(diǎn)擊菜單中File→Create/Update→Crea-te Symbol Files forCurrent File命令,以生成圖5所示CNT8模塊。

按照同樣的方法生成CNT24和DEC2模塊。將這些模塊包裝為一個(gè)symbol,以備總模塊調(diào)用,如圖5所示。

2.3 原理圖輸入設(shè)計(jì)

2.3.1 PWM_1.mif文件的設(shè)計(jì)

在設(shè)計(jì)控制器前,必須首先完成存放PWM波形的ROM存儲(chǔ)器設(shè)計(jì),而在此之前還必須定制LPM_ROM初始化數(shù)據(jù)文件,如圖6所示。

2.3.2 ROM存儲(chǔ)器的設(shè)計(jì)

mif文件建好以后就可以進(jìn)入ROM存儲(chǔ)器的設(shè)計(jì)。

設(shè)計(jì)好的rom3模塊如圖7所示。

2.3.3 定制模塊

調(diào)用LPM庫(kù)中的模塊,定制BUSMUX(參數(shù)化多路數(shù)據(jù)選擇器)元件和lpm_compare0元件。

如圖8所示,數(shù)據(jù)選擇器通過(guò)模式選擇信號(hào),再根據(jù)不同的模式功能選擇該功能模塊的信號(hào)輸出。該模塊的輸入信號(hào)有模式選擇信號(hào)sel[0],即非細(xì)分控制和模式選擇信號(hào)sel[1],即細(xì)分控制。當(dāng)sel為“0”時(shí),對(duì)應(yīng)的為非細(xì)分控制輸出,即由DEC2輸出,此時(shí)步進(jìn)電機(jī)按照雙四拍模式運(yùn)行;當(dāng)sel為“1”時(shí),對(duì)應(yīng)的為細(xì)分控制輸出,即由比較器CMP3輸出,此時(shí)步進(jìn)電機(jī)按照細(xì)分8拍模式運(yùn)行。

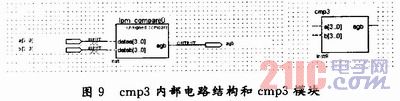

調(diào)用LPM庫(kù)中的模塊,定制一個(gè)lpm_compare0元件,然后在lpm_compare0的輸入/輸出端接入輸入/輸出信號(hào),并將這些模塊包裝為一個(gè)symbol,以備總模塊調(diào)用,如圖9所示。

2.3.4 各模塊集成

各功能模塊設(shè)計(jì)完成后,用原理圖的輸入法生成總的功能模塊,實(shí)現(xiàn)設(shè)計(jì)功能,最后生成的頂層電路圖如圖10所示。

3 系統(tǒng)調(diào)試

3.1 步進(jìn)電機(jī)總模塊時(shí)序仿真調(diào)試及分析

總模塊在QuartusⅡ6.1軟件環(huán)境下編譯通過(guò),再進(jìn)行總體仿真。

圖11中各信號(hào)的定義為u_d為步進(jìn)電機(jī)正、反轉(zhuǎn)控制;clock0為步進(jìn)電機(jī)轉(zhuǎn)動(dòng)速度控制;clock5為PWM計(jì)數(shù)時(shí)鐘;s=1為細(xì)分;s=0為非細(xì)分。Y[3..0]分別對(duì)應(yīng)步進(jìn)電機(jī)的4個(gè)相,即DP,CP,BP,AP;s為選擇細(xì)分控制。

圖11給出了步進(jìn)電機(jī)無(wú)細(xì)分仿真波形圖。圖12給出了步進(jìn)電機(jī)從A相(1000即8)→AB相(1100即12)→B相(0100即4)→BC相(0110即6)→相C(0010即2)→CD相(0010即3)→D相(0001即1)→DA相(1001即9)→…的工作過(guò)程仿真波形。通過(guò)圖12可以清楚地看到,首先步進(jìn)電機(jī)A相導(dǎo)通,B,C,D相截止;然后B項(xiàng)的數(shù)據(jù)逐漸增大,從1增大到4,電機(jī)中的磁場(chǎng)經(jīng)過(guò)4拍從A相轉(zhuǎn)到了AB相,再經(jīng)過(guò)4拍,A相的數(shù)據(jù)逐漸減小,電機(jī)中的磁場(chǎng)從AB相轉(zhuǎn)到B相。從A到AB再到B共經(jīng)過(guò)了8拍,實(shí)現(xiàn)了步距角的8細(xì)分。圖13給出了步進(jìn)電機(jī)反轉(zhuǎn)8細(xì)分仿真波形圖。

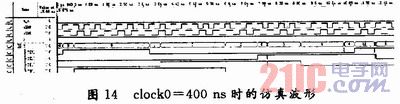

步進(jìn)電機(jī)的轉(zhuǎn)速取決于輸入的脈沖頻率。如果給步進(jìn)電機(jī)發(fā)一個(gè)控制脈沖,它就轉(zhuǎn)一步,再發(fā)一個(gè)脈沖,它會(huì)再轉(zhuǎn)一步。2個(gè)脈沖的間隔越短,步進(jìn)電機(jī)轉(zhuǎn)得越快。調(diào)整控制器發(fā)出的脈沖頻率,就可以對(duì)步進(jìn)電機(jī)進(jìn)行調(diào)速。從圖14可以看出,當(dāng)改變輸入脈沖clock0的周期時(shí),A,B,C,D四相繞組的高低電平寬度將發(fā)生變化,它將導(dǎo)致通電和斷電的變化速率發(fā)生變化,隨之使電機(jī)轉(zhuǎn)速發(fā)生變化。所以調(diào)節(jié)輸入脈沖的周期就可以控制步進(jìn)電機(jī)的運(yùn)動(dòng)速度。

由圖14與圖15的對(duì)比可知,通過(guò)減少clock0周期,步進(jìn)電機(jī)控制器的運(yùn)行速度明顯加快。通過(guò)以上對(duì)步進(jìn)電機(jī)的仿真分析可知,該設(shè)計(jì)實(shí)現(xiàn)了對(duì)步進(jìn)電機(jī)的各種基本控制。

3.2 下栽到實(shí)際FPGA器件上進(jìn)行工程調(diào)試

各模塊經(jīng)過(guò)編譯優(yōu)化后,就要選擇合適的目標(biāo)芯片進(jìn)行綜合、管腳配置。該系統(tǒng)選用Altera公司的高性價(jià)比Cyclone系列FPGA芯片,型號(hào)為EP1C6Q240C8,芯片在32 678 Hz下工作,將實(shí)驗(yàn)板GW48-PK3的JTAG PORT接口和下載接口USBBlaster用數(shù)據(jù)線連接,最后打開(kāi)板子的電源。

在該硬件環(huán)境中,通過(guò)鍵7可以控制步進(jìn)電機(jī)的正、反轉(zhuǎn),鍵8可以選擇步進(jìn)電機(jī)的細(xì)分/非細(xì)分功能,這證明該設(shè)計(jì)完成了步進(jìn)電機(jī)細(xì)分驅(qū)動(dòng)控制器的設(shè)計(jì)要求,最終取得了令人滿意的結(jié)果。

4 結(jié)語(yǔ)

該系統(tǒng)以FPGA為核心部件,根據(jù)步進(jìn)電機(jī)的工作原理,利用EDA技術(shù)實(shí)現(xiàn)了步進(jìn)電機(jī)的細(xì)分驅(qū)動(dòng)控制。采用VHDL語(yǔ)言并根據(jù)步進(jìn)電機(jī)的不同,改變模塊程序的參數(shù),實(shí)現(xiàn)不同型號(hào)的步進(jìn)電機(jī)控制。在系統(tǒng)設(shè)計(jì)過(guò)程中,力求硬件簡(jiǎn)單,并充分發(fā)揮VHDL語(yǔ)言軟件編程靈活方便和FPGA快速的特點(diǎn)來(lái)滿足系統(tǒng)設(shè)計(jì)要求,同時(shí)大大縮短系統(tǒng)的開(kāi)發(fā)時(shí)間和成本。