本文介紹一種利用復(fù)雜可編程邏輯器件給高速數(shù)據(jù)采集" title="高速數(shù)據(jù)采集">高速數(shù)據(jù)采集系統(tǒng)中的采集數(shù)據(jù)貼上精確時(shí)間標(biāo)簽的方法,并利用MAX PLUSⅡ開(kāi)發(fā)環(huán)境驗(yàn)證設(shè)計(jì)方案的正確性。此設(shè)計(jì)方案已經(jīng)成功地應(yīng)用到自行設(shè)計(jì)的高速數(shù)據(jù)采集卡中。

關(guān)鍵詞:ADuC812" title="ADuC812">ADuC812;時(shí)間標(biāo)簽;CPLD" title="CPLD">CPLD;GPS

A method of realizing precise time label in high-speed data acquisition system

Chen jing, Zhang Cheng-xue, Liu Yanhua

(School of Electrical Engineering, Wuhan University, 430072, Wuhan,China)

Abstract: This paper introduces a new method, using Complex Programmable Logic Device to attach a precise time label for sample data in very high-speed sample data system. It has used MAX PLUS II to simulate the function and it has been proved to be accurate. The system has been applied in high-speed data sample board, which has been designed successfully.

Key words:ADuC812;time laber;CPLD;global positioning system)GPS" title="GPS">GPS)

0 引言

基于GPS的雙端行波故障定位系統(tǒng)是利用行波的第一個(gè)波頭到達(dá)線路兩端的時(shí)間差來(lái)計(jì)算故障點(diǎn)的位置,由于行波的傳播速度非常快(約為光速的98%),這就對(duì)線路兩端行波波頭到達(dá)時(shí)刻的時(shí)間精度要求非常高。但相對(duì)于高速數(shù)據(jù)采集系統(tǒng)而言,單片機(jī)系統(tǒng)對(duì)時(shí)間的分辨能力是很低的(設(shè)51系列CPU的時(shí)鐘頻率為12MHz,則計(jì)數(shù)器(T0或T1)對(duì)時(shí)間的最小分辨能力為2μs)。而且單片機(jī)系統(tǒng)還不能直接地得到故障發(fā)生時(shí)對(duì)應(yīng)于靜態(tài)RAM的確切地址,所以如果只利用單片機(jī)系統(tǒng)給采集數(shù)據(jù)貼上時(shí)間標(biāo)簽,則時(shí)間精度和時(shí)間標(biāo)簽的可靠性會(huì)大大降低,這樣會(huì)直接影響到故障測(cè)距的精度。

1 相關(guān)內(nèi)容簡(jiǎn)介

1.1 GPS簡(jiǎn)介

全球定位系統(tǒng)(GPS)是美國(guó)于1993年全面建成并運(yùn)行的新一代衛(wèi)星導(dǎo)航、定位和授時(shí)系統(tǒng)。電力系統(tǒng)中主要是利用GPS的精確授時(shí)。GPS接收器在任意時(shí)刻能同時(shí)接收其視野范圍內(nèi)4~8顆衛(wèi)星信號(hào),其內(nèi)部硬件電路和處理軟件通過(guò)對(duì)接收到的信號(hào)進(jìn)行解碼和處理,能從中提取并輸出兩種時(shí)間信號(hào):一是時(shí)間間隔為1s的脈沖信號(hào)1PPS;二是經(jīng)串行口或RS-232輸出的與1PPS脈沖前沿對(duì)應(yīng)的國(guó)際標(biāo)準(zhǔn)時(shí)間和日期代碼(年、月、日、時(shí)、分、秒)[1]。

GPS接收器提供的1PPS信號(hào)實(shí)際上是以秒為計(jì)時(shí)單位、精度為1us的國(guó)際標(biāo)準(zhǔn)時(shí)間信號(hào),這種信號(hào)在地球上任何地方都能比較可靠地接收到。因此,若以該信號(hào)作為標(biāo)準(zhǔn)時(shí)鐘源去同步電網(wǎng)內(nèi)運(yùn)行的各時(shí)鐘,則能保證各廠站時(shí)鐘的高精確度同步運(yùn)行[1]。

1.2 ADuC812簡(jiǎn)介

ADuC812芯片是由美國(guó)AD(Analog Device)公司推出的微轉(zhuǎn)換器。它是一個(gè)完整的數(shù)據(jù)采集微系統(tǒng),它的組成為:一個(gè)8通道、5μs轉(zhuǎn)換時(shí)間、精度自校準(zhǔn)、12位精度、逐次逼近的ADC轉(zhuǎn)換器;兩個(gè)12位的數(shù)模轉(zhuǎn)換器(DAC);10.5KB的閃存E2PROM;具有16位計(jì)數(shù)/定時(shí)器和32條可編程I/O接口的8051/8052微控制器,256字節(jié)的SRAM[2]。由于ADuC812的特殊功能寄存器組中添加了一個(gè)DPP(地址為84H),它與特殊功能寄存器DPH、DPL配合,使得ADuC812能夠訪問(wèn)16MB的外部數(shù)據(jù)地址空間。ADuC812的應(yīng)用開(kāi)發(fā)比較方便,它的內(nèi)核是國(guó)內(nèi)技術(shù)人員都很熟悉的Intel8051,用戶現(xiàn)有軟件都可以直接移植。

1.3 MAX 7000系列CPLD器件及MAX PLUSⅡ開(kāi)發(fā)平臺(tái)簡(jiǎn)介

本次設(shè)計(jì)選用ALTERA公司的MAX 7000系列器件。MAX 7000系列的高性能和高密度是基于它先進(jìn)的多重陣列矩陣架構(gòu)(Multiple Array Matrix),它采用E2CMOS工藝制作,傳播延遲最小為3.5ns,可以實(shí)現(xiàn)速度高于200MHz的計(jì)數(shù)器,并且為高密度的器件提供了非常寬的選擇余地,非常適合高速設(shè)計(jì)時(shí)應(yīng)用。該公司推出的MAX PLUSⅡ軟件是一款易于使用的開(kāi)發(fā)工具,其界面友好,集成化程度高,兼容工業(yè)標(biāo)準(zhǔn),支持FLEXMAXACEX1K等系列產(chǎn)品[3]。CPLD要實(shí)現(xiàn)的邏輯功能一般是在MAX PLUSⅡ環(huán)境下通過(guò)硬件描述語(yǔ)言(VHDL)開(kāi)發(fā)出來(lái)的,并能脫離硬件(CPLD)對(duì)設(shè)計(jì)方案進(jìn)行仿真,在確認(rèn)邏輯功能正確無(wú)誤的情況下,通過(guò)并行口下載“燒結(jié)”到CPLD器件中。“燒結(jié)”有不同設(shè)計(jì)人員“思想”的CPLD器件所實(shí)現(xiàn)的邏輯功能是千變?nèi)f化的,正因?yàn)槿绱耍瑢?duì)CPLD器件的開(kāi)發(fā)是相當(dāng)靈活的。

2 實(shí)現(xiàn)方案

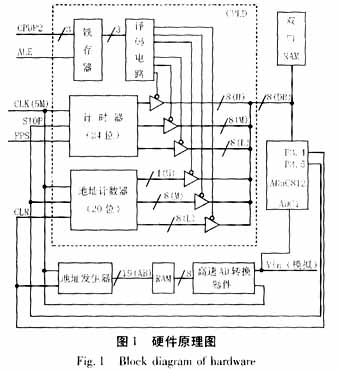

針對(duì)前面提到的問(wèn)題,本文提出一種利用CPLD器件巧妙解決此問(wèn)題的方法。高速AD轉(zhuǎn)換器件、地址發(fā)生器、地址計(jì)數(shù)器、計(jì)時(shí)器在時(shí)鐘源CLK(5MHz)的同步下以統(tǒng)一的步調(diào)工作。ADuC812初始化時(shí)P3.5置“0”,P3.4發(fā)出清零脈沖同時(shí)對(duì)地址發(fā)生器和地址計(jì)數(shù)器清零。在故障信號(hào)出現(xiàn)時(shí),ADuC812對(duì)P3.5置“1”,計(jì)時(shí)器和地址計(jì)數(shù)器同時(shí)停止計(jì)數(shù),暫態(tài)信號(hào)記錄完畢后,ADuC812分時(shí)讀出計(jì)時(shí)器中的值并將該數(shù)值保存在雙口RAM中,此值即為精度為0.2μs的時(shí)間信息,分時(shí)讀出地址計(jì)數(shù)器中的值并將該數(shù)值保存在雙口RAM中,此地址的精確時(shí)間即為計(jì)時(shí)器中的計(jì)數(shù)值。這樣就為高速數(shù)據(jù)采集系統(tǒng)中的采集數(shù)據(jù)貼上精確的時(shí)間標(biāo)簽。 本系統(tǒng)的硬件原理圖如圖1所示。

2.1 ADuC812的工作過(guò)程

ADuC812初始化時(shí)P3.5置“0”,同時(shí)P3.4發(fā)出清零脈沖使地址發(fā)生器和地址計(jì)數(shù)器同步計(jì)數(shù)。ADuC812控制內(nèi)部的ADC轉(zhuǎn)換模塊對(duì)經(jīng)過(guò)調(diào)整的取自電流互感器二次側(cè)的電流進(jìn)行AD轉(zhuǎn)換,采用半波比較,在每個(gè)工頻內(nèi)采集36個(gè)點(diǎn),分別用第n個(gè)點(diǎn)和第n+18個(gè)點(diǎn)、第n+1個(gè)點(diǎn)和第n+19個(gè)點(diǎn)比較,依此類推,如果大于事先設(shè)定的門檻值即認(rèn)為故障已經(jīng)發(fā)生。ADuC812使P3.5置“1”,計(jì)時(shí)器和地址計(jì)數(shù)器同時(shí)停止計(jì)數(shù),計(jì)時(shí)器中的數(shù)據(jù)即為地址計(jì)數(shù)器記錄的對(duì)應(yīng)于靜態(tài)RAM相同地址采集數(shù)據(jù)的時(shí)間標(biāo)簽,由于高速AD轉(zhuǎn)換器件的轉(zhuǎn)換頻率固定(本次設(shè)計(jì)為5MHz),所以,可以此為基準(zhǔn)為整個(gè)靜態(tài)RAM中的采集數(shù)據(jù)貼上時(shí)間標(biāo)簽。

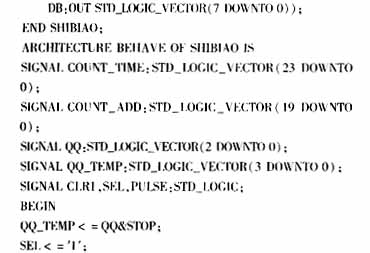

3.2 計(jì)時(shí)器和地址計(jì)數(shù)器的工作過(guò)程

當(dāng)STOP端口為低電平時(shí)(P3.5置“0”),計(jì)時(shí)器在5MHz的時(shí)鐘源下以相同的頻率計(jì)數(shù),由于它是一個(gè)24位的計(jì)數(shù)器,從而確保了計(jì)時(shí)器能夠記錄一個(gè)整秒,并為一個(gè)整秒刻上了![]() =0.2μs)的最小刻度。同時(shí)GPS發(fā)出的1PPS信號(hào)的上跳沿給計(jì)時(shí)器清零,從而為計(jì)時(shí)器提供精確的時(shí)間基準(zhǔn),以消除計(jì)時(shí)器的累計(jì)誤差。

=0.2μs)的最小刻度。同時(shí)GPS發(fā)出的1PPS信號(hào)的上跳沿給計(jì)時(shí)器清零,從而為計(jì)時(shí)器提供精確的時(shí)間基準(zhǔn),以消除計(jì)時(shí)器的累計(jì)誤差。

當(dāng)STOP端口為高電平時(shí)(P3.5置“1”),計(jì)時(shí)器停止計(jì)數(shù),在此狀態(tài)下GPS發(fā)出的1PPS信號(hào)的上跳沿不能對(duì)計(jì)時(shí)器清零。

地址計(jì)數(shù)器的工作過(guò)程與計(jì)時(shí)器的工作過(guò)程類似,唯一的區(qū)別是地址計(jì)數(shù)器的清零信號(hào)(CLR)是在初始化時(shí)由ADuC812的P3.4口發(fā)出的,由于地址發(fā)生器和地址計(jì)數(shù)器共用同一個(gè)清零信號(hào),從而確保地址發(fā)生器和地址計(jì)數(shù)器中的計(jì)數(shù)值完全相同。同理當(dāng)STOP端口為高電平時(shí),地址計(jì)數(shù)器也停止計(jì)數(shù),在此狀態(tài)下ADuC812發(fā)出的清零信號(hào)不能改變地址計(jì)數(shù)器中的計(jì)數(shù)值。

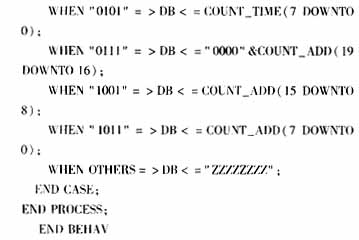

2.3 將地址計(jì)數(shù)器和計(jì)時(shí)器中的數(shù)據(jù)送至雙口RAM

由于ADuC812是一種8位單片機(jī),所以地址計(jì)數(shù)器和計(jì)時(shí)器中的數(shù)據(jù)只能“分批”地送至雙口RAM中保存。所以要設(shè)計(jì)鎖存器、譯碼電路和總線隔離電路,避免總線沖突以及保證總線上的數(shù)據(jù)能正確無(wú)誤地傳遞。在本次設(shè)計(jì)中,當(dāng)ADuC812的特殊功能寄存器DPP高3位的值為“00H”時(shí)將計(jì)時(shí)器的高8位數(shù)據(jù)通過(guò)ADuC812送至雙口RAM中,依此類推,當(dāng)特殊功能寄存器DPP高3位的值為“05H”時(shí)將地址計(jì)數(shù)器的低8位數(shù)據(jù)通過(guò)ADuC812送至雙口RAM中保存。當(dāng)特殊功能寄存器DPP為其他值時(shí)釋放數(shù)據(jù)總線,便于ADuC812進(jìn)行其他操作。

2.4 系統(tǒng)的VHDL描述及其仿真結(jié)果

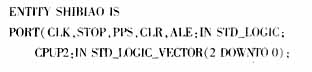

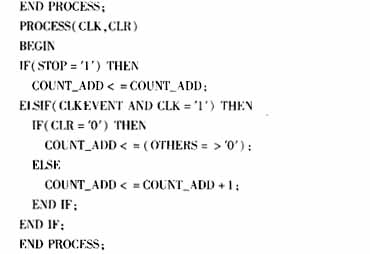

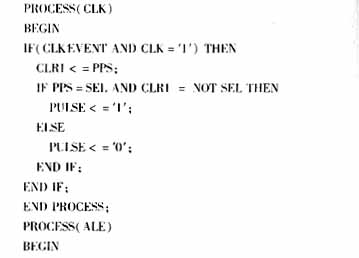

系統(tǒng)的上述功能可由硬件描述語(yǔ)言(VHDL)來(lái)實(shí)現(xiàn),源程序如下:

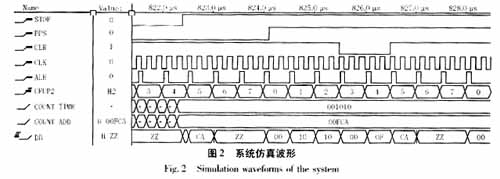

其仿真結(jié)果如圖2所示。

4 結(jié)論

本文對(duì)高速數(shù)據(jù)采集系統(tǒng)中的采集數(shù)據(jù)貼上精確時(shí)間標(biāo)簽的方法進(jìn)行了詳細(xì)地?cái)⑹龊头抡妫贸鋈缦陆Y(jié)論:

(a) 假設(shè)高速AD轉(zhuǎn)換器件的轉(zhuǎn)換頻率為5MHz,則本系統(tǒng)能為存入靜態(tài)RAM中的轉(zhuǎn)換數(shù)據(jù)貼上精度為0.2μs的時(shí)間標(biāo)簽。

(b) 通過(guò)復(fù)雜可編程邏輯器件(CPLD)間接地實(shí)現(xiàn)了“低速”的單片機(jī)系統(tǒng)對(duì)高速數(shù)據(jù)采集系統(tǒng)的實(shí)時(shí)監(jiān)視。