0 引言

PCI Express總線是新一代的I/O局部總線標準,是取代PCI總線的革命性總線架構(gòu)。PCI總線曾經(jīng)是PC體系結(jié)構(gòu)發(fā)展史上的一個里程碑,但是隨著技術(shù)的不斷發(fā)展,新涌現(xiàn)出的一些外部設(shè)備對傳輸速度和帶寬有更高的要求,PCI設(shè)計" title="設(shè)計">設(shè)計之初并沒有考慮這些因素,因此并不能完全滿足這些外部設(shè)備的需求。PCI Express總線正是在這種背景下應(yīng)運而生的。

一個PCI Express連接可以被配置成x1、x2、x4、x8、x12、x16和x32的數(shù)據(jù)帶寬。Xilinx公司的Virtex5系列FPGA芯片內(nèi)嵌PCI-Express" title="PCI-Express">PCI-Express-Endpoint Block硬核,為實現(xiàn)" title="實現(xiàn)">實現(xiàn)單片可配置PCI-Express總線解決方案提供了可能。

本文在研究PCI-Express接口" title="接口">接口協(xié)議和PCI-Express Endpoint Block硬核的基礎(chǔ)上,使用Virtex5LXT系列的XC5VLX50T FPGA芯片設(shè)計PCI- Express接口硬件電路,現(xiàn)YPCI-Express x4總線數(shù)據(jù)的傳輸。

1 PCI-Express總線概述

PCI-Express是一種高性能、通用的I/O互連技術(shù),可以廣泛應(yīng)用于計算和通訊的平臺。與傳統(tǒng)的PCI/PCI-X總線相比,PCI Express用高速串行接口替代了PCI-X的并行接口;用點到點的基于Switch的交換式通訊替代了PCI-X的基于總線的通訊;用基于包的傳輸協(xié)議(packetbasedprotocol)替代TPCI-X的基于總線的傳輸協(xié)議。此外,它還引入了一些新的特性:更強的電源管理、服務(wù)質(zhì)量控制(QoS),支持熱拔插,以及完善的錯誤處理和恢復(fù)。

1.1 PCI-Express設(shè)備/拓撲結(jié)構(gòu)

PCI-Express的典型拓撲結(jié)構(gòu)如圖1所示。PCI-Express協(xié)議中共定義了三種設(shè)備:RootComplex、Endpoint和Switeh。

Root Complex在系統(tǒng)中的位置類似于PCI-X中的主橋,它是I/O層次的根,它將CPU和MM連接至I/O部件。每個Root Complex可以有一個或多個PCI-Express Port(Root Port),每個接口定義一個層次域。Endpoint是PCI-Express的端點設(shè)備,可以分為PCI-Express Endpoint和LegacyEndpoint兩類。

Switch是PCI-Express的交換設(shè)備,可以理解為邏輯上由多個PCI-PCI橋組合而成,每個橋?qū)?yīng)于一個SwiSh端口。從配置軟件來看,Swi-tch是兩個或更多個邏輯的PCI-PCI橋。

1.2 PCI-Express的層次

PCI-Express協(xié)議中定義了三層結(jié)構(gòu):事務(wù)層(Transaction Layer)、數(shù)據(jù)鏈路層(Data Link Layer)和物理層(Physical Layer)。其結(jié)構(gòu)如圖2所示。

事務(wù)層主要負責(zé)組包和拆包,負責(zé)管理基于信用的流控制。

數(shù)據(jù)鏈路層主要負責(zé)鏈路的管理和數(shù)據(jù)完整性的管理,包括錯誤的檢測和錯誤的糾正。

物理層包含接口的所有電路:驅(qū)動器和輸入緩沖、并-串/串-并轉(zhuǎn)換、鎖相環(huán)、阻抗匹配電路,具有接口初始化和維護的功能。物理層可以更進一步細分為邏輯物理層(Logical Physical Layer)和電氣物理層(Electrical Physical Laycr)。邏輯物理層在發(fā)送方向上負責(zé)從數(shù)據(jù)鏈路層接收包,處理后發(fā)送上鏈路;在接收方向上負責(zé)將從鏈路收到的包經(jīng)過處理轉(zhuǎn)發(fā)到數(shù)據(jù)鏈路層。電氣物理層是連接到鏈路的模擬接口,包含每個通道的差分收發(fā)器。

1.3 PCI-Express的包

對應(yīng)于協(xié)議定義的三層結(jié)構(gòu),PCI Express定義了三種包:

(1)TLP:對應(yīng)于事務(wù)層,主要完成協(xié)議中定義的存儲器事務(wù)、I/O事務(wù)、配置事務(wù)和消息事務(wù)。

(2)DLLP:對應(yīng)于數(shù)據(jù)鏈路層,主要用于鏈路管理的功能,包括和TLP確認相關(guān)的ACK/NAK協(xié)議、電源管理和流控制信息的交換。在這一層提供了點到點的鏈路重傳機制和鏈路層的ECC校驗,從而提供了可靠的容錯機制。

(3)PLP:對應(yīng)于物理層,能夠支持物理層的鏈路訓(xùn)練,時鐘容忍/補償,自治的硬件電源管理。

2 Virtex-5" title="Virtex-5">Virtex-5 Lxt簡介

綜合考慮了實現(xiàn)PCI Express總線的周期、難易、成本等因素,最后本文采用了Xilinx公司65nm工藝的Virtex5 LXT系列芯片來實現(xiàn)PCI-Express的總線接口以及應(yīng)用。

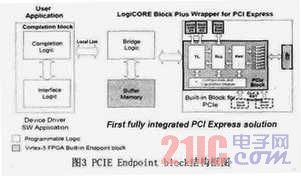

Virtex 5 Lxt PCIE Endpoint block具有PCI-Express的完整功能,完全符合PCIe基本規(guī)格v1.1版要求,作為FPGA內(nèi)部的硬核,它是可配置的PCIe端點解決方案,大大增加設(shè)計的靈活性,降低設(shè)計的RNE費用,并且支持1x、2x、4x或8x通道的實現(xiàn),為系統(tǒng)的功能擴張?zhí)峁┝擞行У耐緩健?br />

該系列芯片內(nèi)嵌PCIE Endpoint block集成了PCIE協(xié)議中的物理層(PHY)、數(shù)據(jù)鏈接層(DLL)和傳輸層(TL),同時它還實現(xiàn)了PCI-Express設(shè)備的功能配置寄存器,其結(jié)構(gòu)框圖如圖3所示,包含有以下幾個接口:時鐘和復(fù)位接口、配置和狀態(tài)接口、電源管理接口、用戶接口和傳輸層接口。該PCIE Endpoint block完成了PCI-SIG兼容性專題研討會的嚴格測試步驟,保證了產(chǎn)品的兼容性,降低了風(fēng)險;集成了Rocket IO-TMGTP收發(fā)器,該GTP收發(fā)器能提供100Mb/s到3.2Gb/s的串行連接性能,可以支持PCI-Express協(xié)議所需的2.5Gb/s的速率,與PCI-Expre-ss協(xié)議每通道2.5Gb/s工作模式兼容,這使得它在數(shù)據(jù)的編解碼上滿足PCI-Express協(xié)議的要求。本文使用該系列中的XC5VLX50T芯片設(shè)計PCI-Express接口硬件電路,實現(xiàn)PCI-Express x4的數(shù)據(jù)傳輸。

3 PCI-Express總線接口設(shè)計

本文的硬件主要就是單片XC5VLX50T實現(xiàn)PCI-Express總線接口,并在該FPGA內(nèi)設(shè)計具體應(yīng)用,完成PCI-Express總線接口的測試和使用。本文實現(xiàn)的應(yīng)用有如下幾個特性:

(1)主機通過控制FPGA內(nèi)部的寄存器文件來啟動和停止DMA操作,支持endpoint到root的全雙工DMA讀寫。

(2)使用LogiCORE產(chǎn)生的Endpoint Block Plus進行PCI-Express總線接口設(shè)計。該硬核集成了PCIE協(xié)議中的物理層、數(shù)據(jù)鏈接層的解析,提供傳輸層接口(TRN)供設(shè)計者對相應(yīng)的事務(wù)層數(shù)據(jù)包的處理。

(3)PCI-Express總線接口支持x4通道的實現(xiàn),主機操作系統(tǒng)為嵌入式Linux 2.6.10系統(tǒng)。在Windows XP下也進行PCI-Express接口測試。

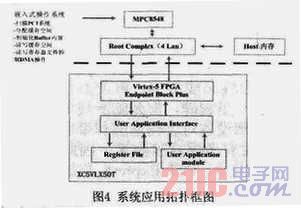

FPGA是整個設(shè)計的最關(guān)鍵部分,主要實現(xiàn):PCI-Express硬核;在硬核的用戶接口和傳輸接口實現(xiàn)PCI-Express傳輸本地總線的時序邏輯;并且在其內(nèi)部完成DMA控制時序邏輯。FPGA是PCI-Express總線接口和應(yīng)用模塊數(shù)據(jù)傳輸?shù)耐ǖ馈T贖ost端使用嵌入式的MPC8548作為主機系統(tǒng)應(yīng)用CPU,設(shè)計相應(yīng)的驅(qū)動和應(yīng)用程序配合FPGA內(nèi)部代碼的調(diào)試。圖4為該系統(tǒng)的拓撲框圖。

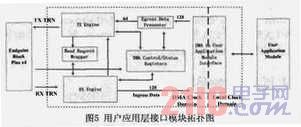

使用LogiCORE產(chǎn)生的Endpoint Block Plus中,定義了兩個基地址memory空間,一個用于DMA寄存器的操作,一個用于用戶邏輯空間。本文主要介紹的就是用戶應(yīng)用層接口的實現(xiàn),該接口將通過TRN進行相應(yīng)的事務(wù)層數(shù)據(jù)包的處理。

用戶應(yīng)用層接口主要包括如下幾個模塊:a.TX Engine模塊;b.RX Engine模塊;c.Egress Data Presenter模塊;d.Read Request Wrapper模塊;e.DMA Control/Status Registers模塊。這幾個模塊之間的拓撲關(guān)系如圖5所示。

TX Engine:該模塊主要用于產(chǎn)生和發(fā)送事務(wù)層數(shù)據(jù)包:Posted事務(wù)包(存儲器、I/O、配置讀寫事務(wù))、non_Posted事務(wù)包(該總線事務(wù)包分兩步進行,首先是發(fā)送端向接收端提交總線讀寫請求,之后接收端再向發(fā)送端發(fā)送完成包)和completion(完成)包。該模塊通過發(fā)送posted memory寫,non_Posted memory讀,和接收completion包來完成DMA的讀寫請求。該模塊的啟動由DMA Control/Status Registers模塊控制。該模塊又包括若干子模塊:posted packet generator模塊、non posted packet generator模塊、completion packet generator模塊和transmit TRN state machine模塊,上述三個generator模塊均由transmit TRN狀態(tài)機模塊控制,該狀態(tài)機的控制信號來自Endpoint Block Plus核以及DMA Control/StatusRegisters模塊。

RX Engine:該模塊主要用于接收Endpoint BlockPlus模塊從RX TRN接口送出的事務(wù)層數(shù)據(jù)包,對不同的事務(wù)包進行解析,根據(jù)相應(yīng)的包做相應(yīng)的處理,該模塊能處理如下三種事務(wù)包:完成包、memory讀包和memory寫包。該模塊又包括如下子模塊:接收TRN狀態(tài)機模塊、接收TRN監(jiān)控模塊、接收數(shù)據(jù)狀態(tài)機模塊以及兩個fifo用于存放完成包的接收數(shù)據(jù)和完成包中目的和源的地址以及數(shù)據(jù)包的長度,用于設(shè)置DMA Control/Status Registers模塊中的各個狀態(tài)。接收TRN狀態(tài)機模塊只負責(zé)TRN接口處的數(shù)據(jù)包的狀態(tài)和接收收據(jù),送給后面的模塊;接收TRN監(jiān)控模塊負責(zé)根據(jù)不同的TLP包來分配數(shù)據(jù)和狀態(tài),是直接將帶數(shù)據(jù)的完成包的數(shù)據(jù)寫到用戶應(yīng)用接口fifo,還是讀請求或?qū)懻埱骉LP包通知TX engine,組成相應(yīng)的包發(fā)送出去或者通知DMA控制器進行相應(yīng)的DMA傳送控制;接收數(shù)據(jù)狀態(tài)機模塊對接收到的數(shù)據(jù)進行相應(yīng)的處理。

Egress Data Presenter:該模塊是專門為TX Engine模塊提供發(fā)送數(shù)據(jù)的模塊,要發(fā)送到主機的數(shù)據(jù)都在該模塊中進行處理,它和TX Engine模塊間的數(shù)據(jù)位寬定義為64bit。

Read Request Wrapper:該模塊主要用于TX Engine模塊和RX Engine模塊之間的通信控制接口,本文中設(shè)計DMA的讀寫操作每包可能的數(shù)據(jù)長度為:1KDW、2KDW、3KDW、4KDW、8 KDW、16 KDW之間可選。該選擇是由主機通過寫寄存器文件來進行長度策略選擇的。

DMA Control/Status Register:該模塊主要用于主機系統(tǒng)通過控制FPGA內(nèi)部的寄存器文件的設(shè)置來啟動和停止endpoint到root的DMA讀寫操作。包括一個控制寄存器以及若干個配置寄存器,配置寄存器有主機的目的地址、源地址信息,本地的目的地址、源地址信息,以及每次DMA的數(shù)據(jù)包長度等信息。由控制寄存器中的bit位的狀態(tài)來啟動所有的狀態(tài)機的控制,所以控制寄存器是整個操作的關(guān)鍵信號。

4 實驗結(jié)果分析

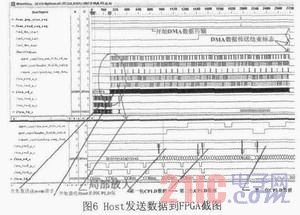

首先初始化FPGA內(nèi)部的寄存器文件,通過設(shè)置相應(yīng)的控制位啟動數(shù)據(jù)從Host內(nèi)存通過PCI-Express接口向下傳輸?shù)紽PGA內(nèi)部,傳輸完畢后,F(xiàn)PGA內(nèi)部控制邏輯將接收的數(shù)據(jù)進行處理,并得到向上輸出的數(shù)據(jù),然后通過PCI-Express接口,再將數(shù)據(jù)傳輸回Host內(nèi)存,Host內(nèi)存的檢測程序?qū)λ盏降臄?shù)據(jù)進行校驗。在進行FPGA內(nèi)部PCI-Express接口速度測試時,由于Host讀寫內(nèi)存需要一定的時間,所以在測試速度時不進行Host內(nèi)存的讀寫。而在正確性測試時,則通過Host讀寫內(nèi)存判斷數(shù)據(jù)是否正確。所有ChipScope截圖均以一包數(shù)據(jù)包大小為4KDW為例進行捕捉,圖中有文字標識其中的信號意義。

圖6為Host將數(shù)據(jù)通過PCI-Express接口向下傳輸?shù)紽PGA內(nèi)部的ChilpScope截圖。

從圖中可以看出,F(xiàn)PGA接收數(shù)據(jù)包的最大載荷為512B,而發(fā)送數(shù)據(jù)包為128B。在Host將數(shù)據(jù)通過PCI-Express接口向下傳輸?shù)紽PGA過程中,首先FPGA要向Host發(fā)送一系列mem讀請求包,Host收到請求包后,就根據(jù)請求包的內(nèi)存地址和數(shù)據(jù)長度發(fā)送CPLD包給FPGA,F(xiàn)PGA解析CPLD包并存儲數(shù)據(jù)到相應(yīng)數(shù)據(jù)區(qū)。圖7為在Windows XP下測得的每包數(shù)據(jù)包大小為16KDW時傳輸速率為5.03Gb/s。

圖8為FPGA處理完后將數(shù)據(jù)通過PCI-Express接口向上傳輸?shù)紿ost的ChipScope截圖。從圖中可以看出包和包之間的發(fā)送有一定的間隔,這是因為控制每包發(fā)送造成的間隔,所以在同樣每包數(shù)據(jù)包大小為16KDW時測得的傳輸速率要底于Host向下傳輸?shù)乃俾剩挥?.7Gb/s左右。

5 總結(jié)和展望

Virtex5系列FPGA芯片內(nèi)嵌PCI-Express End-pointBlock硬核,為實現(xiàn)單片可配置PCI-Express總線解決方案提供了可能。基于Virtex5 FPGA的PCI-Express設(shè)計實現(xiàn)方式簡單、配置靈活,適合于各種應(yīng)用領(lǐng)域,降低了設(shè)計成本,縮短了產(chǎn)品上市時間,保證了產(chǎn)品的功能性和易用性,開創(chuàng)了高效率PCI Express開發(fā)的新時代。