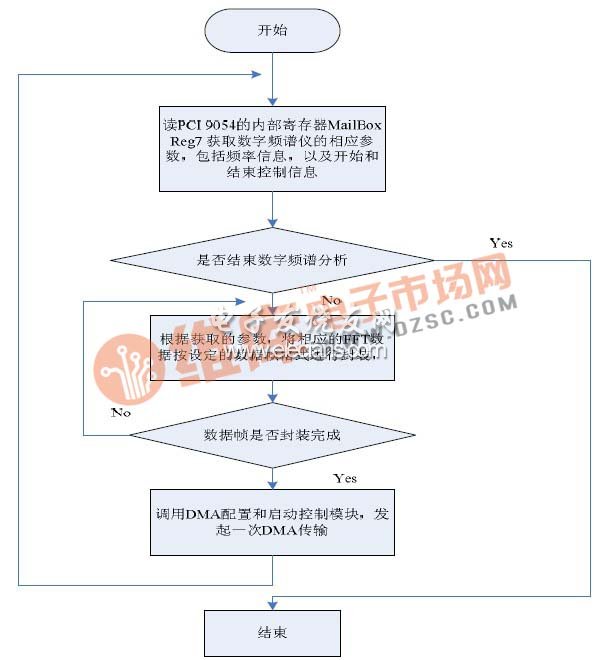

使用PCI9054 提供的DMA 傳輸方式,并由其Local 端配置和啟動DMA 傳輸來完成數(shù)字頻譜數(shù)據(jù)的傳輸,達到用PXI 總線實現(xiàn)數(shù)字頻譜分析儀與工控機的高速數(shù)據(jù)傳輸的目的。

隨著無線通信業(yè)務(wù)的飛速發(fā)展,頻譜資源顯得越來越缺乏,而實際中像廣播電視等頻段的頻譜利用率卻并不高,提高頻譜的利用率成為一種共識。認知無線電是一種按伺機方式充分利用頻譜的共享頻譜技術(shù),因此可以用來提高頻譜利用率。快速準確的數(shù)字頻譜分析對認知無線電的頻譜感知有非常重要的影響。在認知無線電系統(tǒng)中,數(shù)字頻譜分析儀與下一級的處理模塊的數(shù)據(jù)傳輸速率是制約認知無線電系統(tǒng)處理速度的一個瓶頸,因此需要選擇一種高速穩(wěn)定的數(shù)據(jù)傳輸接口技術(shù)。

本文利用 PXI 總線技術(shù)來實現(xiàn)數(shù)字頻譜分析儀與下一級處理模塊的數(shù)據(jù)傳輸接口。PXI是CompactPCI extend for Instrumentation 的簡稱,即面向儀器系統(tǒng)的PCI 擴展,由NI(美國國家儀器公司) 于1997 年10 月率先推出。它將CompactPCI 規(guī)范定義的PCI 總線技術(shù)發(fā)展為適合于工業(yè)控制、測量、數(shù)據(jù)采集和試驗應用的電氣、機械和軟件規(guī)范,從而形成了新的虛擬儀器體系結(jié)構(gòu)。PXI 總線是一種高性能的32 /64 位地址數(shù)據(jù)復用總線,支持突發(fā)傳輸,是一種堅固的基于PC 的測量和自動化平臺, 它的數(shù)據(jù)傳輸速率的峰值于33 MHz、32 bit 的總線上可達132 MB/s; 于66 MHz、64 bit 的總線上則可高達528 MB/s,遠高于GPIB (General-Purpose Interface Bus,通用接口總線)與VXI (VME bus eXtension for Instrumentation,面向儀器系統(tǒng)的VME 總線的擴展)接口的傳輸速率。基于PCI 總線發(fā)展而來的PXI 系統(tǒng)具有較好兼容性、存取延時小、成本低等優(yōu)點。PXI 總線數(shù)據(jù)傳輸接口以其高傳輸速率和穩(wěn)定可靠的傳輸性能得到了越來越廣泛的應用。

PXI 總線協(xié)議比較復雜, 工程應用中一般采用兩種方式, 一是采用FPGA(FieldProgrammable Gata Array,現(xiàn)場可編程門陣列)來設(shè)計控制接口, 缺點是控制接口難度較大、開發(fā)周期長、成本大; 二是采用接口芯片, 將復雜的PXI 總線接口轉(zhuǎn)換為相對簡單的用戶接口, 用戶只要設(shè)計轉(zhuǎn)換后的總線接口。本文采用PXI 總線專用接口芯片PCI9054 來實現(xiàn)PXI總線的數(shù)據(jù)傳輸。

PCI9054 是PLX 公司提供的一款PCI 專用接口芯片,它兼容PCI V2.2 的協(xié)議規(guī)范。其內(nèi)部結(jié)構(gòu)圖如圖1 所示。由圖可知,PCI9054 實現(xiàn)的是PCI Bus 端和Local Bus端的信號轉(zhuǎn)換,使得Local Bus 端不需要進行復雜的PCI 協(xié)議邏輯的設(shè)計,只需要進行簡單的數(shù)據(jù)傳輸邏輯的設(shè)計就能實現(xiàn)符合PCI 協(xié)議規(guī)范的信號生成。

傳輸方式、PCI Target 傳輸方式以及PCI DMA 傳輸方式。PCI Initiator 傳輸方式下,PCI9054 成為PCI Bus 端的主機,同時是Local Bus 端的從機,由Local Bus 端主動發(fā)起數(shù)據(jù)傳輸,PCI9054 被動后再主動向PCI Bus 發(fā)起傳輸。PCI Target 傳輸方式下PCI9054 的角色剛好與PCI Initiator 方式相反,成為PCI Bus端的從機以及Local Bus端的主機。而在PCI DMA方式下PCI9054同時是PCI Bus端和Local Bus 端的主機。在PCI9054 內(nèi)部分別提供了這三種傳輸方式下的內(nèi)部寄存器,方便設(shè)計者來對每一種傳輸方式進行配置。

PCI9054 的本地端支持可編程的特點,通過兩個模式選擇管腳MODE[1:0]來設(shè)置LocalBus 端分別工作在C 模式、J 模式、M 模式。這樣可以使得PCI9054 的Local Bus 可以掛載不同類型的其他設(shè)備。

PCI9054 提供了兩個獨立的可編程DMA (Direct Memory Access,直接存儲器存取) 控制器;每個通道均支持塊和分散/集中的DMA 方式;在PCI 總線端支持32 位的數(shù)據(jù)位寬,時鐘速率達到33MHz;本地端可以編程實現(xiàn)8、16 或32 位的數(shù)據(jù)寬度;傳輸速率最高可達132MB/s;本地總線端時鐘最高可達50MHz 支持復用/非復用的32 位地址數(shù)據(jù)。

2 接口電路設(shè)計

PXI 總線接口電路的設(shè)計主要是對PCI9054 芯片的外圍電路進行設(shè)計,主要包括四個部分:電源方案的設(shè)計、時鐘方案的設(shè)計、EEPROM 電路的設(shè)計,Local 端的連線方案設(shè)計。

PCI9054 芯片的正常工作電壓是3.3V,而在上位機的PXI 接口中,提供了三種電壓,3.3V、5V 和12V,因此PCI9054 的供電完全可以由上位機來提供。設(shè)計中,可以增加一個外部電壓的接入接口,方便開發(fā)過程中的調(diào)試。

PCI9054 芯片需要兩個工作時鐘,一個是PCI Bus 端的工作時鐘,一個是Local Bus 端的工作時鐘,這兩個工作時鐘是獨立的,均需要外部邏輯輸入。PCI Bus 端的工作時鐘由上位機的PXI 接口提供,主要在PCB(Printed Circuit Board, 印刷電路板);布線的時候需要對該時鐘線進行蛇形走線處理。Local Bus 端的工作時鐘由晶振提供,本方案中采用50MHz 的晶振。

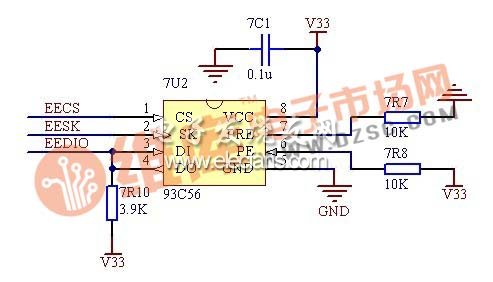

EEPROM 電路的設(shè)計中需要注意EEDI 和EEDO 兩個管腳的連接,電路原理圖如圖2所示。注意在沒有掛載Local 端的設(shè)備同時又沒有EEPROM 時,EEDI 和EEDO 需要通過一個1KΩ的電阻拉低。設(shè)計中,往往需要加上一個EEPROM 用來存儲對PCI9054 芯片的內(nèi)部寄存器的設(shè)置。這些設(shè)置在每次上電時自動進行加載,對PCI9054 芯片的內(nèi)部寄存器進行配置,使得每次上電后,PCI9054 能按事先所配置的方式工作。因此,在設(shè)計電路完成之后還需要對EEPROM 的內(nèi)容進行設(shè)置,并通過PlxMon 工具寫入。

圖 2 EEPROM 電路設(shè)計原理圖

在 Local 端的連線方案設(shè)計中,需要注意兩點:一是本地時鐘的接入,本地時鐘作為PCI9054 識別Local 端是否有設(shè)備的依據(jù),若在EEPROM 的EEDI 和EEDO 沒有下拉的情況下,一定要接入本地時鐘,不然連接上位機后,上位機進入不了系統(tǒng)。二是若需要用到PCI Initiator 傳輸方式,則必須將LBE[3:0]#全部拉低,否則就會造成讀寫出現(xiàn)上位機死機現(xiàn)象。

3 接口程序設(shè)計

由于數(shù)據(jù)傳輸接口涉及到數(shù)字頻譜儀和上位機,其程序設(shè)計也包括兩個部分:一部分是數(shù)字頻譜儀端的程序設(shè)計,即PCI9054 Local 端的程序設(shè)計,由于本項目中在PCI9054 的Local端掛載的是FPGA 芯片,需要在FPGA 中進行Local 端的接口邏輯程序設(shè)計;另一部分是上位機端的程序設(shè)計,主要是基于操作系統(tǒng)的驅(qū)動程序以及上層應用程序設(shè)計。

3.1 FPGA 程序設(shè)計

FPGA 程序的設(shè)計主要是對PCI9054 的Local 端時序邏輯進行設(shè)計。由圖2 可知,在PCI9054 內(nèi)部的Local 端存在三種傳輸方式狀態(tài)機:PCI Initiator 方式、PCI Target 方式、PCIDMA 方式。因此,在對Local 端的控制進行設(shè)計時,可以用不同的狀態(tài)機來匹配PCI9054的內(nèi)部狀態(tài)機,達到實現(xiàn)各種方式的數(shù)據(jù)傳輸。

本文根據(jù)系統(tǒng)的特點,選擇使用PCI DMA的傳輸方式。在FPGA端的程序采用層次化和模塊化的設(shè)計,分為上下兩層結(jié)構(gòu):下層是鏈路層,實現(xiàn)PCI DMA 方式下,長字(4Bytes)數(shù)據(jù)流的雙向傳輸鏈路的建立;上層是鏈路適配層,實現(xiàn)數(shù)字頻譜儀的數(shù)據(jù)按照一定的幀格式封轉(zhuǎn)成幀。PCI DMA 方式的設(shè)置和啟動也在FPGA 中完成,程序采用模塊化的設(shè)計方式,將數(shù)據(jù)傳輸模塊與控制模塊區(qū)分。在控制模塊中,分成三層:第一層是寄存器讀寫層,實現(xiàn)對PCI9054 內(nèi)部寄存器的讀寫操作;第二層是參數(shù)獲取與PCI DMA 方式配置層,實現(xiàn)從PCI9054 內(nèi)部消息寄存器獲取數(shù)字頻譜儀的控制參數(shù)以及對PCI DMA 方式進行配置與啟動控制;第三層是上層控制層,用來解析控制參數(shù)以及控制生成數(shù)據(jù)幀。整個程序結(jié)構(gòu)圖如圖3 所示。

圖3 FPGA程序結(jié)構(gòu)圖

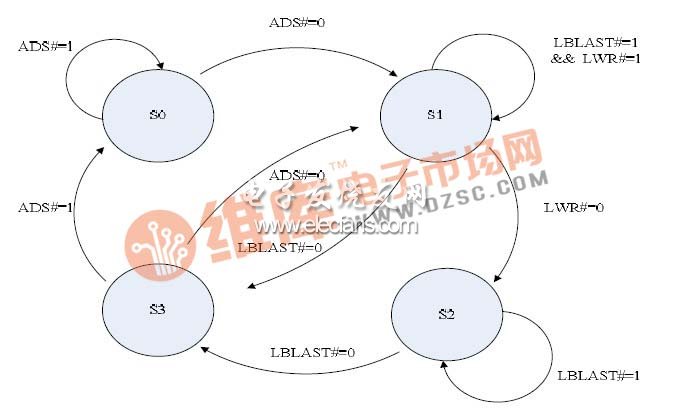

上述 FPGA 程序中主要包括了兩個狀態(tài)機的設(shè)計,一個PCI DMA 數(shù)據(jù)傳輸方式的狀態(tài)機設(shè)計,一個是PCI 9054 內(nèi)部寄存器讀寫操作的狀態(tài)機設(shè)計。它們的狀態(tài)轉(zhuǎn)移圖分別如圖4和圖5 所示。

圖4 PCI DMA 數(shù)據(jù)傳輸狀態(tài)轉(zhuǎn)移圖

圖 4 中,S0 為空閑狀態(tài);S1 若在PCI9054 對Local Bus 進行寫的操作中為數(shù)據(jù)接收狀態(tài),若在PCI9054 讀Local Bus 的操作中為數(shù)據(jù)準備狀態(tài);S2 為PCI 9054 讀Local Bus 的操作中的數(shù)據(jù)發(fā)送狀態(tài);S3 為讀寫操作的終止狀態(tài)。圖中各狀態(tài)轉(zhuǎn)移觸發(fā)信號均為PCI 9054Local Bus 端的控制信號。

圖 5 PCI 9054 內(nèi)部寄存器讀寫操作的狀態(tài)轉(zhuǎn)移圖

圖 5 中,S0為空閑狀態(tài),在讀寫啟動信號en_rwreg=1的情況下進入工作狀態(tài);S1為讀寫周期開始狀態(tài),有效Local Bus 端的讀寫周期開始信號;S2 為讀寫周期等待狀態(tài),等待PCI9054 的LREADY#有效;S3 為突發(fā)讀寫方式下的響應狀態(tài),突發(fā)讀寫方式下,PCI9054的LREADY#有效后,使能內(nèi)部邏輯進行相應的響應;S4 為讀寫周期響應狀態(tài),在非突發(fā)讀寫方式下或者突發(fā)讀寫的終止周期中的響應狀態(tài)。

在實現(xiàn)了上述兩個狀態(tài)機模塊后,F(xiàn)PGA的程序還需要包括對FFT處理器的輸出數(shù)據(jù)進行數(shù)據(jù)幀封裝,即給每一次FFT 處理器根據(jù)相應的配置參數(shù)進行處理輸出的數(shù)據(jù)加上幀頭,幀頭中包含了此次傳輸?shù)腇FT 數(shù)據(jù)所覆蓋的頻段以及數(shù)據(jù)的長度信息。這樣做的好處是上位機不需要額外的同步信息,只需要根據(jù)幀頭中的頻段信息以及長度信息就可以判斷當前數(shù)據(jù)幀所表示的頻譜信息。利用PCI9054 內(nèi)部寄存器中的MailBox 寄存器組來實現(xiàn)數(shù)字頻譜儀與上位機之間的參數(shù)傳遞。由于數(shù)字頻譜儀需要的參數(shù)信息比較少,只需要頻段選擇信息,以及開始和結(jié)束數(shù)字頻譜儀的控制信號,選擇MailBox 寄存器組中的第七個位寬為32 位的寄存器來傳遞控制信息。

整個 FPGA 程序的流程示意圖如圖6 所示。

圖6 FPGA程序流程示意圖

3.2 接口驅(qū)動程序的設(shè)計

接口驅(qū)動程序的設(shè)計可以通過兩種方式實現(xiàn),一種是通過專用的驅(qū)動程序開發(fā)工具進行驅(qū)動程序的設(shè)計,如DDK、DriverStudio 和WinDriver 等,另外一種方式是通過PLX 公司提供的PCI軟件工具包SDK(Software Development Kit)實現(xiàn)接口的驅(qū)動設(shè)計,它提供了能夠?qū)崿F(xiàn)各種傳輸方式所需要的基本API 函數(shù)。

為了縮短開發(fā)周期,本文采用由PLX 公司提供的SDK 工具包進行驅(qū)動程序的開發(fā)。運用其SDK 提供的工作API 函數(shù)實現(xiàn)Block DMA 模式下的Burst Forever(無限突發(fā))方式的數(shù)據(jù)傳輸。主要用到的函數(shù)如表1 所示。

由于本系統(tǒng)的特殊應用,還需要增加一些上層的應用程序,才能實現(xiàn)整個數(shù)字頻譜儀數(shù)據(jù)的正常工作,主要包括數(shù)字頻譜儀的參數(shù)控制字的生成和寫PCI9054 內(nèi)部寄存器MailBoxReg7,以及對接收的數(shù)據(jù)幀進行解封裝的相關(guān)程序開發(fā)。

表1 Block DMA 模式下的SDK API 函數(shù)應用列表

本文使用了 PCI9054 的DMA傳輸方式,并且在Local端發(fā)起DMA傳輸,在上位機上采用中斷的形式進行響應,可以減少占用上位機CPU 處理時間,使得上位機在進行數(shù)據(jù)傳輸?shù)耐瑫r可以進行其他的操作。PXI 接口加上PCI9054 的開發(fā)模式,使得開發(fā)周期縮短了很多,避免了復雜的PXI 總線協(xié)議的邏輯設(shè)計和驗證工作。本系統(tǒng)采用的PXI 總線的傳輸位寬32 位,采用無限突發(fā)的傳輸方式,在數(shù)據(jù)傳輸周期中的數(shù)據(jù)傳輸速率為132MB/s,但是由于增加了額外的控制周期以及其他的一些控制邏輯,使得數(shù)據(jù)的平均傳輸速率并沒有達到這個值,但是完全可以匹配目前FFT 處理器的處理速率,可以保證數(shù)據(jù)傳輸?shù)膶崟r性。