0 引言

當前,人們對大數據量的高速存取需求越來越高。SD" title="SD">SD卡作為新一代數據存儲設備,具有大容量,高速度的特點,很好地滿足了市場的具體需求,被廣泛用于便攜式消費類電子設備,例如手機,數碼相機、PDA和各種多媒體播放器等。在工業(yè)控制領域,同樣有大量數據需要采集,存儲,分析。而傳統(tǒng)用MCU的GPIO模擬SD卡的時序實現讀/寫調試復雜、讀/寫速度慢,已經不能符合大多數應用的需求。利用FPGA自身高速并行的特點,開發(fā)一種SD卡讀寫" title="讀寫">讀寫控制器" title="控制器">控制器的IP核,不但可以提高性能,而且可以簡單實現IP復用,大大提高開發(fā)效率,降低成本,具有極大的應用前景。

可編程的片上系統(tǒng)(System on Programmable Chip,SoPC)最先由Altera公司提出,它將盡可能大而完整的電子系統(tǒng),主要包括NiosⅡ嵌入式處理器、各種硬件接口、數字信號處理系統(tǒng)、普通數字電路邏輯在單一FPGA芯片中實現。SoPC系統(tǒng)中的各個外設通過Avalon" title="Avalon">Avalon總線相連,可簡單實現IP復用,因此,系統(tǒng)在開發(fā)周期、體積、功耗、功能、產品升級維護等多方面實現最優(yōu)化,逐漸成為電子產品設計" title="設計">設計的趨勢。

1 Avalon總線簡介

Avalon總線是Altera公司專門為SoPC系統(tǒng)指定的一套總線標準,它定義了主從端口對之間通信的信號類型和時序關系。在結構上不同于傳統(tǒng)的共享式總線:它在需要連接的每一個主從端口對之間都有點到點的連接,不同的主從端口對之間可以同時進行通信,所以大大提高了系統(tǒng)的性能。Altera一直在致力于為Avalon總線添加一些極其有用高級特性,簡化系統(tǒng)設計的同時提高系統(tǒng)的性能。Avalon總線標準也在不斷的升級完善,現在已經包含Avalon-MM接口規(guī)范和Aval-on-ST接口規(guī)范。

在Avalon總線接口的設計中,SoPC Builder提供了直觀的圖形用戶界面,設計人員可以很方便地添加自定義外設,SoPC Builder將自定義外設和其他組件組合起來,生成對這些組件進行例化的單個系統(tǒng)模塊,并且自動生成內部總線邏輯,按照設計人員的要求將這些外設與NiosⅡ處理器連接起來,并自動完成外設和存儲器的地址映射、中斷控制和總線控制等工作。本文主要闡述了SD卡讀/寫控制器的AvaIon-MM總線接口和SD卡讀/寫控制邏輯的設計,以圾NiosⅡIDE中讀/寫控制程序的編寫。

2 SD卡的一般讀/寫過程

SD卡有兩種讀/寫訪問模式:SD模式和SPI模式,其中SD模式又分為1 b和4 b兩種。由于DE2開發(fā)平臺硬件上的原因,該設計采用的是1 b的SD模式實現SD卡的讀/寫。SD卡在上電初期,卡主控通過檢測引腳1(DAT3)的電平來決定使用SD模式還是SPI模式。

SD總線上命令和數據的傳輸從一個起始位開始,以停止位終止。每個時鐘周期傳輸一個命令或數據位。控制器通過CMD信號線發(fā)送命令到SD卡,用于對SD卡進行相應的操作,SD卡接收到命令后,會發(fā)送相對應的響應給控制器,這些響應中包含了SD卡的一些基本信息和狀態(tài)信息等。SD卡初始化完成后,進入數據傳輸階段,則可以進行讀/寫操作。為了避免命令,數據和響應傳輸的錯誤,SD規(guī)范中采用了CRC技術,在傳輸命令和響應時,需要進行CRC7效驗,而在傳輸數據時,則需要進行CRC16效驗。該控制器主要采用SD的CLK,CMD,DAT0三根信號線完成SD卡的讀/寫。

3 SD卡讀寫控制器總體工作過程

該控制器采用Verilog HDL語言編寫,在SD卡就緒后,NiosⅡ處理器先向Avalon-MM Slave端口設置相關寄存器。狀態(tài)控制邏輯根據寄存器中的相關位發(fā)送命令到讀/寫控制邏輯,再由讀/寫控制邏輯發(fā)送相應的命令到SD卡。命令在時鐘信號CLK的上升沿經過CRC7校驗后通過CMD信號線串行寫入SD卡。SD規(guī)范中定義了很多命令,但這里僅用到了常用的10個命令就實現了讀/寫控制的功能,命令都要按一定格式順序發(fā)送到SD卡,命令編號占6 b,每個命令必須填充開始標志,命令的參數以及CRC7校驗數據以及結束標志,發(fā)送1個完整的命令需要寫入48b。

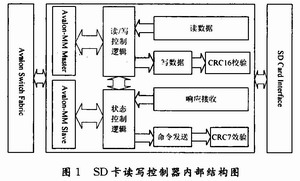

SD卡在接收到命令后,會根據寫入的命令執(zhí)行相應的操作,并發(fā)送相應的Response給控制器,其中Re-sponse也分為幾種,包含長響應和短響應,Response中的數據包含了卡的一些基本信息以及命令的執(zhí)行情況等。控制器根據返回的狀態(tài)的信息決定下一步操作,即發(fā)送下一個命令。控制器內部總體結構如圖1所示。

控制器上電后自動進行初始化,將SD卡的狀態(tài)保存到狀態(tài)寄存器中,在進行讀/寫前,應先讀取SD卡的狀態(tài)信息,在SD卡進入了讀/寫就緒狀態(tài)后,即可向Avalon-MM Slave端口寫入讀/寫控制命令,具體包括要讀/寫的扇區(qū)號,讀出數據或寫入數據的存放地址。控制器在收到開始讀/寫命令后,開始讀/寫指定的扇區(qū),控制器一次性讀/寫512 B,產生一個讀/寫完成的中斷,即可以開始讀/寫下一個扇區(qū)。進行讀操作時,控制器將從SD卡讀出的數據通過AvaIon-MM Master端口寫入所指定的地址處。進行寫操作時,控制器通過Avalon-MM Master端口將指定內存地址處的數據寫入SD卡。控制器整個讀/寫過程無需CPU干預,由Master端口主動完成,CPU僅需寫入相關控制命令,大大提高了CPU的利用率。

4 Avalon-MM接口設計

為了實現數據在Avalon總線上的傳輸,必須實現Avalon總線相關信號和時序邏輯,主要包括數據、地址、讀/寫控制、中斷、時鐘復位等信號。

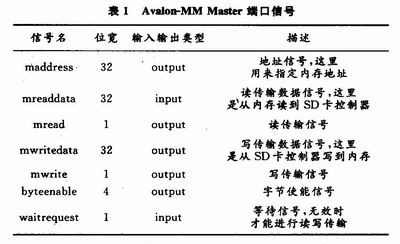

Avalon-MM Master端口主要用來將讀/寫控制邏輯部分讀到的數據寫入內存,或者將內存中的數據寫入讀/寫控制邏輯,其接口信號如表1所示。

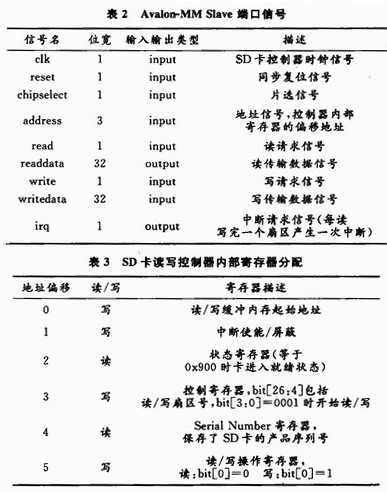

Avalon-MM SIave端口主要用來接收相關控制命令,即通過這個端口實現控制器內部寄存器的訪問,其接口信號如表2所示。

該控制器內部有6個寄存器,也可以根據需要實現更多,通過軟件設置相關寄存器即可進行讀/寫SD卡的操作,寄存器功能描述如表3所示。

5 系統(tǒng)硬件設計

為了驗證SD卡讀寫控制器,在DE2開發(fā)平臺上搭建了最基本的硬件系統(tǒng),主要包括:NiosⅡ處理器,PLL鎖相環(huán),片上RAM,JTAG UART和自定義的SD卡讀寫控制器。NiosⅡ作為系統(tǒng)主控制器,PLL用來產生SD卡讀/寫所需的時鐘信號,片上RAM用來存儲代碼和數據,JTAG UART主要用來調試,打印數據到控制臺驗證寫入的數據和讀出的數據是否相同。

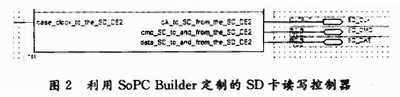

硬件系統(tǒng)的建立主要利用Altera公司QuartusⅡ開發(fā)工具以及其集成的SoPC Builder完成的,關鍵在于如何用SoPC Builder將SD卡讀寫控制器添加到元件列表中。在SoPC Builder提供的圖形化的界面下,添加控制器Verilog源程序后,設置控制器中各信號在Avalon-MM總線中的信號類型等,圖2即為添加好的SD卡讀寫控制器。

圖2中,各引腳的描述如下:

base_clock:控制器輸入時鐘,該設計采用PLL產生的25MHz時鐘信號;

clk_to_SD:SD卡時鐘信號輸入;

cmd_SD:SD卡命令,響應輸入/輸出信號;

data_SD:SD卡數據信號。

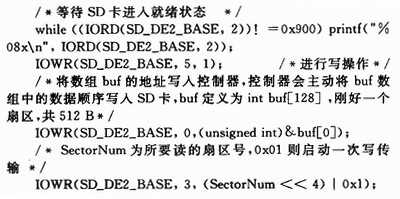

根據SD控制器的寄存器映射,在Nios IDE中編寫C程序控制SD卡控制器進行讀/寫操作,下面代碼為寫SD卡的一段程序,讀SD卡的的過程與其類似。

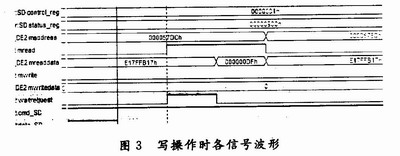

讀/寫完一個扇區(qū)后,控制器會產生一個中斷,此時即可進行下一次讀/寫操作。由于SD卡讀/寫有比較復雜的時序要求,命令、響應眾多,在設計的初期,采用Modelsim做了各方面的功能仿真,功能仿真完成后采用QuartusⅡ自帶的SignalTapⅡ邏輯分析儀來測試

分析內部邏輯的工作狀態(tài),SignalTapⅡ使用簡單方便,更重要的是可以實時觀測內部信號變化,而且可以設置觸發(fā)條件,大大提高了開發(fā)的效率。圖3是用SignalTapⅡ邏輯分析儀捕捉到的波形。

圖3中,status_reg為狀態(tài)寄存器,00000900表明卡已處于就緒狀態(tài),control_reg為控制寄存器,00000001H表明已經開始了一次對扇區(qū)0的寫傳輸,mread的上升沿即開始了Master端口的讀傳輸,這里的讀指的是將內存中buf數組中的數據讀入控制器,再由控制器寫入SD卡中,waitrequest為等待信號,高電平時無法進行數據傳輸,waitrequest無效后可以很明顯地看到000000DFH由Master端口讀入控制器,再由讀寫控制邏輯寫入SD卡。

6 結語

該設計采用SoPC技術實現了SD卡讀寫控制器,通過NiosⅡ處理器控制實現了SD卡讀/寫。由于該控制器根據Avalon接口規(guī)范進行開發(fā),可以很方便以IP核的形式集成到其他SoPC系統(tǒng)中,簡單實現SD卡的讀/寫,大大降低了開發(fā)成本和難度。本文所設計的SD卡讀寫控制器還有一大優(yōu)點就是具有Master端口,可以自主完成數據的讀/寫,無需CPU的干預,另外采用了中斷,降低了響應延時,提高了讀/寫速率。該設計滿足了大部分數據存儲需求,適用于工業(yè)監(jiān)測控制,一般消費類電子產品等。