EMCCD(Electron MuItiplying Charge Coupled Device)是新一代高質(zhì)量微光成像器件。與傳統(tǒng)CCD(Charge Coupled Device)相比,它采用了片上電子增益技術(shù),利用片上增益寄存器使圖像信息在電子轉(zhuǎn)移過程中得到放大,這使得它在很高的讀出速率下仍具有相對很低的讀出噪聲,能在微光源下高分辨力成像。

EMCCD的這些特性使其在航天微光目標(biāo)探測、微光生命科學(xué)成像、軍用高性能夜視探測等領(lǐng)域具有極大的應(yīng)用潛力。EMCCD驅(qū)動(dòng)電路是EM-CCD應(yīng)用的核心技術(shù),其性能直接影響到成像質(zhì)量。目前常用的時(shí)序產(chǎn)生方法有以下幾種:

(1)直接數(shù)字電路驅(qū)動(dòng)法。這種方法原理簡單,容易實(shí)現(xiàn)。但是邏輯設(shè)計(jì)較復(fù)雜,調(diào)試非常困難,而且在實(shí)際電路中因使用芯片較多,為整個(gè)系統(tǒng)帶來不可靠性。

(2)MCU驅(qū)動(dòng)法。該方法是通過編程MCU的I/O端口來獲得CCD驅(qū)動(dòng)脈沖信號(hào)的。這種方法的靈活性好,精度也可以很高,對不同的CCD器件只需要修改程序即可。由于CCD的驅(qū)動(dòng)頻率為MHz級(jí),使得選用MCU器件的工作頻率必須很高(提高了硬件成本),同時(shí)因頻繁的中斷和任務(wù)調(diào)度使MCU效率很低。

(3)EPROM驅(qū)動(dòng)法。這種驅(qū)動(dòng)電路一般由晶體震蕩器、計(jì)數(shù)電路和EPROM存儲(chǔ)器構(gòu)成。這種驅(qū)動(dòng)時(shí)序產(chǎn)生方法,結(jié)構(gòu)簡單、明確,調(diào)試容易,缺點(diǎn)是結(jié)構(gòu)尺寸太大,對于實(shí)現(xiàn)復(fù)雜的驅(qū)動(dòng)時(shí)序有較大困難。

(4)專用IC驅(qū)動(dòng)方法。這種方法就是利用CCD專用IC來產(chǎn)生時(shí)序,集成度高,功能強(qiáng),使用方便。對攝像機(jī)等視頻領(lǐng)域應(yīng)用的CCD或三元彩色CCD,這種驅(qū)動(dòng)方法是首選。一般由相應(yīng)的CCD廠家提供。

另一種更有效的方法就是使用CPLD,F(xiàn)PGA等大規(guī)模可編程邏輯器件實(shí)現(xiàn)。通過對該邏輯器件的編程,能實(shí)現(xiàn)任意復(fù)雜的時(shí)序邏輯,且調(diào)試方便,只使用一片集成電路以及少數(shù)外圍器件,故可靠性高。本文即采用這種方法,實(shí)現(xiàn)了CCD97所需的12路驅(qū)動(dòng)時(shí)序。

1 CCD97簡介

CCD97是E2V公司的背照式低照度CCD圖像傳感器,有效像素512X512,像素大小16μm×16 μm,它是幀轉(zhuǎn)移型CCD,芯片采用反向輸出模式抑制暗電流,其靈敏度高,噪聲控制方面精益求精,由于采用新的輸出放大電路,使它能在11 MHz的像素讀出速率下,以低于1電子/像素的超低噪聲工作,其量子效率高達(dá)92.5%。它獲取圖像速度快,具有正常CCD和EMCCD雙讀出模式。在微光成像系統(tǒng)中更具有優(yōu)越性,能實(shí)現(xiàn)真正意義上的24 h實(shí)時(shí)監(jiān)控。

2 驅(qū)動(dòng)電路的設(shè)計(jì)

2.1 CCD97驅(qū)動(dòng)電路的要求

成像區(qū)向存儲(chǔ)區(qū)的轉(zhuǎn)移波形如圖1所示。

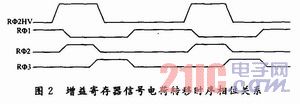

信號(hào)電荷在增益寄存器中的轉(zhuǎn)移波形如圖2所示。圖2為信號(hào)電荷在增益寄存器中的轉(zhuǎn)移波形,轉(zhuǎn)移脈沖Rφ2HV的高電平必須先于Rφ1和Rφ2到達(dá),同時(shí)Rφ1和Rφ2需要交替變化。

幀轉(zhuǎn)移時(shí)序如下:

Iφ與Sφ為幀轉(zhuǎn)移脈沖,Rφ1,2,3為行轉(zhuǎn)移脈沖。Iφ與Sφ的典型工作頻率為1 MHz,Rφ的工作頻率為11 MHz。

在Iφ1,2和Iφ3,4反向時(shí)序下,將成像區(qū)圖像信號(hào)逐行轉(zhuǎn)移至存儲(chǔ)區(qū)。需要轉(zhuǎn)移的行數(shù)為512+8+8=528。

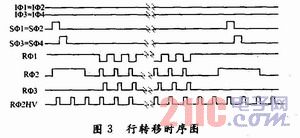

行轉(zhuǎn)移時(shí)序圖:

與幀轉(zhuǎn)移結(jié)束,在轉(zhuǎn)移時(shí)序Rφ1,2,3以及RφHV的時(shí)序作用下,存儲(chǔ)區(qū)的圖像以行為單位進(jìn)行轉(zhuǎn)移,逐像素通過移位寄存器組,然后從讀出放大器讀出(EMCCD讀出模式),其操作時(shí)序如圖3所示。

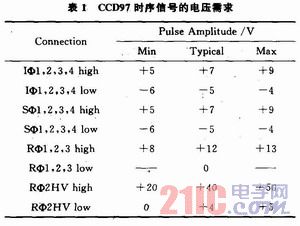

CCD97所需的電壓和波形如表1所示。

由CPLD,F(xiàn)PGA等可編程器件發(fā)生的時(shí)序邏輯冒充為TTL型,要想它能驅(qū)動(dòng)CCD97工作,必須按照表1進(jìn)行電平轉(zhuǎn)換。

2.2 驅(qū)動(dòng)電路的設(shè)計(jì)

該系統(tǒng)選用的FPGA芯片為Altera公司Cyclone系列的FPGAEP1C3T100,其有100個(gè)管腳封裝,I/O的電源為3.3 V,內(nèi)核電壓為1.5 V,有1個(gè)鎖相環(huán)(PLL),2個(gè)專用全局時(shí)鐘輸入管腳CLK0、CLK1,5個(gè)雙重用途時(shí)鐘管腳DPCLK。EP1C3T100是SRAM型的可編程邏輯器件,本身并不能固化程序,因此需要通過一片F(xiàn)LASH結(jié)構(gòu)的配置芯片來存儲(chǔ)邏輯配置信息。從Altera公司提供的數(shù)據(jù)手冊,可知Cyclone系列的FPGA僅支持EPCS1,EPCS4以及EPCS16。而選用的EP1C3T100中,其原始二進(jìn)制文件大小為627 376 b,使用EPCS1(1 048 576 b)的配置芯片。使用EPCS配置芯片在主動(dòng)串行模式(AS)下(MSEL[0..1]置地),即可實(shí)現(xiàn)上電后,將存儲(chǔ)器件中的數(shù)據(jù)傳送到EP1C3T100中。系統(tǒng)通過ARM加載驅(qū)動(dòng)程序?qū)崿F(xiàn)對FPGA的配置,驅(qū)動(dòng)FPGA產(chǎn)生CCD的工作時(shí)序。本系統(tǒng)選用Atmel公司的AT91RM9200的處理器。它是基于ARM920T內(nèi)核,主頻為180 MHz,運(yùn)行性能可達(dá)200 MIPS,擁有獨(dú)立的16 KB指令和數(shù)據(jù)Cache,并配備有16 KB的SRAM以及128 KB的ROM。

EP1C3T100芯片內(nèi)含1個(gè)PLL,外接40 MHz有源晶振為PLL提供時(shí)鐘。時(shí)鐘模塊通過QliartusⅡ的megafunctions下的altpll配置生成。采用非補(bǔ)償模式,輸入/輸出時(shí)鐘比為5:1,輸出的2路時(shí)鐘c0,c1均為200 MHz。其中c0為clk_gen模塊提供基礎(chǔ)時(shí)鐘。同時(shí)c1產(chǎn)生相位需要調(diào)整的Rφ2HV,用以滿足CCD97增益寄存器轉(zhuǎn)移過程中的嚴(yán)格時(shí)序要求。

在FPGA時(shí)序發(fā)生設(shè)計(jì)中,依照CCD97工作的流程,進(jìn)行逆序設(shè)計(jì)。從最高頻率的像素移位讀出時(shí)鐘到行轉(zhuǎn)移時(shí)鐘最后到幀轉(zhuǎn)移這樣的流程進(jìn)行設(shè)計(jì)。框圖如圖4所示。

2.2.1 Iφ,Sφ,Rφ驅(qū)動(dòng)設(shè)計(jì)

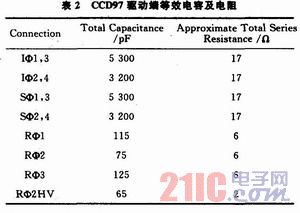

在設(shè)計(jì)Iφ,Sφ以及Rφ驅(qū)動(dòng)電路時(shí),統(tǒng)一采用Elantec半導(dǎo)體公司的EL7457。它是高速四通道CMOS驅(qū)動(dòng)器,能工作在40MHz,并提供2 A的峰值驅(qū)動(dòng)能力,以及超低的等效阻抗(3 Ω),它具有3態(tài)輸出,并通過OE控制,這對于CCD的驅(qū)動(dòng)來說,容易實(shí)現(xiàn)靈活的電源管理。為了簡化設(shè)計(jì),固定Rφ2HV的電壓幅值為典型值。在組成Iφ和Sφ的驅(qū)動(dòng)電路時(shí)必須考慮CCD97驅(qū)動(dòng)端的等效電容和電阻,如表2所示。

電路的時(shí)間常數(shù):

![]()

又因?yàn)樯仙龝r(shí)間與時(shí)間常數(shù)的關(guān)系為:

![]()

為了滿足最佳上升時(shí)間(200 ns)的要求,必須在EL7457驅(qū)動(dòng)輸出端串上一個(gè)小電阻,原理如圖6所示。

圖6中,F(xiàn)PGA_CLKI1,F(xiàn)PGA_CLKI2,F(xiàn)PGA_CLKI3,F(xiàn)PGA_CLKI4為FPGA產(chǎn)生的TTL時(shí)序。ARM_IOE為ARM核產(chǎn)生的門控信號(hào),用來控制驅(qū)動(dòng)脈沖Iφ1,2,3,4的開關(guān)。由于理論與實(shí)際計(jì)算的誤差,輸出串接電阻R9,R10,R13,R14將通過硬件調(diào)試過程確定,以產(chǎn)生驅(qū)動(dòng)CC97工作的最佳波形。同理,F(xiàn)PGA_CLKS1,F(xiàn)PGA_CLKS2,F(xiàn)PGA_CLKS3,F(xiàn)PGA_CLKS4為FPGA產(chǎn)生的TTL時(shí)序。ARM_SOE為ARM產(chǎn)生的門控信號(hào),輸出串接電阻待定。

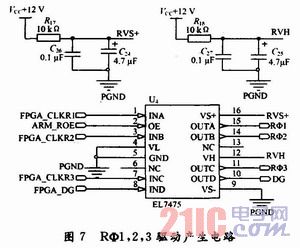

在Rφ1,2,3產(chǎn)生電路中,因?yàn)槠潆妷簲[幅要求為0~12 V,故給它加以12 V的電源(見圖7)。

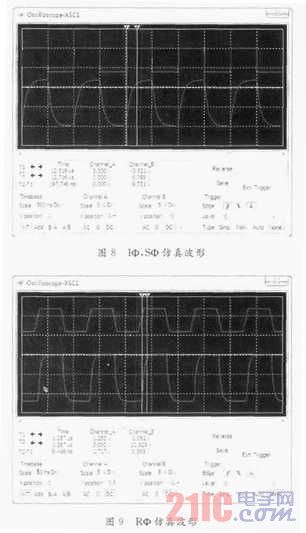

它的驅(qū)動(dòng)頻率為11 MHz,輸出的上升時(shí)間不需要串接電阻調(diào)節(jié),可達(dá)10 ns。同理,F(xiàn)PGA_CLKR1,F(xiàn)P-GA_CLKR2,F(xiàn)PGA_CLKR3為FPGA產(chǎn)生的10 MHz的驅(qū)動(dòng)時(shí)序,ARM_ROE為ARM產(chǎn)生的門控信號(hào)。這里還產(chǎn)生了一路控制行數(shù)據(jù)丟棄DG(Dump Gate)門控信號(hào)。該信號(hào)的擺幅同Rφ1,2,3。以上電路的連接均通過Multisim仿真,仿真波形如圖8、圖9所示。

2.2.2 Rφ2HV高壓倍增驅(qū)動(dòng)設(shè)計(jì)

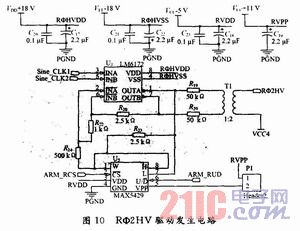

Rφ2HV的幅值決定著倍增倍數(shù),是EMCCD的一項(xiàng)重要可調(diào)參數(shù),必須在指定范圍內(nèi)可調(diào)以滿足不同場合的應(yīng)用。在設(shè)計(jì)Rφ2HV時(shí),由于其驅(qū)動(dòng)電壓擺幅高,現(xiàn)有的專用驅(qū)動(dòng)芯片不能滿足其高壓驅(qū)動(dòng)要求,必須采用特殊方法實(shí)現(xiàn)。根據(jù)E2V的文檔,Rφ2HV的波形即可以是正弦波,也可以是方波。如果為方波,則其高電平要先于Rφ1變高,如果為正弦波,則要求其波峰要在Rφ1下降時(shí)到達(dá)。

如果采用方波脈沖,因?yàn)镽φ2HV為11 MHz,根據(jù)計(jì)算,其系統(tǒng)值將達(dá)2 W,CCD97上的功耗也將達(dá)到1 W;如果采用正弦波形式,可使CCD97上的功耗降到100 mW。在此,采用正弦波方式產(chǎn)生Rφ2HV。

周期矩形脈沖信號(hào)用傅里葉級(jí)數(shù)展開后,除了基波外,只有奇次諧波,在通過一個(gè)低通濾波器后,便能轉(zhuǎn)化成正弦波。因?yàn)镕PGA只能產(chǎn)生TTL時(shí)序,這里通過先將TTL的方波轉(zhuǎn)化成正弦波,即可通過一個(gè)7階的巴特沃斯濾波器,將20 MHz以后的高頻分量衰減,保留基頻。在得到10 MHz的正弦信號(hào)后,通過第一級(jí)放大,這里采用National Semiconductor公司生產(chǎn)的LM6172來構(gòu)成。LM6172為雙通道高速、低失真、低功耗的電壓反饋型放大器。通過將LM6172的雙放大器組合起來形成雙端輸入/雙端輸出以增加帶負(fù)載能力。

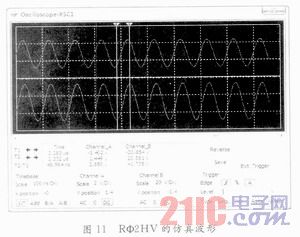

在設(shè)計(jì)中,把基本的放大參數(shù)預(yù)設(shè)為使輸入正弦信號(hào)放大到21 V,這樣產(chǎn)生的雙端信號(hào)經(jīng)過一個(gè)初次級(jí)電阻,比為1:4的高頻變換器達(dá)到輸出高電平為45 V、低電平為4 V的驅(qū)動(dòng)脈沖,供電電源為正負(fù)18 V的供電電源。為了使CCD97的增益可通過軟件控制調(diào)節(jié),這里使用了MAXIN公司生產(chǎn)的數(shù)字電位計(jì)MAX5429,預(yù)設(shè)目標(biāo)是電壓在40~50 V可調(diào)節(jié)。通過計(jì)算,反饋電阻參數(shù)如圖10所示。其中,MAX5429為10 KB,其有32個(gè)可編程節(jié)點(diǎn),上電后自動(dòng)設(shè)置為節(jié)點(diǎn)16。在硬件電路設(shè)計(jì)完畢時(shí),可通過ARM_RCS(片選信號(hào)),ARM_RUD(節(jié)點(diǎn)控制信號(hào))來調(diào)節(jié)輸出電壓,如圖10所示。這樣通過對ARM的對應(yīng)I/O口編程就能實(shí)現(xiàn)對CCD97的增益調(diào)節(jié)。但是因?yàn)檫@里選用了并聯(lián)法,故調(diào)節(jié)時(shí)增益是非線性變化的。圖11為正弦信號(hào)輸入(經(jīng)濾波器輸出)經(jīng)LM6172以及高頻變換器后輸出的仿真波形。

2.2.3 CCD97外圍電路

CCD97除了需要外部的各種高擺幅轉(zhuǎn)移脈沖,還需要各種幅值的控制信號(hào)輸入。

在該系統(tǒng)中,為了簡化設(shè)計(jì),固定ABD(抗曝光),φRL、φRH high(視頻信號(hào)復(fù)位端),DG high(行丟棄控制信號(hào)),DD(電源),OD(輸出放大器電源開光),RD(復(fù)位上電電源)的值為典型值,分別為18 V,0 V,10 V.18 V,24 V,28 V,17 V。φRL,φRH的典型脈沖寬度為10ns,這里仍然采用EL7457來產(chǎn)生。信號(hào)OG為控制CCD97輸出的門控信號(hào),它同時(shí)控制兩種模式的輸出,而ODH,ODL分別為控制CCD模式和EMCCD模式放大器輸出的電源開關(guān)。系統(tǒng)要求ODH和ODL可控,在需要時(shí)關(guān)閉,這樣就要求通過模擬的開關(guān)來控制ODH,ODL的電壓是+28 V還是接地。這里采用ADI公司的ADG453,它的VDD到GND端的輸入電壓可達(dá)32 V,模擬輸入/輸出值為VDD+2 V,達(dá)到這里控制ODH,ODL的通斷要求(28 V)。其中CCD和EMCCD端口分別為該CCD的視頻信號(hào)輸出。其輸出需要外接5 kΩ的負(fù)載。

3 結(jié)語

提出了一種新型的CCD驅(qū)動(dòng)電路,不僅可以達(dá)到幾十兆赫茲的驅(qū)動(dòng)頻率,而且編程方便,硬件電路簡單,根據(jù)用戶需求,只要更換晶振或適當(dāng)修改程序就能實(shí)現(xiàn)特定目的,具有很強(qiáng)的靈活性。通過仿真及實(shí)驗(yàn)驗(yàn)證,該方法切實(shí)可行,性價(jià)比高,不僅適用于CCD驅(qū)動(dòng)電路設(shè)計(jì),對于其他需要多種邏輯信號(hào)的場合也同樣適用。