摘要:文章通過對(duì)1553B總線協(xié)議的研究,結(jié)合現(xiàn)代EDA技術(shù),介紹了一種使用現(xiàn)場(chǎng)可編程邏輯器件(FPGA)設(shè)計(jì)1553B,總線協(xié)議用的manches-ter II型碼解碼器的方法。通過采用Verilog HDL硬件描述語言和原理圖混合輸入法,使設(shè)計(jì)簡潔有效。通過OuartusII開發(fā)軟件對(duì)設(shè)計(jì)進(jìn)行了時(shí)序約束和分析,最后給出了時(shí)序仿真圖,從而證明了這種設(shè)計(jì)是可行和可靠的。

關(guān)鍵詞:1553B總線協(xié)議;ManehesterII型碼;現(xiàn)場(chǎng)可編程門陣列

0 引言

MIL-STD-1553B是關(guān)于數(shù)據(jù)總線電氣特性和協(xié)議規(guī)范的美國軍用標(biāo)準(zhǔn),它的全稱為“飛機(jī)內(nèi)部時(shí)分制指令/響應(yīng)性多路傳輸數(shù)據(jù)總線”(Aircraft Internal Time Division Command/Response Multiplex Data Bus),該標(biāo)準(zhǔn)規(guī)定了飛機(jī)內(nèi)部數(shù)字式的命令/相應(yīng)時(shí)分制多路數(shù)據(jù)總線的技術(shù)要求。

在軍用機(jī)載數(shù)據(jù)總線方面,MIL-STD-1553B是應(yīng)用時(shí)間最早,也最為持久的,它為適應(yīng)工業(yè)和軍事的需要而提出,具有很高的可靠性和靈活性,加之技術(shù)比較成熟,所以應(yīng)用比較廣泛。目前,MIL-STD-1553B已廣泛應(yīng)用于軍事、工業(yè)和科技領(lǐng)域,從大型運(yùn)輸艦、空間補(bǔ)給站、轟炸機(jī)到各種戰(zhàn)斗機(jī),以及直升機(jī),都有其應(yīng)用,它甚至用于導(dǎo)彈系統(tǒng),以及用作飛行器和導(dǎo)彈之間的基本通信協(xié)議。我國于1987年頒布了相應(yīng)的軍標(biāo),目前,1553B總線已成為國內(nèi)軍用飛機(jī)航電系統(tǒng)的主流數(shù)據(jù)總線。

本文論述了一種運(yùn)用Verilog HDL語言,并結(jié)合現(xiàn)在EDA技術(shù)設(shè)計(jì)的可靠性強(qiáng)的1553B總線用ManchesterII型碼解碼器模塊。

1 1553B數(shù)據(jù)格式

1553B數(shù)據(jù)總線以異步、命令/響應(yīng)方式執(zhí)行數(shù)據(jù)信息的傳輸,其通信方式采用半雙工方式,總線控制器初始化所有個(gè)信息位、一個(gè)奇偶校驗(yàn)位和3個(gè)位長的傳輸,并控制數(shù)據(jù)總線上所有數(shù)據(jù)信息的傳輸,并控制數(shù)據(jù)總線上所有數(shù)據(jù)信息的傳輸,數(shù)據(jù)總線上的信息流有信息組成,而信息有三種類型的字組成:命令字、數(shù)據(jù)字和狀態(tài)字。有10種信息格式,每個(gè)信息格式至少包含兩個(gè)字,每個(gè)字有16的同步頭,所有的信息字都采用ManchesterlI型碼。

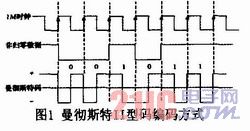

如圖1所示,1553B的數(shù)據(jù)傳輸速率是1Mbit/s。按照ManchesterII型碼規(guī)則,將邏輯“0”用編碼“01”來表示,其中“0”和“1”各占0.5 μs,也即用一個(gè)由低到高的跳變來表示;將邏輯“1”用編碼“10”來表示,其中“1”和“0”各占0.5 μs,也即用一個(gè)由高到低的跳變來表示。

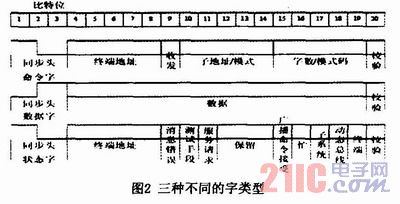

MIL-STD-1553B總線標(biāo)準(zhǔn)定義了三種字類型:命令字、數(shù)據(jù)字和狀態(tài)字。每一種字類型都有唯一的格式,但三種字類型有相同的數(shù)據(jù)結(jié)構(gòu),如圖2所示。每個(gè)字有20比特,最前面三個(gè)比特是同步字頭,標(biāo)志新字的開始,同步字頭波形是無效的Manchester碼,因?yàn)槠涮儍H僅發(fā)生在第二比特時(shí)間的正中。使用這種不同的模式,是為了讓解碼器在每個(gè)字的開頭重新建立同步,以及保持發(fā)送的整體穩(wěn)定性;接下去的十六比特是信息字段,三種類型的字有不同的含義;最后一個(gè)比特是該字的奇偶校驗(yàn)位,標(biāo)準(zhǔn)規(guī)定為奇校驗(yàn)。

2 EDA設(shè)計(jì)

本文設(shè)計(jì)的ManchesterII型碼解碼器選擇ALTERA公司的Cyclone系列的EPlC6Q240C6芯片作為目標(biāo)器件,在QuartusII9.0集成環(huán)境中,使用Verilog HDL硬件描述語言和原理圖混合輸入方法實(shí)現(xiàn),使設(shè)計(jì)簡潔有效。

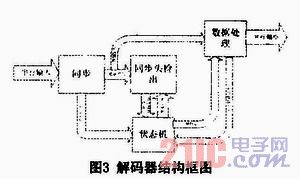

解碼器的功能是將1553B總線中串行輸入的數(shù)據(jù)轉(zhuǎn)變成并行數(shù)據(jù),并檢查數(shù)據(jù)和奇偶校驗(yàn)位是否正確,為下游的1553B處理器提供正確的數(shù)據(jù)。如圖3所示,解碼器包括同步模塊、同步頭檢出模塊、數(shù)據(jù)處理模塊、狀態(tài)機(jī)模塊。設(shè)計(jì)采用16M時(shí)鐘的工作頻率。

數(shù)據(jù)信號(hào)和使能信號(hào)可以在時(shí)鐘信號(hào)的一個(gè)周期之內(nèi)的任意時(shí)間來領(lǐng),也就是說無法定位數(shù)據(jù)信號(hào)和使能信號(hào)對(duì)于時(shí)鐘信號(hào)上升沿的時(shí)間間隔,這將使各模塊內(nèi)部的時(shí)鐘計(jì)數(shù)器無法準(zhǔn)確地計(jì)時(shí),使?fàn)顟B(tài)機(jī)無法準(zhǔn)確地進(jìn)行狀態(tài)跳變。

同步模塊的作用相當(dāng)于一個(gè)D觸發(fā)器,它可以使數(shù)據(jù)信號(hào)和使能信號(hào)相對(duì)于時(shí)鐘信號(hào)的上升沿有固定的時(shí)間間隔,這個(gè)時(shí)間間隔就是同步模塊的tco,即時(shí)鐘輸出延時(shí)。這樣就為下游模塊的時(shí)鐘計(jì)算和時(shí)序約束提供了一個(gè)固定的參數(shù),為各模塊的時(shí)鐘計(jì)數(shù)器準(zhǔn)確計(jì)時(shí)和狀態(tài)機(jī)正確跳變奠定了基礎(chǔ)。

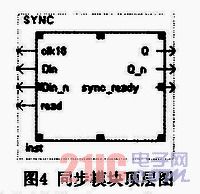

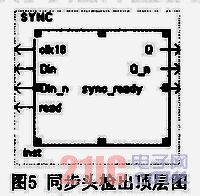

如圖4所示,同步模塊中Din和Din_n管腳(Din_n為Din的方向輸入信號(hào))接收來自1553B模擬收發(fā)器的數(shù)據(jù)信號(hào),read管腳接收模擬收發(fā)器發(fā)出的使能信號(hào)。產(chǎn)生與16MHz時(shí)鐘的上升沿同步的數(shù)據(jù)信號(hào)和使能信號(hào)。

同步頭檢出模塊是檢測(cè)1553B三種類型字的同步頭。如圖2所示,命令字和狀態(tài)字的同步頭是先高電平后低電平,數(shù)據(jù)字的同步頭是先低電平后高電平,三種字的同步頭的高低電平各占1.5 μs。在用Verilog HDL硬件描述語言設(shè)計(jì)中,本文通過設(shè)置兩個(gè)計(jì)數(shù)器,分別在時(shí)鐘信號(hào)上升沿的時(shí)候給高低電平計(jì)數(shù),理論上說兩個(gè)計(jì)數(shù)器都等于24的時(shí)候,同步頭才算檢出。但是要考慮到tco的影響,設(shè)計(jì)中當(dāng)兩個(gè)計(jì)數(shù)器到等于22的時(shí)候,就說同步頭檢出,這時(shí)產(chǎn)生message ready信號(hào),告訴狀態(tài)機(jī)要開啟數(shù)據(jù)處理模塊。如圖5所示,是同步頭檢出頂層圖。

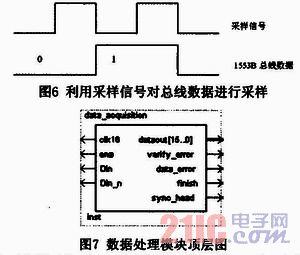

數(shù)據(jù)處理模塊是正確解碼后面的有效信息位,包括串并轉(zhuǎn)換、數(shù)據(jù)錯(cuò)誤檢測(cè)、校驗(yàn)位檢測(cè)。如圖6所示,利用把16MHz時(shí)鐘8分頻產(chǎn)生的2MHz的采樣信號(hào)對(duì)總線數(shù)據(jù)進(jìn)行采樣,可以在每一碼位的1/4周期處和3/4周期處采樣,這樣采樣的信號(hào)最可靠。當(dāng)一碼位兩次采樣的值不一樣時(shí),就認(rèn)為數(shù)據(jù)正確,并將第一次采樣的值發(fā)送給數(shù)據(jù)寄存器。如果一碼位兩次采樣的值相等,就認(rèn)為數(shù)據(jù)錯(cuò)誤,產(chǎn)生數(shù)據(jù)錯(cuò)誤信號(hào)dataerror。當(dāng)數(shù)據(jù)寄存器的前十六位的和除以2的余數(shù)等于第十七的數(shù)據(jù)時(shí),就認(rèn)為奇校驗(yàn)正確。否則就認(rèn)為錯(cuò)誤,并產(chǎn)生奇校驗(yàn)錯(cuò)誤信號(hào)verify_error信號(hào)。圖7所示為數(shù)據(jù)處理頂層圖。

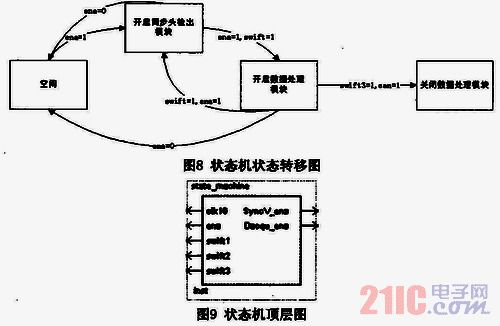

狀態(tài)機(jī)模塊是要正確地協(xié)調(diào)工作同步頭檢出模塊和數(shù)據(jù)處理模塊,如圖8所示狀態(tài)機(jī)模塊的狀態(tài)轉(zhuǎn)移圖。當(dāng)狀態(tài)機(jī)被使能時(shí),說明1553B總線數(shù)據(jù)來臨,此時(shí)狀態(tài)機(jī)產(chǎn)生SyncV end信號(hào)告訴同步頭檢出模塊開始工作。當(dāng)同步頭檢出模塊工作結(jié)束時(shí),產(chǎn)生Sync ready信號(hào),告訴狀態(tài)機(jī)要開啟數(shù)據(jù)處理模快。當(dāng)數(shù)據(jù)處理模塊工作到一定時(shí)間時(shí)會(huì)產(chǎn)生一個(gè)sync head信號(hào),這個(gè)信號(hào)的意義是要讓狀態(tài)機(jī)告訴同步頭檢出模塊開始檢測(cè)下一個(gè)字的同步頭。而此時(shí)數(shù)據(jù)處理模塊還沒有工作完,只有當(dāng)數(shù)據(jù)處理模塊產(chǎn)生finish信號(hào)時(shí),才表示數(shù)據(jù)處理模塊工作完成,告訴狀態(tài)機(jī)關(guān)閉數(shù)據(jù)處理模塊。圖9所示是狀態(tài)機(jī)頂層圖。

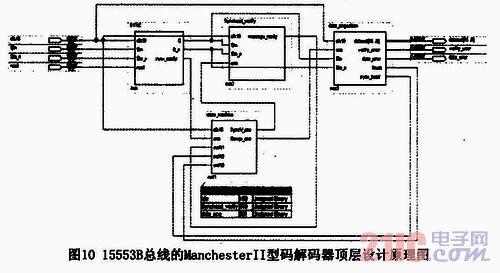

在QuartuslI中的原理圖輸入界面中,將以上各模塊正確地連接在一起,如圖10所示為1553B總線的manchesterII型碼解碼器的頂層設(shè)計(jì)原理圖。

3 時(shí)序約束與驗(yàn)證

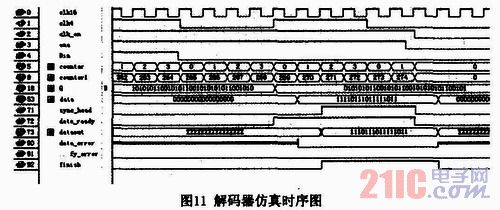

時(shí)序約束是FPGA設(shè)計(jì)中非常重要的環(huán)節(jié),只有建立了合理的時(shí)序約束,設(shè)計(jì)才能正常地工作。如今的FPGA中一般都有全銅層的全局時(shí)鐘驅(qū)動(dòng)網(wǎng)絡(luò),本設(shè)計(jì)中16MHz的時(shí)鐘設(shè)置成全局時(shí)鐘,可以有效地避免這些時(shí)鐘信號(hào)到達(dá)各寄存器時(shí)鐘短的時(shí)鐘偏斜。將時(shí)鐘的最高頻率設(shè)置成16.8MHz。圖11所示為解碼器的仿真時(shí)序圖,解碼器在一個(gè)字周期之后,解碼出數(shù)據(jù)為1110111011111011。

文章詳細(xì)介紹了一種利用FPGA實(shí)現(xiàn)的1553B總線用的ManchesterlI型碼解碼器,文章給出了解碼器各模塊的功能和實(shí)現(xiàn)方法,最后給出了頂層設(shè)計(jì)原理圖。給出的仿真時(shí)序圖證明這是一種可靠的實(shí)現(xiàn)方法。