電壓管理器是一種集成電路,在低電壓的情況下它可以用來(lái)對(duì)處理器進(jìn)行復(fù)位,避免處理器錯(cuò)誤操作以確保系統(tǒng)安全掉電。本文介紹了電壓管理器概念以及電壓管理器的重要性能,并以ispPAC-POWR1208P1為例探討電源電壓的監(jiān)測(cè)電路的應(yīng)用。

隨著亞微米技術(shù)的應(yīng)用,先進(jìn)的集成電路,例如那些在通信產(chǎn)品中所用到的處理器在增強(qiáng)性能和功能的同時(shí),還降低了功耗。這也導(dǎo)致了器件內(nèi)核電壓的降低,然而器件之間相互連接的標(biāo)準(zhǔn)需要不同種類(lèi)的I/O電壓,使得需要給這些器件提供多種電源電壓。在一個(gè)典型的處理器數(shù)據(jù)手冊(cè)中,除了定義1.2V的內(nèi)核電壓、2.5V和3.3V的I/O電壓以外,同時(shí)也定義了允許的電壓變化范圍。例如,1.2V的范圍是±3%、2.5V和3.3V的范圍是±5%。只要電源電壓的波動(dòng)在其允許的范圍之內(nèi),處理器就會(huì)正常工作。如果器件的內(nèi)核電壓降到一定的門(mén)限以下,處理器開(kāi)始錯(cuò)誤理解指令。如果I/O接口的電壓降到信號(hào)規(guī)格以下,在處理器和存儲(chǔ)器之間傳送的數(shù)據(jù)就會(huì)變得模糊,致使處理器誤讀指令,由此引起錯(cuò)誤的指令。

|

|

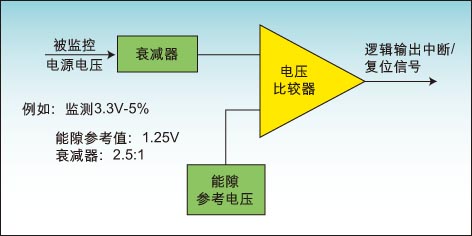

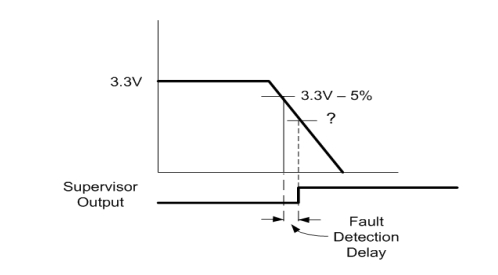

圖1:?jiǎn)坞娫措妷汗芾砥麟娐贰?/i> |

由于錯(cuò)誤的指令,就會(huì)導(dǎo)致處理器不可預(yù)知的行為。在某些時(shí)候,處理器可能重寫(xiě)電路板上的閃存存儲(chǔ)器,從而引起整個(gè)電路板不能正常工作。在電源電壓低于門(mén)限的條件下,板上的ASIC/FPGA都可能產(chǎn)生不可預(yù)知的行為。例如,對(duì)用于網(wǎng)絡(luò)處理的ASIC,當(dāng)電源電壓低于門(mén)限時(shí),它可能發(fā)出一些混亂的數(shù)據(jù)包,或者遺失一些內(nèi)部緩存的數(shù)據(jù)包,因此引起錯(cuò)誤的信息。電壓管理器就是用于防止這種不可預(yù)知的行為。

電壓管理器的概念

電壓管理器是一種集成電路,在低電壓的情況下它可以用來(lái)對(duì)處理器進(jìn)行復(fù)位,避免處理器錯(cuò)誤操作。在某些情況下,電壓管理器可以中斷處理器當(dāng)前的指令操作流程,給處理器提供早期的告警信息,以確保系統(tǒng)安全掉電。

一個(gè)典型的電壓管理器(如圖1所示)包括一個(gè)電壓比較器、能隙(band-gap)參考電壓源和用于設(shè)置監(jiān)測(cè)電壓閾值的電壓衰減器。比較器的輸出可以用于中斷處理器的操作或者對(duì)其復(fù)位。

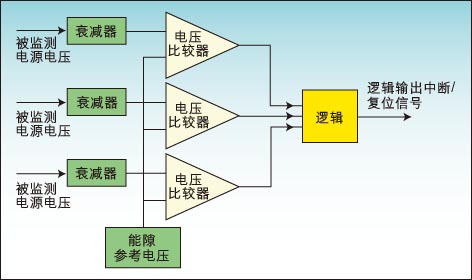

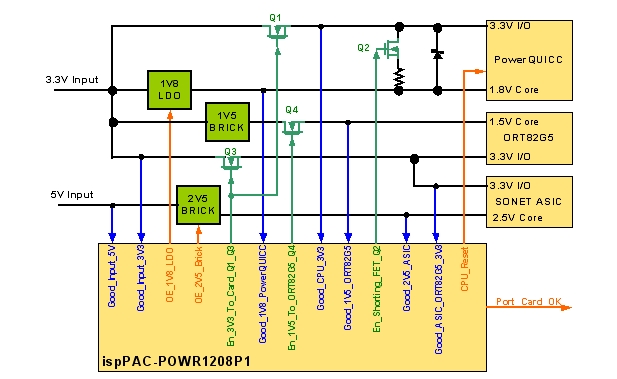

如圖2所示,這是一個(gè)用于多電源電壓監(jiān)測(cè)的器件結(jié)構(gòu)。這類(lèi)器件包含多個(gè)比較器,這些比較器擁有各自獨(dú)立的衰減器,以此來(lái)完成對(duì)不同電源電壓的監(jiān)測(cè)。其比較器的輸出經(jīng)邏輯組合提供一個(gè)單一的輸出信號(hào)去中斷或者復(fù)位處理器。

電壓管理器的精確性

如圖1所示的電路,這是一個(gè)假設(shè)的理想框圖,其中包括能隙電壓參考源(輸出電壓為1.25V),衰減器(當(dāng)輸入電壓為3.135V時(shí),其輸出為準(zhǔn)確的1.25V)和理想的比較器(所謂理想的比較器,是指該比較器沒(méi)有任何偏移,無(wú)窮大的增益,零傳播延遲,當(dāng)受監(jiān)測(cè)的電壓為3.135V時(shí),比較器總是準(zhǔn)確地翻轉(zhuǎn)。)

|

|

圖2:三種電源電壓監(jiān)測(cè)電路。 |

在現(xiàn)實(shí)中,能隙參考電壓隨溫度變化而改變,衰減器的輸出電壓隨器件不同而不同,這樣會(huì)造成比較器的不準(zhǔn)確。累計(jì)起來(lái),在整個(gè)工作溫度范圍和電壓范圍內(nèi)這些變化因素會(huì)使比較器的閾值發(fā)生變化。管理器的準(zhǔn)確性指標(biāo)就是對(duì)不同器件在整個(gè)工作溫度范圍內(nèi)實(shí)際電壓閾值門(mén)限的度量。

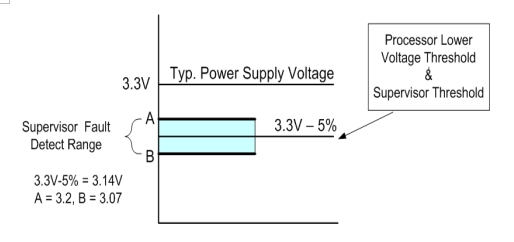

圖3為表示電壓管理器精度的示意圖。以圖1所示的單電源電壓管理器為例,電源電壓出錯(cuò)門(mén)限設(shè)置在3.3V-5%(3.135V)。如果電源電壓管理器的精度為2%,在其范圍以外3.135-2%(3.072V)或3.135+2%(3.2V)的任何地方都可以指示出電源錯(cuò)誤。如圖3中的A和B所示。

如果電源電壓在3.2V時(shí),出現(xiàn)電源錯(cuò)誤標(biāo)示,即意味著應(yīng)該阻止處理器操作,盡管此時(shí)處理器在這種情況下或許能正常地的工作。更嚴(yán)重的情況是當(dāng)電源電壓降到3.07V時(shí),處理器在低于指定的最低的門(mén)限電壓下工作,極有可能出現(xiàn)錯(cuò)誤的操作。使采用電源管理器監(jiān)控電源電壓的目的毫無(wú)用處。

補(bǔ)償電壓管理器的精確性

由于電壓管理器的不準(zhǔn)確,可能使處理器工作在不希望的低電壓情況下。為了避免這種情況的發(fā)生,電壓管理器的閾值門(mén)限必須仔細(xì)選擇,使得電源出錯(cuò)監(jiān)測(cè)范圍落在處理器正常工作的電源范圍以?xún)?nèi)。如圖4所示,如果將電壓管理器的閾值電壓設(shè)置在3.2V,判斷電源出錯(cuò)的范圍電壓從3.14V到3.26V,這樣就可以避免處理器工作在低于門(mén)限電壓(3.3V-5%)。

|

|

圖3:精度為2%的管理器故障檢測(cè)。 |

在圖4中,電壓管理器的門(mén)限設(shè)置為3.2V,其計(jì)算公式如下:

這里:VTSup為電壓管理器的門(mén)限值;Vin為電源電壓正常輸入值;

VCktTol為電路電源電壓容忍值;Asup為電壓管理器的準(zhǔn)確度。在這個(gè)例子中,Vin為3.3V,VCktTol為5%,Asup為2%,將這些值代入公式(1)中,

當(dāng)所選擇的電壓管理器的閾值門(mén)限電壓為3.2V或者以上時(shí),在電源供電電壓等于或者小于3.3V-5%時(shí),處理器將處于復(fù)位狀態(tài)。

電源電壓輸出的變化決定電壓管理器的準(zhǔn)確度

電源的輸出電壓由于各種不同的原因與典型值之間有差異,這些因素包括:負(fù)載電流,工作的環(huán)境溫度以及器件與器件之間的差異。一種通常的做法是在選擇電源時(shí),選擇其電壓的偏差值范圍小于單板電路對(duì)電壓所能容忍的范圍。例如,電源電壓的波動(dòng)范圍為3%,而單板電路對(duì)電源電壓的要求其變化范圍是5%。電源電壓輸出的最小值為3.3V-3%=3.2V,具有2%精度的電壓管理器的門(mén)限電壓范圍為3.14V到3.26V。這就是說(shuō),無(wú)論什么時(shí)候只要電源電壓輸出低于3.26V(例如,動(dòng)態(tài)電流的增加,溫度升高等原因),電壓管理器就能檢查出電源錯(cuò)誤信息并對(duì)處理器復(fù)位,同時(shí)導(dǎo)致系統(tǒng)間歇故障。

|

|

圖4:基于修正門(mén)限電壓后的錯(cuò)誤監(jiān)測(cè)。 |

在設(shè)定的電源電壓輸出范圍值和單板電路容忍電壓的范圍值,等式2可以用來(lái)計(jì)算需要的電壓管理器的精度。

這里:VSupRng為電源電壓輸出范圍值百分比;VCktTol為板上電路所能容忍的電壓范圍值百分比;Asup為電壓管理器的精度百分比。

請(qǐng)注意,在公式(2)中電壓管理器的精度與實(shí)際的電源電壓無(wú)關(guān),而僅僅與電源輸出電壓偏差范圍和單板電路對(duì)工作電壓容忍范圍有關(guān)。

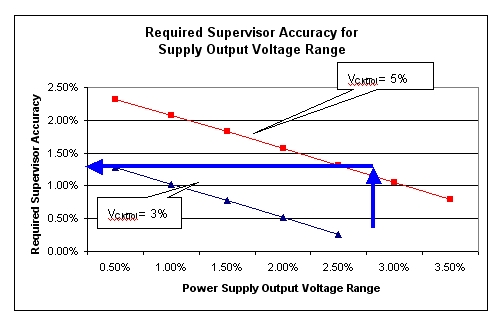

如圖5所示,曲線(xiàn)圖表示所計(jì)算出的管理器的精度與電源電壓輸出范圍的關(guān)系。這里有兩條曲線(xiàn),對(duì)應(yīng)不同板上電路的電源電壓容忍范圍,分別是3%和5%。如圖5中的箭頭所指,把一個(gè)電壓輸出范圍在3%的電源用到板上電路,其電壓容忍范圍為5%時(shí),要求電壓管理器的精度為1%。

在一個(gè)多電壓的電路板上,有些器件的電壓容忍范圍是3%。如果電壓管理器的精度是1%,如圖5所示,電源電壓輸出的范圍將被限制在1%的范圍。由此可清楚地得出,對(duì)于可靠的系統(tǒng)操作,電壓管理器的精度是一個(gè)極為重要的因素。例如,由Lattice提供的ispPAC-POWR1208P1芯片,該器件在室溫條件下提供0.5%的電壓監(jiān)測(cè)精度。同時(shí),該單芯片可以精確監(jiān)測(cè)多達(dá)12種電源。對(duì)于可靠的系統(tǒng)操作,不僅僅電壓管理器的精度重要,而且錯(cuò)誤監(jiān)測(cè)的時(shí)延也需要考慮。以下將討論該內(nèi)容。

電壓管理器的錯(cuò)誤監(jiān)測(cè)時(shí)延

錯(cuò)誤監(jiān)測(cè)時(shí)延是指當(dāng)電源電壓降到電壓管理器所設(shè)置的門(mén)限電壓值時(shí),電壓管理器的指示翻轉(zhuǎn),指示出錯(cuò)誤的時(shí)間。圖6所示,當(dāng)3.3V的電源電壓在錯(cuò)誤期間,同時(shí),電壓管理器監(jiān)測(cè)出錯(cuò)誤后,使其輸出翻轉(zhuǎn)。

|

|

圖5:輸出電壓范圍與電壓管理器精度曲線(xiàn)圖。 |

請(qǐng)注意,為了簡(jiǎn)化,這里的討論忽略錯(cuò)誤監(jiān)測(cè)的準(zhǔn)確度。如圖6所示,電壓管理器報(bào)告錯(cuò)誤的時(shí)間越長(zhǎng),電源電壓下降的幅度越大。例如,當(dāng)電源電壓的衰減率為1V/ms,電壓管理器的閾值為3.3V-5%。這里有兩種情形:

情形1: 錯(cuò)誤監(jiān)測(cè)時(shí)延為1ms。在這種情況下,電源電壓繼續(xù)往下掉。當(dāng)處理器被復(fù)位時(shí),電源電壓可能已降到低于處理器所能容忍的最低電壓門(mén)限以下。盡管處理器的電壓范圍要求是3.3V+/-5%,由于錯(cuò)誤監(jiān)測(cè)時(shí)延為1ms,使得當(dāng)電源電壓下降到2V時(shí),處理器還在執(zhí)行命令。很顯然,高精度的電壓監(jiān)測(cè)沒(méi)有發(fā)揮其作用。

情形2: 錯(cuò)誤監(jiān)測(cè)時(shí)延為50us。由于錯(cuò)誤監(jiān)測(cè)時(shí)延為50us,當(dāng)電壓管理器輸出指示信息時(shí),供給處理器的電源電壓已經(jīng)從門(mén)限電壓值3.3V-5%再下降50mV。再次強(qiáng)調(diào),在此刻的電壓值不能確保處理器的正常工作。

為可靠的錯(cuò)誤監(jiān)測(cè)提高門(mén)限閾值

現(xiàn)在,將門(mén)限電壓調(diào)整到比3.3V-5%高50mV,當(dāng)電源電壓下降到門(mén)限附近時(shí),處理器將被復(fù)位。在這種應(yīng)用例子中,錯(cuò)誤監(jiān)測(cè)時(shí)延為1ms是不能接受的。但是,對(duì)于錯(cuò)誤監(jiān)測(cè)時(shí)延為50us,需要將門(mén)限電壓設(shè)置在比處理器所能容忍的最低操作電壓高50mV。

很明顯,為保證系統(tǒng)操作可靠,電壓管理器不僅僅要考慮管理器的精度,同時(shí)也要考慮錯(cuò)誤監(jiān)測(cè)的時(shí)延。由于過(guò)高的輸入電壓會(huì)造成器件的損壞,為避免損壞器件,對(duì)高電壓的監(jiān)測(cè)也是很重要的。在這種情況下,對(duì)過(guò)電壓的錯(cuò)誤監(jiān)測(cè)速度要比對(duì)次電壓的錯(cuò)誤監(jiān)測(cè)速度更重要。例如,Lattice的ispPAC-POWR1208可以同時(shí)監(jiān)測(cè)12路電源電壓,錯(cuò)誤監(jiān)測(cè)時(shí)延為4us。

以上的例子只是考慮到對(duì)單電源使用非常精確的電壓管理器。在現(xiàn)實(shí)情況中,需要監(jiān)測(cè)的電源電壓不僅僅只有一種,經(jīng)常都是多種電壓。電壓管理器必須具備同時(shí)監(jiān)測(cè)多種電源電壓的能力,并且要有最小的錯(cuò)誤監(jiān)測(cè)時(shí)延。

|

|

圖6:?jiǎn)伟邋e(cuò)誤監(jiān)測(cè)示意圖。 |

增加系統(tǒng)可靠性的其它因素

為了可靠的電源電壓錯(cuò)誤監(jiān)測(cè),其他的因素也需要考慮。它們是:

尖脈沖濾波器。單板在實(shí)際工作中,電源上通常是有噪聲的。這些噪聲的產(chǎn)生可能來(lái)源于電源的紋波,或者來(lái)源于當(dāng)板上器件工作時(shí)的瞬變電流。這些噪聲都會(huì)引起電壓管理器的比較器的隨機(jī)翻轉(zhuǎn),為了防止這種情況的發(fā)生,電壓管理器在輸入端有一個(gè)尖脈沖濾波器,為門(mén)限比較器提供干凈的輸入。

遲滯。在門(mén)限比較器的輸入端設(shè)置少許的遲滯電壓,以此防止當(dāng)電源電壓在門(mén)限閾值附近時(shí)比較器由于電源噪聲引起的多次翻轉(zhuǎn)。

多路電壓同時(shí)錯(cuò)誤監(jiān)測(cè)電路

以下的方案是以L(fǎng)attice的ispPAC-POWR1208P1為例,探討電源電壓的監(jiān)測(cè)電路。如前面提及到的,該芯片提供的監(jiān)測(cè)精度為0.5%,錯(cuò)誤監(jiān)測(cè)時(shí)延為4us.

Power1208P1有12個(gè)高精度的模擬輸入比較器。每路輸入都可以單獨(dú)編程,設(shè)置不同的門(mén)限(共384個(gè)階梯),錯(cuò)誤監(jiān)測(cè)的精度為0.5%。另外,1208P1還有獨(dú)立可編程的電壓參考以供電源電壓監(jiān)測(cè),4個(gè)抗噪聲的數(shù)字輸入端以及4個(gè)漏極開(kāi)路輸出,用于系統(tǒng)控制接口,4個(gè)片內(nèi)可編程計(jì)數(shù)器,1個(gè)1MHz的片內(nèi)振蕩器,用于時(shí)延控制和16個(gè)宏單元的PLD用于實(shí)現(xiàn)電源順序控制功能。并且,較為嚴(yán)重的噪聲環(huán)境下,Power1208P1也能正常工作,其工作的電壓范圍從2.7V到5.5V。

|

|

圖7:用于ATM卡的電源管理方案。 |

在12路電源電壓監(jiān)測(cè)輸入端,每路都具備以下特點(diǎn):

可獨(dú)立編程門(mén)限電壓值的比較器:

1. 電壓范圍從0.68V到5.95V共有384階梯設(shè)置,一個(gè)80mV的電源電壓放電門(mén)限閾值監(jiān)測(cè)。

2. 0.5%門(mén)限閾值精度(因工藝和電源電壓,溫度變化其最大值為0.9%)

高速的錯(cuò)誤監(jiān)測(cè):

1. 當(dāng)沒(méi)有尖脈沖濾波器時(shí),錯(cuò)誤監(jiān)測(cè)時(shí)延為4us

2. 當(dāng)設(shè)置尖脈沖濾波器時(shí),錯(cuò)誤監(jiān)測(cè)時(shí)延為32us

遲滯電壓:

同一個(gè)芯片可以用作去監(jiān)測(cè)不同的電源電壓,因?yàn)槊柯份斎氲拈T(mén)限是可編程的。不需要任何附加的外圍器件(電阻,電容或抑制尖脈沖的電感)。另外,在Lattice提供的免費(fèi)PAC-Designer軟件里,可以單獨(dú)設(shè)置每一路模擬輸入的門(mén)限值。

圖7所示的電路在ATM端口卡上實(shí)現(xiàn)完整的電源管理功能,3.3V和5.0V電源是由背板提供的。所需的電源管理功能如下:

第一步,等待背板的電源穩(wěn)定。

第二步,為不同的器件產(chǎn)生各自所需的加電順序。

第三步,當(dāng)這些電源電壓都穩(wěn)定后,時(shí)延一定的時(shí)間,釋放對(duì)處理器的復(fù)位信號(hào)。

第四步,對(duì)所有電源電壓進(jìn)行監(jiān)測(cè),一旦任何一路電源出現(xiàn)故障,對(duì)處理器復(fù)位。如果電源故障一直持續(xù),啟動(dòng)單板電源掉電操作。

第五步,根據(jù)設(shè)計(jì)要求完成規(guī)定的掉電順序控制。

在圖7中,1208P1芯片同時(shí)對(duì)7種電源進(jìn)行監(jiān)測(cè)。根據(jù)操作的步驟,處理電源電壓錯(cuò)誤監(jiān)測(cè)的方法是不同的。片內(nèi)的CPLD用于控制電源電壓管理功能。例如:

在第一步,1208P1檢測(cè)從背板來(lái)的3.3V和5.00V電壓。其目的是在打開(kāi)單板上其他電源電壓時(shí)確保該兩組電壓已經(jīng)穩(wěn)定,不會(huì)產(chǎn)生對(duì)處理器的復(fù)位信號(hào),其原因是該兩組電源電壓還在所設(shè)定的門(mén)限電壓值以下。

在第二步,1208P1對(duì)每一路電壓進(jìn)行檢測(cè),確保正確的上電順序。如果這個(gè)啟動(dòng)的處理過(guò)程在規(guī)定的時(shí)間內(nèi)沒(méi)有完成,1208P1將所有電源關(guān)掉。

在第三步,精確的錯(cuò)誤監(jiān)測(cè)過(guò)程開(kāi)始,在所有電壓穩(wěn)定后,延伸復(fù)位脈沖以確保CPU正確啟動(dòng)。精確的監(jiān)測(cè)繼續(xù)到第四步。

第四步過(guò)程表示板上電路工作正常,繼續(xù)對(duì)所有電源電壓進(jìn)行精確的監(jiān)測(cè)。無(wú)論是單板上的任何電源出錯(cuò),或者單板突然從插槽中取出,CPU將被復(fù)位。減少CPU由于在低電壓的情況下誤操作的可能性。

本文小結(jié)

為了完成可靠的電源電壓錯(cuò)誤監(jiān)測(cè),所需的電壓管理器的精度應(yīng)考慮到電源電壓輸出的電壓偏差范圍和器件正常工作的電壓容忍范圍。除了電壓管理器的精度以外,工程師還需要考慮到電壓管理器的錯(cuò)誤監(jiān)測(cè)時(shí)延。

由于1208P1提供12路高精度的模擬輸入,并且每一路的門(mén)限閾值設(shè)置可編程,使設(shè)計(jì)更靈活和簡(jiǎn)單。帶有遲滯特性和尖脈沖濾波特性的輸入使系統(tǒng)更具有抗干擾性,同時(shí)錯(cuò)誤監(jiān)測(cè)的響應(yīng)速度極快,ispPAC-POWR1208P1芯片適合于對(duì)所有多電源供電的電路板進(jìn)行電源管理。1208P1的高精度和快速錯(cuò)誤監(jiān)測(cè)能力,可最大化地增加電源電壓容忍范圍,能用低成本的電源而同時(shí)保持高的系統(tǒng)可靠性。由于每一路被監(jiān)測(cè)的輸入錯(cuò)誤門(mén)限是可編程的,因此一個(gè)器件可以用于同時(shí)監(jiān)測(cè)各種的電源電壓。另外,片內(nèi)CPLD的邏輯功能可以完成單板所有的電源管理。基于圖形化的設(shè)計(jì)軟件使電源管理器功能的完成變得非常方便和易用。