目前智能儀器已廣泛應(yīng)用于科研和工業(yè)生產(chǎn)當(dāng)中,但是許多儀器分散在不同的地理位置上,不易操作和維護(hù),并且實(shí)時(shí)跟蹤性能差,人為誤差大,數(shù)據(jù)無法保存,另外大量高檔儀表價(jià)格相當(dāng)昂貴。為解決上述難題,在計(jì)算機(jī)的提示下完成操作,可以減少人為因素造成的損壞,并提高測試數(shù)據(jù)的準(zhǔn)確度。由于智能儀器是RS 232接口,上位機(jī)用的是USB接口,所以還需由FPGA實(shí)現(xiàn)RS232與USB之間的接口轉(zhuǎn)換。由于FPGA可以并行處理,集成度高,可用資源豐富,所以利用FPGA進(jìn)行數(shù)據(jù)處理,可以減少上位機(jī)的工作量,減少數(shù)據(jù)處理的時(shí)間,還可以縮短設(shè)計(jì)周期,減小板卡體積,以便于集成到其他板卡上。

1 控制系統(tǒng)及接口簡介

1.1 系統(tǒng)功能

在整個(gè)系統(tǒng)中,上位機(jī)可以實(shí)時(shí)對系統(tǒng)進(jìn)行監(jiān)控,并下發(fā)相應(yīng)的命令。智能儀器傳出的數(shù)據(jù)通過RS 232接口傳送到FPGA,F(xiàn)PGA根據(jù)上位機(jī)下發(fā)的命令對這些數(shù)據(jù)進(jìn)行判決、處理,然后經(jīng)過USB接口上傳給上位機(jī),再由上位機(jī)對FPGA處理過的數(shù)據(jù)進(jìn)行顯示、存儲等操作。

1.2 USB接口芯片簡介

本設(shè)計(jì)采用的是CYPRESS半導(dǎo)體公司的EZ-USBFX2系列芯片CY7C68013。CY7C68013是一款高性能USB 2.0微控制器,它提供了全面的USB 2.0外圍設(shè)備解決方案。工作模式有Port,Slave FIFO和GPIFMaster三種,本方案采用Slave FIFO模式。在該模式下,外部控制器(如FPGA)可像對普通FIFO一樣對FX2中端點(diǎn)為2,4,6,8的數(shù)據(jù)緩沖區(qū)進(jìn)行讀/寫。FX2內(nèi)嵌的8051固件的功能只是配置Slave FIFO相關(guān)的寄存器,以及控制FX2何時(shí)工作在Slave FIFO模式下。一旦8051固件將相關(guān)的寄存器配置完畢,且使自身工作在Slave FIFO模式下后,外部邏輯(如FPGA)即可按照Slave FIFO的傳輸時(shí)序,高速地與主機(jī)進(jìn)行通信,而在通信過程中不需要8051固件的參與。

1.3 RS 232接口簡介

RS-232C標(biāo)準(zhǔn)(協(xié)議)的全稱是EIA-RS-232C標(biāo)準(zhǔn)。EIA-RS-232C是用正負(fù)電壓來表示邏輯狀態(tài)的,與TTL以高低電平表示邏輯狀態(tài)的規(guī)定不同。因此,為了能夠與計(jì)算機(jī)接口或終端的TTL器件連接,必須使EIA-RS-232C與TTL電路之間進(jìn)行電平和邏輯關(guān)系的變換。實(shí)現(xiàn)這種變換的方法可用分立元件,也可用集成電路芯片。該設(shè)計(jì)用的是MAX3232芯片。

RS 232的數(shù)據(jù)傳輸格式如圖1所示。

RS 232傳輸格式包含起始位(1 b)、有效數(shù)據(jù)位(8 b)、奇偶校驗(yàn)位(0~2 b)、停止位(1 b)。傳輸線在空閑時(shí)為高電平,因此起始位為低電平,停止位為高電平。奇偶校驗(yàn)位可設(shè)置為奇校驗(yàn)、偶校驗(yàn)或不校驗(yàn),有效數(shù)據(jù)位是從低位開始傳送。

2 FPGA設(shè)計(jì)

2.1USB接口時(shí)序

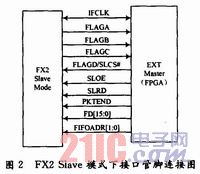

在Slave FIFO方式下,外部邏輯與FX2的連接信號如圖2所示。

在Slave FIFO模式下,CY7C68013芯片為端口2,4,6,8提供滿空標(biāo)志位FLAGA,F(xiàn)LAGB,F(xiàn)LAGC,F(xiàn)LAGD。IFCLK為FX2輸出的時(shí)鐘,可作通信的同步時(shí)鐘;SLCS為FIFO的片選信號;SLOE為FIFO輸出使能;SLRD為FIFO讀信號;SLWR為FIFO寫信號。對FPGA來說,4個(gè)端口分別為4個(gè)FI-FO。FPGA檢測4個(gè)滿空標(biāo)志位來分別對相應(yīng)的FIFO進(jìn)行讀/寫。FPGA可以選擇同步或異步讀/寫,在該設(shè)計(jì)中采用異步讀/寫。在異步Slave FIFO寫時(shí),時(shí)鐘由FPGA提供。數(shù)據(jù)在SLWR的每個(gè)有效一無效的跳變沿時(shí)被寫入,F(xiàn)IFO寫指針遞增。異步Slave FIFO讀時(shí),F(xiàn)IFO讀指針在SLRD的每個(gè)有效一無效的跳變沿時(shí)遞增以改變數(shù)據(jù)。

2.2 FPGA程序設(shè)計(jì)

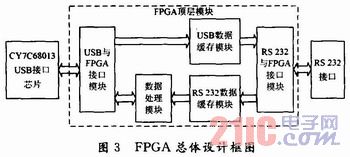

FPGA設(shè)計(jì)是整個(gè)系統(tǒng)的核心部分,由VHDL語言實(shí)現(xiàn)。FPGA實(shí)現(xiàn)了USB與RS 232接口的轉(zhuǎn)換、數(shù)據(jù)的處理、命令的傳輸?shù)裙δ堋S辛松厦娴慕涌跁r(shí)序,便可以進(jìn)行FPGA設(shè)計(jì)。FPGA部分的總體設(shè)計(jì)如圖3所示。

模塊介紹:

USB與FPGA接口模塊:USB與FPGA之間的接口轉(zhuǎn)換模塊,主要功能為將USB接口傳過來的信息緩存到FPGA內(nèi)部FIFO,并將由數(shù)據(jù)處理模塊處理過的數(shù)據(jù)傳給USB芯片。即產(chǎn)生控制信號讀/寫USB芯片內(nèi)部FIFO。可以由讀/寫FIFO兩個(gè)有限狀態(tài)機(jī)實(shí)現(xiàn)。以讀取CY7C68013芯片內(nèi)數(shù)據(jù)為例,根據(jù)異步讀USB內(nèi)的FIFO時(shí)序圖可分為4個(gè)狀態(tài):空閑態(tài)、選擇地址態(tài)、準(zhǔn)備讀數(shù)據(jù)態(tài)、讀數(shù)據(jù)態(tài)、讀取后狀態(tài)。在空閑態(tài),當(dāng)讀事件發(fā)生時(shí)進(jìn)入選擇地址態(tài);在選擇地址態(tài),使FIFOADR[1:O]指向OUT FIFO,進(jìn)入準(zhǔn)備讀數(shù)據(jù)態(tài);在準(zhǔn)備讀數(shù)據(jù)態(tài),如FIFO空,在本狀態(tài)等待,否則進(jìn)入讀數(shù)據(jù)態(tài);在讀數(shù)據(jù)態(tài),使SLOE,SLRD有效,從數(shù)據(jù)線上讀數(shù),再使SLRD無效,以遞增FIFO讀指針,再使SLOE無效,進(jìn)入讀取后狀態(tài);在讀取后狀態(tài),如需傳輸更多的數(shù),進(jìn)入準(zhǔn)備讀數(shù)據(jù)態(tài),否則進(jìn)入空閑態(tài)。

USB數(shù)據(jù)緩存模塊:用來緩存計(jì)算機(jī)發(fā)給智能儀器的指令等信息。是由FPGA芯片的IP核生成的先入先出存儲器FIFO。容量為8b×512dept-h。占用1個(gè)塊RAM資源。

RS 232數(shù)據(jù)緩存模塊:用來緩存由智能儀器發(fā)出的數(shù)據(jù)。是由FPGA IP核生成的先入先出存儲器FIFO。容量為8 b×512 depth,占用1個(gè)塊RAM資源。

RS 232與FPGA接口模塊:RS 232與FPGA之間的接口轉(zhuǎn)換模塊。主要功能為進(jìn)行串/并和并/串轉(zhuǎn)換。將USB數(shù)據(jù)緩存模塊中緩存的內(nèi)容以合適的速率通過串口發(fā)給智能儀器,并將智能儀器發(fā)出的數(shù)據(jù)緩存到RS 232數(shù)據(jù)緩存模塊中。此模塊也是由兩個(gè)狀態(tài)機(jī)實(shí)現(xiàn)。串口通信必須要設(shè)定波特率,這里采用的波特率為9 600 Kb/s,采用的時(shí)鐘為50 MHz,相當(dāng)于傳送1位數(shù)據(jù)需要約5 028個(gè)時(shí)鐘周期,這里采用減法計(jì)數(shù)器來控制,即計(jì)數(shù)器計(jì)到5 028個(gè)時(shí)鐘周期后,就開始傳輸下一位數(shù)據(jù)。

數(shù)據(jù)處理模塊:主要功能為根據(jù)上位機(jī)的指令對RS 232數(shù)據(jù)緩存中的數(shù)據(jù)做出相應(yīng)的處理。處理后再向上位機(jī)傳。主要的處理方式有定時(shí)取數(shù)、平滑處理等。實(shí)現(xiàn)方式由狀態(tài)機(jī)等實(shí)現(xiàn)。FPGA頂層模塊:主要負(fù)責(zé)各模塊間數(shù)據(jù)流的流向。以及與外部芯片相連的輸入輸出信號的定義。

系統(tǒng)在工作時(shí),在采集數(shù)據(jù)上傳上位機(jī)時(shí),數(shù)據(jù)通道為:智能儀器發(fā)送的數(shù)據(jù)通過RS 232接口模塊存在RS232數(shù)據(jù)緩存模塊中緩存。當(dāng)緩存到一定的數(shù)據(jù)量后,再通過數(shù)據(jù)處理模塊連續(xù)的讀取FIFO中的數(shù)據(jù)并根據(jù)上位機(jī)發(fā)送的命令進(jìn)行相應(yīng)的數(shù)據(jù)處理,然后將處理的數(shù)據(jù)通過USB與FPGA接口模塊傳給USB接口。在上位機(jī)下發(fā)控制命令時(shí),數(shù)據(jù)通道為:上位機(jī)發(fā)送的命令通過USB口傳給FPGA的RS 232與FPGA接口模塊,此模塊判斷是數(shù)據(jù)處理指令還是控制儀器指令。如果是數(shù)據(jù)處理指令,則傳向數(shù)據(jù)處理模塊讓其按要求進(jìn)行數(shù)據(jù)處理。如果是控制儀器指令,則將其存入U(xiǎn)SB數(shù)據(jù)緩存模塊中,再由RS 232與FPGA接口模塊讀取,轉(zhuǎn)成RS2322格式后傳出。由于RS 232接口速度比USB接口慢,用FPGA內(nèi)部的異步時(shí)鐘FIFO解決速率匹配問題。將通過RS 232傳過來的數(shù)據(jù)緩存在FIFO中,然后存到一定數(shù)據(jù)量后再全部連續(xù)的取出,如此往復(fù),從而實(shí)現(xiàn)數(shù)據(jù)的連續(xù)采集及上位機(jī)的實(shí)時(shí)顯示。將通過USB傳過來的數(shù)據(jù)放在另一個(gè)FIFO中緩存,讓FPGA按照RS232的速率進(jìn)行讀取。這樣可以防止RS 232的速度跟不上USB的速度而產(chǎn)生的數(shù)據(jù)丟失。

3 仿真結(jié)果

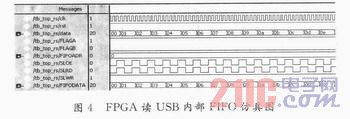

FPGA采用的系統(tǒng)時(shí)鐘頻率為50 MHz,仿真工具為Modelsim SE 6.5a,仿真用數(shù)據(jù)為連續(xù)的8 b數(shù)據(jù)。仿真結(jié)果如圖4所示。

圖4為FPGA讀USB內(nèi)部FIFO的仿真結(jié)果,DATA為模擬從USB口接到的數(shù)據(jù),該數(shù)據(jù)已存在于USB芯片的FIFO中。FIFODATA為FPGA接到的數(shù)據(jù),由上可以看出,F(xiàn)PGA可以將USB接受到的數(shù)據(jù)解析出來。

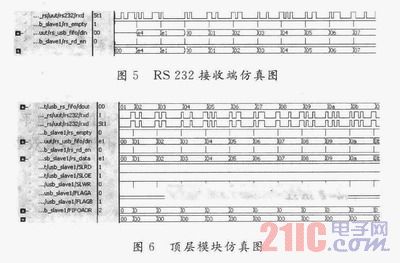

圖5為RS 232與FPGA接口部分仿真結(jié)果。可以看出,由RS 232接收串行數(shù)據(jù)RXD已經(jīng)轉(zhuǎn)換為并行數(shù)據(jù)din。程序中是在一個(gè)有效字節(jié)結(jié)束后將其存入FIFO中,由圖可以驗(yàn)證。圖6頂層模塊仿真圖,為了驗(yàn)證由FPGA發(fā)出的數(shù)據(jù)能正確的接受到,先由FPGA內(nèi)部發(fā)數(shù)據(jù),然后通過RS 232的TXD端口發(fā)出,讓RXD與TXD相連再接收,可以看出發(fā)出的數(shù)據(jù)可以被正確的接收回來并傳向USB接口,說明時(shí)序正確。同理可以驗(yàn)證USB端的收發(fā)時(shí)序。

4 結(jié)語

本文采用FPGA實(shí)現(xiàn)了USB與RS 232間的接口轉(zhuǎn)換及數(shù)據(jù)處理的功能。設(shè)計(jì)中先入先出存儲器的運(yùn)用解決了數(shù)據(jù)的緩存的和速率匹配問題,有限狀態(tài)機(jī)的運(yùn)用使得程序設(shè)計(jì)更加清晰可靠。該設(shè)計(jì)將復(fù)雜的信號運(yùn)算集中在FPGA中完成,利用FPGA獨(dú)特的并行處理能力,減小上位機(jī)工作量的同時(shí),提高了系統(tǒng)運(yùn)行速度。