在目前電子系統(tǒng)的設(shè)計(jì)中,,DSP+FPGA架構(gòu)越來越多,其原因在于該架構(gòu)兼顧了速度和靈活性,。通用DSP的優(yōu)點(diǎn)是通過編程可以廣泛應(yīng)用到產(chǎn)品中,,并且主流制造商生產(chǎn)的DSP已能滿足算法控制結(jié)構(gòu)復(fù)雜、運(yùn)算速度高,、尋址方式靈活和通信性能強(qiáng)大等需求,。但是傳統(tǒng)的DSP采用馮-諾依曼結(jié)構(gòu)或某種類型擴(kuò)展。此種結(jié)構(gòu)本質(zhì)上是串行的,,因此遇到需處理的數(shù)據(jù)量大,,對(duì)處理速度要求高,,但是對(duì)運(yùn)算結(jié)構(gòu)相對(duì)比較簡(jiǎn)單的底層信號(hào)處理算法則顯不出優(yōu)點(diǎn),適合采用FPGA硬件實(shí)現(xiàn),。而采用DSP+FPGA的數(shù)字硬件系統(tǒng)就可以把二者優(yōu)點(diǎn)結(jié)合起來,,兼顧速度和靈活性,既滿足底層信號(hào)處理要求,,又滿足高層信號(hào)處理要求,。采用此架構(gòu),就不可避免地遇到FPGA與DSP之間數(shù)據(jù)通信的問題,。本文討論了異步FIFO在FPGA與DSP通信中的運(yùn)用,,該方法具有傳輸速度快,穩(wěn)定可靠并且實(shí)現(xiàn)方便等優(yōu)點(diǎn),。

1 異步FIFO的結(jié)構(gòu)

由于FPGA和DSP具有各自的全局時(shí)鐘,將FPGA中的數(shù)據(jù)傳遞給DSP時(shí),,也就是將數(shù)據(jù)從一個(gè)時(shí)鐘域傳遞到另一個(gè)時(shí)鐘域,,并且目標(biāo)時(shí)鐘域與源時(shí)鐘域是不相關(guān)的,因此這些域中的動(dòng)作也是不相關(guān)的,,從而消除了同步操作的可能性,,并使系統(tǒng)重復(fù)地進(jìn)入亞穩(wěn)定狀態(tài)。亞穩(wěn)態(tài)也就是觸發(fā)器工作在一種不確定的狀態(tài),,這種不確定的狀態(tài)將會(huì)影響到下一級(jí)觸發(fā)器,,最終導(dǎo)致連鎖反應(yīng),從而使整個(gè)系統(tǒng)功能失常,。當(dāng)有大量的數(shù)據(jù)需要進(jìn)行跨時(shí)鐘域傳輸且對(duì)數(shù)據(jù)傳輸速度要求比較高的場(chǎng)合,,克服亞穩(wěn)態(tài)實(shí)現(xiàn)數(shù)據(jù)的高速穩(wěn)定傳輸,異步FIFO是一種簡(jiǎn)單,、快捷的解決方案,。

FIFO(First In First Out)是一種先進(jìn)先出的數(shù)據(jù)緩存器,而異步FIFO是用一種時(shí)鐘寫入數(shù)據(jù),,用另一種時(shí)鐘讀出數(shù)據(jù),。以FPGA向DSP傳輸數(shù)據(jù)為例,F(xiàn)PGA產(chǎn)生寫時(shí)鐘,,在寫時(shí)鐘的控制下同步向FIFO中寫入數(shù)據(jù),,并且使相應(yīng)的寫指針增加1;DSP提供讀時(shí)鐘,,在讀時(shí)鐘的控制下同步地從FIFO中取出數(shù)據(jù),,并且使相應(yīng)的讀指針增加1。這里唯一的跨時(shí)鐘域操作就是對(duì)FIFO空或滿的判斷,。如何根據(jù)異步的讀,、寫指針信號(hào)產(chǎn)生正確的空,、滿標(biāo)志,保證數(shù)據(jù)正確的寫入或讀出,,而不發(fā)生溢出或讀空的狀態(tài)出現(xiàn),。就必須保證FIFO在滿的情況下,不能進(jìn)行寫操作,,在空的狀態(tài)下不能進(jìn)行讀操作,,這是異步FIFO設(shè)計(jì)的關(guān)鍵。

判斷FIFO為空還是滿,,本文采用如下算法:構(gòu)造一個(gè)指針寬度為N+1,,深度為2N Byte的FIFO,當(dāng)讀,、寫指針的二進(jìn)制碼中最高位不一致而其他N位都相等時(shí),,F(xiàn)IFO為滿。當(dāng)讀,、寫指針完全相等時(shí),,F(xiàn)IFO為空。例如:一個(gè)深度為8 Byte的FIFO,,F(xiàn)IFO_WIDTH=8,,F(xiàn)IFO_DEPTH=2N= 8,N=3,,指針寬度為N+1=4,。起初rd_ptr_bin和wr_ptr_bin均為“0000”。此時(shí)FIFO中寫入8 Byte的數(shù)據(jù),,wr_ptr_bin=“1000”,,rd_ptr_ bin=“0000”。當(dāng)然,,這就是滿條件?,F(xiàn)在,假設(shè)執(zhí)行了8次讀操作,,使得rd_ptr_bin=“1000”,,這就是空條件。另外的8次寫操作將使wr_ ptr_bin等于“0000”,,但rd_ptr_bin仍然等于“1000”,,因此FIFO為滿條件。顯然起始指針無需為“0000”,。假設(shè)它為“0100”,,并且FIFO為空,那么寫入8 Byte會(huì)使wr_ptr_bin=“1100”,,rd_ptr_bin仍為“0100”,。這說明FIFO為滿,。

不可以將讀、寫指針直接比較,,因?yàn)樽x,、寫指針在不同的時(shí)鐘域,直接比較會(huì)出現(xiàn)亞穩(wěn)態(tài)現(xiàn)象,。在涉及到觸發(fā)器的電路中,,亞穩(wěn)態(tài)無法徹底消除,只能將其發(fā)生的概率降到最低,。其中的一個(gè)方法就是使用格雷碼,。格雷碼在相鄰的兩個(gè)碼元之間只有一位變換。這就避免了讀,、寫指針與時(shí)鐘同步的時(shí)候發(fā)生亞穩(wěn)態(tài)現(xiàn)象,。另外一種方法就是使用兩級(jí)D觸發(fā)器同步,假設(shè)一個(gè)D觸發(fā)器發(fā)生亞穩(wěn)態(tài)的概率為P,,那么兩個(gè)級(jí)聯(lián)的D觸發(fā)器發(fā)生亞穩(wěn)態(tài)的概率就為P2,。

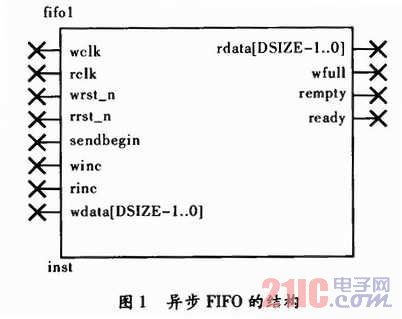

綜上所述,本文設(shè)計(jì)了如圖1所示的FIFO,,該FIFO的輸入端口有wclk(寫時(shí)鐘),,rclk(讀時(shí)鐘),,wrst_n(寫復(fù)位),,rrst_n(讀復(fù)位),sen-dbegin(啟動(dòng)數(shù)據(jù)發(fā)送,,由DSP發(fā)送給FPGA),,winc(寫使能),rinc(讀使能),,wdata[DSIZE-1..0](寫數(shù)據(jù),,以16位數(shù)據(jù)為例),輸出端口為rdata[DSIZE-1..0](讀數(shù)據(jù),,16位),,wfull(寫滿標(biāo)志),rempty(讀空標(biāo)志),,ready(數(shù)據(jù)準(zhǔn)備好,,由FPGA發(fā)送給DSP)。該FIFO的深度設(shè)為2 048,,即一共有2 048個(gè)16位數(shù)據(jù)存貯單元,,當(dāng)寫復(fù)位無效,寫使能有效時(shí),,F(xiàn)PGA就在寫時(shí)鐘的控制下將數(shù)據(jù)寫入FIFO中,,當(dāng)寫滿約定的字符數(shù)時(shí),,將數(shù)據(jù)準(zhǔn)備好信號(hào)置為有效,通知DSP可以取數(shù)據(jù),,當(dāng)FIFO寫滿情況出現(xiàn)時(shí),,寫滿標(biāo)志置為有效,阻止繼續(xù)向FIFO中寫入數(shù)據(jù),。當(dāng)FIFO接收到DSP發(fā)來的啟動(dòng)數(shù)據(jù)發(fā)送信號(hào)且讀使能信號(hào)均為有效時(shí),,F(xiàn)IFO就在DSP發(fā)來的讀時(shí)鐘的控制下,依次將數(shù)據(jù)放到16位讀數(shù)據(jù)端,,供DSP讀取,。

實(shí)現(xiàn)該FIFO的關(guān)鍵部分Verilog代碼如下:

需要說明的是,在產(chǎn)生寫滿標(biāo)志時(shí),,由于采用格雷碼,,寫滿標(biāo)志判斷的條件是:如果讀寫指針的最高兩位不同,其余位相同,,則為寫滿狀態(tài),。為了說明簡(jiǎn)便,以4位格雷碼表示深度為8的FIFO為例,,當(dāng)讀指針指向第7個(gè)地址時(shí),,讀指針為0100,此時(shí)若寫指針指向第8個(gè)地址,,則寫指針為1100,,此時(shí)兩者僅最高位不同而其余位相同,但此時(shí)FIFO并不是處于寫滿狀態(tài),,這與前文所敘述的用二進(jìn)制碼表示的讀寫指針判斷方法是有區(qū)別的,。當(dāng)寫操作寫滿一圈,第二次到達(dá)地址7時(shí),,此時(shí)的寫指針為1000,,可以看出,此時(shí)兩者的最高兩位不同,,而其余位相同,,這時(shí)FIFO真正處于寫滿狀態(tài)。

2 DSP端數(shù)據(jù)接收

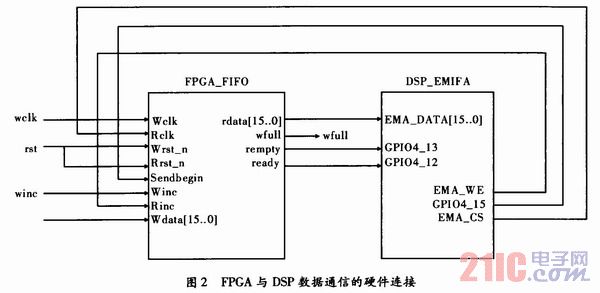

TI公司的TMS320C6000系列DSP均提供EMIFA接口,,本文利用EMIFA接口實(shí)現(xiàn)FPGA向DSP傳輸數(shù)據(jù),,實(shí)現(xiàn)兩者硬件連接的電路如圖2所示。

其中,,EMIFA的16位數(shù)據(jù)端與FIFO的Rdata端相連以便接收FPGA發(fā)來的數(shù)據(jù),,GPI04_13,GPI04_12,,GPI04_15這3個(gè)通用IO口用來接收或輸出相應(yīng)的握手信號(hào),。EMA_WE與FIFO的讀使能端相連,,EMA_CS與FIFO的讀時(shí)鐘相連。

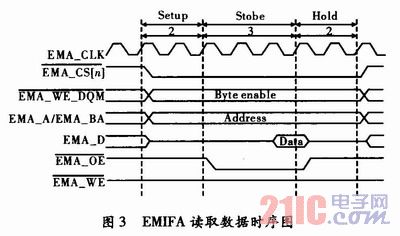

圖3所示為DSP的EMIFA口讀取數(shù)據(jù)的時(shí)序圖,,從圖中可以看出,,每一次讀數(shù)據(jù)操作均以EMA_CS(EMIFA使能信號(hào))下降沿開始,以EMA_CS的上升沿結(jié)束,。同時(shí),,因?yàn)槭亲x取操作,EMA_WE(EMA讀寫控制信號(hào),,低為寫,,高為讀)始終為高電平,EMA_OE(EMA輸出使能信號(hào),,低有效)在數(shù)據(jù)讀取時(shí)刻為低電平,。所以,將EMA_CS連至FIFO的Rclk端,,恰好實(shí)現(xiàn)DSP讀取一次數(shù)據(jù),,F(xiàn)IFO更新一個(gè)數(shù)據(jù),而EMA_WE可作為FIFO的讀使能信號(hào),。

3 仿真結(jié)果與結(jié)論

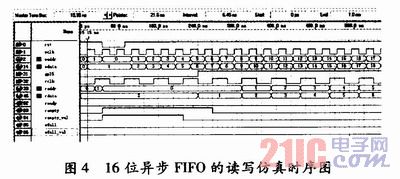

本文設(shè)計(jì)了數(shù)據(jù)寬度為16位,,深度為2 048的FIFO,并使用Verilog語言編寫了FIFO模塊和與DSP的接口模塊,,利用該FIFO,,F(xiàn)PGA實(shí)現(xiàn)了將數(shù)據(jù)1~65 535傳遞給DSP。在Quartus II軟件下進(jìn)行仿真得到的結(jié)果如圖4所示,。

由圖4可以看出,,在rst變?yōu)楦唠娖揭院?,F(xiàn)PGA在Wclk的上升沿依次將數(shù)據(jù)寫入FIFO中,,寫指針也從0開始逐次增1。在收到DSP發(fā)來的gp15(啟動(dòng)數(shù)據(jù)發(fā)送信號(hào))有效后,,在讀時(shí)鐘Rclk的上升沿,,F(xiàn)PGA將數(shù)據(jù)從1開始逐次輸出到Rada端,供DSP讀取,。DSP端在配置好EMIFA口后,,編寫的相應(yīng)接收程序,正確接收到了從0~65 535這65 536個(gè)數(shù)據(jù),。

為實(shí)現(xiàn)FPGA與DSP之間的數(shù)據(jù)通信,,本文提出了利用異步FIFO的方法,采用格雷碼和兩級(jí)D觸發(fā)器同步的方法降低了亞穩(wěn)態(tài)現(xiàn)象出現(xiàn)的概率,。同時(shí),,給出了FPGA和DSP實(shí)現(xiàn)數(shù)據(jù)通信的硬件連接電路,。經(jīng)驗(yàn)證,利用異步FIFO的方法,,能夠穩(wěn)定可靠地從FPGA中傳輸數(shù)據(jù)給DSP,。