引言

隨著信息技術的飛速發(fā)展,基于ARM在嵌入式系統方面的優(yōu)勢和CAN總線的廣泛應用,目前越來越多的ARM處理器內部自帶了CAN控制器,極大的方便了開發(fā)人員對CAN總線的開發(fā)。本課題是基于ARM2104的微處理器CAN總線系統節(jié)點開發(fā),采用CAN總線可以將節(jié)點控制器直接安裝在現場,數據經處理后發(fā)送到總線上,實現了信息的全數字方式傳輸,提高了傳輸的抗干擾能力,增加了信息的傳輸量。

總體設計方案

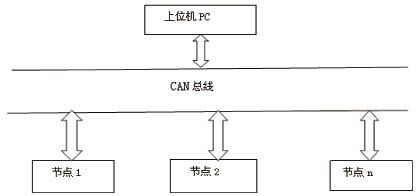

本課題中所設計的是CAN總線系統節(jié)點,系統節(jié)點結構圖如圖1。

圖1 系統節(jié)點結構圖

CAN總線系統應用要求:CAN總線接口的擴展、點對點通信。

CAN節(jié)點的設計主要是CAN通信控制器與微處理器之間、CAN總線收發(fā)器與物理總線之間的電路的設計。微控制器主要負責CAN控制器的初始化,進行與CAN控制器的數據傳遞,并按照預定的程序進行處理;CAN的通信協議主要由CAN控制器完成,CAN控制器主要負責將數據以CAN報文的形式傳遞,并進行系統的診斷、測試以及處理CAN總線上的錯誤等;而CAN總線收發(fā)器是CAN控制器和CAN總線之間的接口,完成物理電平的轉換,功能是增大通信距離,提高系統的瞬間抗干擾能力,保護總線,降低射頻干擾(RFI)。

通常一個完整的CAN節(jié)點應該包括三個部分:微控制器、CAN控制器、CAN收發(fā)器。目前廣泛流行的CAN總線器件有兩大類:一類是獨立的CAN控器,另一類是帶有在片CAN的微控制器。

CAN節(jié)點硬件電路設計

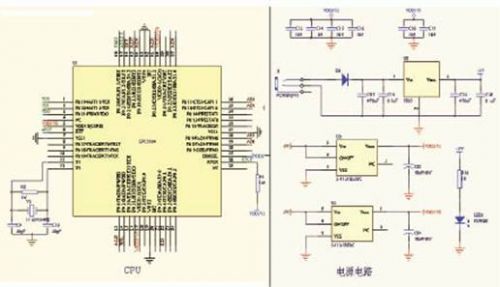

對于CAN節(jié)點硬件電路的的各接口電路的設計有:CAN接口電路、CPU模塊、外圍電路(復位電路和JATG接口電路)。其中CPU及電源電路如下圖2所示:

圖2 CPU及電源模塊

LPC2104要使用兩組電源,I/O供電電源為3.3V應用系統。首先,電源DW1將電源整流,經過C1、C3濾波,然后通過78M05將電源穩(wěn)壓至5V,再使用LDO芯片(低差壓電源芯片)穩(wěn)壓輸出3.3V及1.8V電壓。LD0芯片采用S-1131B33UC和S-1131B18UC,其特點為輸出電流大、精度高、穩(wěn)定性高、功耗低。

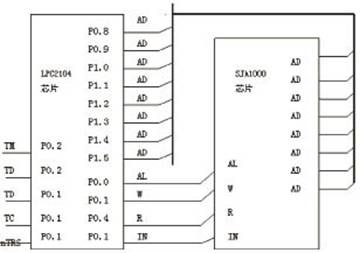

設計中的CPU芯片與控制器SJA1000的配腳圖如圖3所示。

圖3 模擬總線硬件圖

CAN節(jié)點的軟件設計

CAN節(jié)點的軟件設計主要包括ARM處理器的編程和SJA1000驅動程序的設計。在硬件電路確定以后,系統控制的主要功能將依賴于軟件來實現。系統能否正常可靠的工作,除了硬件的合理設計以外,與功能完善的軟件設計是分不開的。

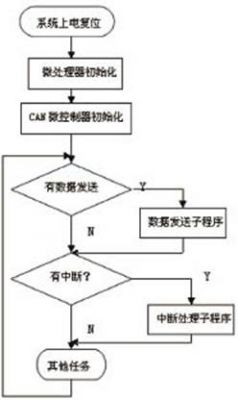

軟件程序流程圖如下圖4所示:

圖4 主程序流程圖

配置軟件包使用的GPIO必須在文件config.h中進行,其程序清單如列表1所示,其中程序清單(1)設置地址總線的寬度,只能為8、16、和24三個值之一。清單(2)設置信號AD0對應GPIO,其中0對應P0.0,1對應P0.1,以此類推。地址/數據總線的其它信號以這個信號為基準,順序定義。清單(3)信號ALE對應GPIO,其中0對應P0.0,1對應P0.1,以此類推。清單(4)信號WR對應GPIO,其中0對應P0.0,1對應P0.1,以此類推。

程序清單列表1 配置總線使用的GPIO

#define ADDR_N_BIT 16 (1)

#define AD0_PIN_NUM 8 (2)

#define ALE_PIN_NUM 0 (3)

#define WR_PIN_NUM 1 (4)

#define RD_PIN_NUM 4 (5)

#include“exbus.h” (6)

本系統CAN控制器采用SJA1000,SJA1000控制器在微控制器正常通訊前,都必須先在相應地址寄存器中加載,確定接收標識碼、總線接收波特率以及輸出控制等,這就是CAN控制器的初始化。系統所用的CAN總線控制器SJA1000和CAN2.0A以及CAN2.0B兩個版本的協議同時兼容。本系統設計以CAN2.0A的Basic CAN為協議標準進行設計。

測試之前編寫的程序前首先要確定SJA1000的片選地址,確定與其他外部存儲器無沖突。其次,微處理器對SJA1000的控制訪問是以外部存儲器的方式,來訪問SJA1000的內部寄存器,所以應該正確定義微處理器訪問SJA1000時,SJA1000內部寄存器的訪問地址。

整個流程進行測試之后,SJA1000有8個不同的中斷,這些中斷可使主控制器立即作用在CAN控制器的某些狀態(tài)上。一旦CAN產生中斷,SJA1000就將中斷輸出(管腳16)設為低電平,直到主控制器通過讀SJA1000的中斷寄存器對中斷采取相應措施,在主控制器響應后中斷,或接收INFO里有更多有效數據,SJA1000立刻將中斷輸出再次設為低電平。采用中斷接收的方式來接收數據,LPC2104的P0.16設置為外部中斷INT,整個數據接收模塊由數據接收函數void ReceiveData(uint8 *Rt)、中斷處理函數CANException(void)構成。當SJA1000接收到CAN總線數據,通過接收中斷使得LPC2104產生外部中斷INT而使其進入中斷處理函數,進而對接收到的數據進行處理。

可想,在CAN節(jié)點的軟件設計的整個流程中,當硬件電路確定以后,系統控制的主要功能將依賴于軟件來實現,并且能夠正常可靠的工作。

結論

以ARM芯片作為主控制器,CAN總線作為數據傳輸方式來進行通訊的嵌入式系統得到了越來越廣泛的應用。同時CAN通訊的可靠性也成為影響系統性能的關鍵部分之一。

本文以LPC2104為例,給出了一類微處理器與CAN控制器SJA1000之間的較為通用的硬件連接方法,對CAN總線節(jié)點進行了可靠性設計,采用CAN總線可以將節(jié)點控制器直接安裝在現場,數據經處理后發(fā)送到總線上,實現了信息的全數字方式傳輸,提高了傳輸的抗干擾能力,增加了信息的傳輸量。

該設計現已在工廠車間中的車身控制系統中得到了應用,且運行可靠。