降低任何嵌入式設(shè)計(jì)的體積和成本的常用方法是使用具有較少I/O引腳的通信總線。雖然從并行總線發(fā)展到串行總線可明顯減小體積和降低成本,但是從一種串行總線發(fā)展為另一種具有較少引腳的串行總線也很有用。用串行總線替代并行總線時(shí),傳輸速度是一個(gè)關(guān)鍵參數(shù)。在小體積是最重要參數(shù)的設(shè)計(jì)中,使用具有較少引腳的串行總線很有優(yōu)勢(shì)。單片機(jī)集成超過(guò)12種不同的串行接口,本文將討論各串行接口的優(yōu)缺點(diǎn)。

個(gè)人計(jì)算機(jī)中的USB與FireWireTM

一種促使PC市場(chǎng)發(fā)生重大變化的流行總線就是通用串行總線(universal serial bus,USB)。它的高速度、低引腳數(shù)和多功能性促進(jìn)了它的廣泛使用,且USB逐漸取代了并行打印機(jī)和RS-232串口,成為PC的主要通信端口。USB2.0在節(jié)約系統(tǒng)成本方面也優(yōu)于FireWireTM S400。此外,USB可利用PC資源依靠主處理器來(lái)管理低級(jí)別的USB協(xié)議,而FireWire將此任務(wù)委托給接口硬件。FireWire所需的額外硬件成本和初始許可費(fèi)用使USB成為PC領(lǐng)域的首選接口。同樣的原因也促使嵌入式應(yīng)用紛紛迅速采用USB。

同步接口與異步接口

選擇串行接口時(shí),必須檢查同步接口和異步接口。同步接口使用主時(shí)鐘進(jìn)行同步,而異步接口將時(shí)鐘嵌入到數(shù)據(jù)流中。從器件時(shí)鐘的頻率變化不會(huì)影響同步接口的同步操作,因而可以使用低成本振蕩器。在異步器件中,實(shí)現(xiàn)同步需要所有器件在傳輸速度、協(xié)議、重新同步頻率和時(shí)鐘穩(wěn)定性方面達(dá)成一致。

同步接口可在同一印刷電路板(printed circuit board,PCB)上輕松實(shí)現(xiàn)器件間連接,而異步接口旨在通過(guò)電纜連接相隔數(shù)米至1000米的系統(tǒng)。應(yīng)用范圍從簡(jiǎn)單的點(diǎn)對(duì)點(diǎn)連接到具有數(shù)百個(gè)器件的復(fù)雜網(wǎng)絡(luò)。也可以通過(guò)OSI模型描述每種總線類型的不同物理接口。

OSI七層模型

通常,同步接口在內(nèi)部支持?jǐn)?shù)據(jù)鏈路層(第2層)和物理層(第1層),而大部分異步接口在內(nèi)部支持?jǐn)?shù)據(jù)鏈路層在外部支持物理層。有時(shí),異步接口也在內(nèi)部支持這兩層。對(duì)于某些應(yīng)用,相同的數(shù)據(jù)鏈路層結(jié)合不同的物理層驅(qū)動(dòng)程序來(lái)創(chuàng)建不同的接口標(biāo)準(zhǔn)。在單片機(jī)中,通常通過(guò)某些硬件支持在軟件中實(shí)現(xiàn)第3至第7層。

從并行接口發(fā)展到串行接口

當(dāng)系統(tǒng)軟件需要大量存儲(chǔ)器時(shí),通常會(huì)選擇具有外部地址和數(shù)據(jù)總線的單片機(jī)。并行閃存程序存儲(chǔ)器和SRAM需要16個(gè)或更多I/O引腳,設(shè)計(jì)人員可選擇使用具有內(nèi)部存儲(chǔ)器的單片機(jī)以節(jié)省I/O引腳、縮小體積和降低成本。雖然現(xiàn)在許多單片機(jī)程序存儲(chǔ)器的容量都已有所提高,但如果內(nèi)部存儲(chǔ)容量還是不夠的話,可采用使用SPI端口的外部閃存程序存儲(chǔ)器或串行SRAM。

由于串行閃存程序存儲(chǔ)器和串行SRAM器件只可通過(guò)SPI總線提供,所以選擇此總線可獲得最高效的系統(tǒng)設(shè)計(jì)。當(dāng)某些元件只能通過(guò)某個(gè)特定總線連接時(shí),這些元件決定了總線的選擇,除非單線器件可提供更好的解決方案。

同步接口

• SPI

• MICROWIRE

• I2C™

• 通用串行異步收發(fā)器(universal serial asynchronous receiver transmitter,USART),同步和異步模式

總線選擇所采用的標(biāo)準(zhǔn):

1.元件只能通過(guò)一種總線提供

2. MCU上可用的總線:

a. SPI和I2C或同步串行端口(Synchronous Serial Port,SSP)

b.串行控制接口(SCI)

c. USART

d.具有軟件驅(qū)動(dòng)的GPI/O

e.其他網(wǎng)絡(luò)總線

3.需要較快的總線速度

4.小尺寸的較低引腳數(shù)總線

5.推挽輸出或漏極開路輸出

6.系統(tǒng)總成本

7.提供的功能集

SPI總線支持的典型速度范圍為5MHz至20MHz,但對(duì)于高速串行閃存程序存儲(chǔ)器,還可支持高達(dá)75MHz的速度。Microwire總線在工作原理和連線數(shù)量上與SPI總線相似,但是總線規(guī)范將其通信速度限制為3MHz。

I2C總線具有時(shí)鐘線和數(shù)據(jù)線,其可軟件尋址且具有400kHz的典型工作速度,連接多個(gè)器件時(shí)速度可為1MHz。由于單片機(jī)I/O端口有限,故端口較少成為了該總線的最大優(yōu)勢(shì)。

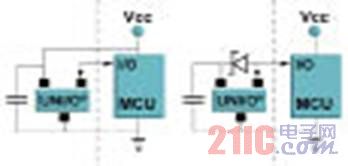

圖1a 3引腳UNI/O總線連接 圖1b 2引腳UNI/O總線連接

通常,SPI和Microwire總線使用4個(gè)I/O端口,而I2C總線使用2個(gè)I/O端口。小型化系統(tǒng)的下一步發(fā)展就是尋求更小的、使用單個(gè)I/O進(jìn)行通信的總線。由于這種情況只能在將時(shí)鐘嵌入到數(shù)據(jù)流中時(shí)實(shí)現(xiàn),所以這些接口必須是異步接口。

異步接口

今天,有兩種不同的異步總線競(jìng)爭(zhēng)通常為同步總線預(yù)留的端口。這兩種總線是1-Wire®總線(Maxim)和UNI/O®總線(Microchip Technology)。

1-Wire®總線上的器件采用2引腳封裝,一個(gè)引腳用于接地,第二個(gè)引腳用于數(shù)據(jù)和電源連接。在1-Wire總線器件的設(shè)計(jì)中融入了電容,從而可從數(shù)據(jù)線獲取寄生功率,采用漏極開路輸出的電阻可獲取高達(dá)16.3kbps的傳輸速度,而當(dāng)該電阻值降至2.2kΩ時(shí)傳輸速度將增至142kbps。

UNI/O®總線是一種新的單線總線標(biāo)準(zhǔn),采用3引腳封裝,支持電源、地和數(shù)據(jù)連接。使用曼徹斯特編碼進(jìn)行通信,支持10kbps至100kbps的數(shù)據(jù)傳輸速度。雖然該總線旨在用于標(biāo)準(zhǔn)嵌入式設(shè)計(jì),但通過(guò)添加一個(gè)外部肖特基二極管并調(diào)整旁路電容的值,可使其用于具有2引腳接口的應(yīng)用中。圖1a和1b中的框圖充分說(shuō)明了此解決方案如此簡(jiǎn)單。

UART為最早且占據(jù)主導(dǎo)地位的異步接口,而在需要同步和異步模式時(shí)還稱為USART。再回到OSI模型,單片機(jī)的片內(nèi)UART實(shí)現(xiàn)了數(shù)據(jù)鏈路層,而物理層受制于幾個(gè)驅(qū)動(dòng)標(biāo)準(zhǔn)。這些標(biāo)準(zhǔn)中最常用的是RS-232C、RS-422和RS-485接口。

還有一些具有異步接口的特殊單片機(jī),旨在用于網(wǎng)絡(luò)連接,如以太網(wǎng)、CAN、LIN和MIDI。表1匯總了各種串行接口及其特性。

表1:各種串行接口匯總

結(jié)論

在選擇最佳的串行接口時(shí),應(yīng)檢查系統(tǒng)設(shè)計(jì)以獲得最低成本解決方案。許多情況下,最低成本的元件并不會(huì)提供最低成本的系統(tǒng)。隨著系統(tǒng)規(guī)模的繼續(xù)縮小,單線總線外部存儲(chǔ)器可以在對(duì)單片機(jī)資源或外部連接器產(chǎn)生較小影響的情況下提供最低的系統(tǒng)總成本。