EDA技術(shù)是以計(jì)算機(jī)為工具完成數(shù)字系統(tǒng)的邏輯綜合、布局布線和設(shè)計(jì)仿真等工作。電路設(shè)計(jì)者只需要完成對系統(tǒng)功能的描述,就可以由計(jì)算機(jī)軟件進(jìn)行系統(tǒng)處理,最后得到設(shè)計(jì)結(jié)果,并且修改設(shè)計(jì)方案如同修改軟件一樣方便。利用EDA工具可以極大地提高設(shè)計(jì)效率。

利用硬件描述語言編程來表示邏輯器件及系統(tǒng)硬件的功能和行為,是EDA設(shè)計(jì)方法的一個重要特征。VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成電路硬件描述語言)是硬件描述語言的一種,對系統(tǒng)硬件的描述功能很強(qiáng)而語法又比較簡單。VHDL具有強(qiáng)大的行為描述能力,設(shè)計(jì)者可以不懂硬件的結(jié)構(gòu),只需集中精力進(jìn)行電子系統(tǒng)的設(shè)計(jì)和性能優(yōu)化;具有方便的邏輯仿真與調(diào)試功能,在設(shè)計(jì)早期就能查驗(yàn)系統(tǒng)的功能,方便地比較各種方案的可行性及其優(yōu)劣。目前,VHDL作為IEEE的工業(yè)標(biāo)準(zhǔn)硬件描述語言,得到眾多EDA公司的支持,在電子工程領(lǐng)域已經(jīng)成為事實(shí)上通用硬件描述語言。

本文采用VHDL作為工具描述了自動售貨機(jī)控制模塊的邏輯控制電路,并在FPGA上實(shí)現(xiàn)。該自動售貨機(jī)能夠根據(jù)投入硬幣額度,按預(yù)定的要求在投入硬幣大于規(guī)定值時送出飲料并找零。

設(shè)計(jì)方案

本文所設(shè)計(jì)的簡易自動售貨機(jī)可銷售礦泉水,假設(shè)每瓶1.5元。設(shè)兩個投幣孔,分別接收1元和5角兩種硬幣,兩個輸出口,分別輸出購買的商品和找零。假設(shè)每次只能投入一枚1元或5角硬幣,投入1元5角硬幣后機(jī)器自動給出一瓶礦泉水;投入2元硬幣后,在給出一瓶礦泉水的同時找回一枚5角的硬幣。另外設(shè)置一復(fù)位按鈕,當(dāng)復(fù)位按鈕按下時,自動售貨機(jī)回到初始狀態(tài)。

開發(fā)軟件選用功能強(qiáng)大的Altera公司的最新可編程邏輯器件開發(fā)工具Quartus II 8.0,實(shí)現(xiàn)芯片選用Altera公司FLEX10K系列的EPF10K10LC84-4;首先在計(jì)算機(jī)上完成程序設(shè)計(jì)、編譯及時序仿真,然后將經(jīng)過驗(yàn)證的設(shè)計(jì)文件下載到選擇的可編程邏輯器件中,并在電子設(shè)計(jì)自動化實(shí)驗(yàn)系統(tǒng)中進(jìn)行硬件模擬和測試。

狀態(tài)機(jī)VHDL程序設(shè)計(jì)

有限狀態(tài)機(jī)FSM(Finite State Machine)及其設(shè)計(jì)技術(shù)是實(shí)用數(shù)字系統(tǒng)設(shè)計(jì)中實(shí)現(xiàn)高效率、高可靠邏輯控制的重要途徑。傳統(tǒng)的狀態(tài)機(jī)設(shè)計(jì)方法需進(jìn)行繁瑣的狀態(tài)分配、繪制狀態(tài)表、簡化次態(tài)方程等,而利用VHDL可以避免這些煩瑣的過程,直接利用狀態(tài)轉(zhuǎn)換圖進(jìn)行狀態(tài)機(jī)的描述。此外,與VHDL的其他描述方式相比,狀態(tài)機(jī)的VHDL表述豐富多樣,程序?qū)哟畏置鳎Y(jié)構(gòu)清晰,易讀易懂;在排錯、修改和模塊移植方面也有其獨(dú)到的特點(diǎn)。

狀態(tài)機(jī)有摩爾(Moore)型和米立(Mealy)型兩種。Moore型狀態(tài)機(jī)的輸出信號只與當(dāng)前狀態(tài)有關(guān);Mealy型狀態(tài)機(jī)的輸出信號不僅與當(dāng)前狀態(tài)有關(guān),還與輸入信號有關(guān)。結(jié)合本文設(shè)計(jì),由于輸出僅與狀態(tài)有關(guān),選用了Moore型狀態(tài)機(jī)設(shè)計(jì)自動售貨機(jī)控制模塊,狀態(tài)轉(zhuǎn)換圖如圖1所示。

圖1 自動售貨機(jī)狀態(tài)轉(zhuǎn)換圖

1)狀態(tài)定義:S0表示初態(tài),S1表示投入5角硬幣,S2表示投入1元硬幣,S3表示投入1元5角硬幣,S4表示投入2元硬幣。

2)輸入信號:取投幣信號為輸入邏輯變量,用兩位的矢量state_inputs表示。state_inputs(0)表示投入1元硬幣,state_inputs(1)表示投入5角硬幣。輸入信號為1表示投入硬幣,輸入信號為0表示未投入硬幣。

3)輸出信號:給出礦泉水和找零為兩個輸出變量,用兩位的矢量comb_outputs表示。comb_outputs(0)表示輸出貨物,comb_outputs(1)表示找5角零錢。輸出信號為1表示輸出貨物或找零,輸出信號為0表示不輸出貨物或不找零。

根據(jù)圖1所示的狀態(tài)轉(zhuǎn)換圖,用VHDL中的CASE_WHEN結(jié)構(gòu)和IF_THEN_ELSE語句實(shí)現(xiàn)控制功能,源程序如下:

LIBRARY IEEE; --庫和程序包的使用說明

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY sellmachine IS --實(shí)體定義

PORT(clk,reset: IN std_logic;

state_inputs:IN std_logic_vector(0 TO 1);

comb_outputs:OUT std_logic_vector(0 TO 1));

END sellmachine;

ARCHITECTURE state OF sellmachine IS --結(jié)構(gòu)體

TYPE fsm_st IS (S0,S1,S2,S3,S4); --狀態(tài)枚舉類型定義

SIGNAL current_state,next_state:fsm_st; --狀態(tài)信號的定義

BEGIN

reg:PROCESS(reset,clk) --時序進(jìn)程

BEGIN

IF reset='1' THEN current_state<=S0; --異步復(fù)位

ELSIF rising_edge(clk) THEN

current_state<=next_state; --狀態(tài)轉(zhuǎn)換

END IF;

END PROCESS;

corn:PROCESS(current_state,state_inputs) --組合進(jìn)程

BEGIN

CASE current_state IS

WHEN S0=>comb_outputs<="00"; --現(xiàn)態(tài)S0

IF state_inputs<="00" THEN next_state<=S0; --輸入不同,次態(tài)不同

ELSIF state_inputs<="01" THEN next_state<=S1;

ELSIF state_inputs<="10" THEN next_state<=S2;

END IF;

WHEN S1=>comb_outputs<="00"; --現(xiàn)態(tài)S1

IF state_inputs<="00" THEN next_state<=S1; --輸入不同,次態(tài)不同

ELSIF state_inputs<="01" THEN next_state<=S2;

ELSIF state_inputs<="10" THEN next_state<=S3;

END IF;

WHEN S2=>comb_outputs<="00"; --現(xiàn)態(tài)S2

IF state_inputs<="00" THEN next_state<=S2; --輸入不同,次態(tài)不同

ELSIF state_inputs<="01" THEN next_state<=S3;

ELSIF state_inputs<="10" THEN next_state<=S4;

END IF;

WHEN S3=>comb_outputs<="10"; --現(xiàn)態(tài)S3

IF state_inputs<="00" THEN next_state<=S0; --輸入不同,次態(tài)不同

ELSIF state_inputs<="01" THEN next_state<=S1;

ELSIF state_inputs<="10" THEN next_state<=S2;

END IF;

WHEN S4=>comb_outputs<="11"; --現(xiàn)態(tài)S4

IF state_inputs<="00" THEN next_state<=S0; --輸入不同,次態(tài)不同

ELSIF state_inputs<="01" THEN next_state<=S1;

ELSIF state_inputs<="10" THEN next_state<=S2;

END IF;

END CASE;

END PROCESS;

END state;

編譯、仿真及FPGA實(shí)現(xiàn)

在Altera公司的可編程邏輯器件集成開發(fā)平臺Quartus II 8.0下完成程序的編輯、編譯并進(jìn)行時序仿真。

1)編譯:編譯是EDA設(shè)計(jì)中的核心環(huán)節(jié)。軟件將對設(shè)計(jì)輸入文件進(jìn)行邏輯化簡、綜合和優(yōu)化, 適當(dāng)?shù)赜靡黄蚨嗥骷M(jìn)行適配,最后產(chǎn)生編程用的編程文件。主要包括設(shè)計(jì)編譯和檢查、邏輯優(yōu)化和綜合、適配和分割、布局和布線、生成編程數(shù)據(jù)文件等過程。自動售貨機(jī)控制模塊VHDL文件編譯報(bào)告如圖2所示。

圖2 編譯報(bào)告

報(bào)告中給出了進(jìn)行編譯的時間、采用的開發(fā)軟件的版本、頂層設(shè)計(jì)實(shí)體名、選用器件的系列和型號、時序分析情況、占用資源情況及引腳使用情況等信息。

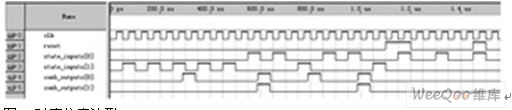

2)時序仿真:編譯后對系統(tǒng)和各模塊進(jìn)行時序仿真,分析其時序關(guān)系,估計(jì)設(shè)計(jì)的性能及檢查和消除競爭冒險是非常有必要的。仿真前,先利用波形編輯器建立波形文件,仿真結(jié)果將會生成報(bào)告文件和輸出信號波形,從中便可以觀察到各個節(jié)點(diǎn)的信號變化。若發(fā)現(xiàn)錯誤,則返回設(shè)計(jì)輸入中修改設(shè)計(jì)邏輯。自動售貨機(jī)控制模塊仿真波形如圖3所示。

圖3 時序仿真波形

3) FPGA實(shí)現(xiàn):將編譯階段生成的編程數(shù)據(jù)文件通過Quartus II 下載到芯片EPF10K10LC84-4中,并在電子設(shè)計(jì)自動化實(shí)驗(yàn)系統(tǒng)中進(jìn)行測試得到了正確的結(jié)果。