1引言

激光告警機(jī)" title="激光告警機(jī)">激光告警機(jī)是被動(dòng)光電偵查設(shè)備,其功能是探測(cè)目標(biāo)激光信號(hào)的性質(zhì),如波長(zhǎng)、方位等,本系統(tǒng)能夠完成探測(cè)并提取激光波長(zhǎng)信息的功能。在激光波長(zhǎng)測(cè)量系統(tǒng)中,激光信號(hào)從CCD相機(jī)輸出到信號(hào)處理器的時(shí)間和處理器的處理時(shí)間是能否做到實(shí)時(shí)監(jiān)測(cè)激光波長(zhǎng)的兩大關(guān)鍵,即使采用高速單片機(jī)也限于它的串行處理模式和較長(zhǎng)的取指時(shí)間,無(wú)法滿足實(shí)時(shí)測(cè)量的目的,因此為實(shí)現(xiàn)在幾毫秒內(nèi)就對(duì)目標(biāo)激光信號(hào)的波長(zhǎng)做出反應(yīng)只能寄希望于高性能的DSP器件或FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA器件了。告警系統(tǒng)中,相機(jī)的接口為器件的選擇則也提出要求:采集器件要支持LVDS 電平,否則要加入電平轉(zhuǎn)換芯片,這勢(shì)必會(huì)帶來數(shù)據(jù)傳輸?shù)难訒r(shí);此外應(yīng)用FFT進(jìn)行數(shù)據(jù)處理時(shí),由于FFT在算法上具有可重復(fù)性和可并行處理的特點(diǎn),為實(shí)現(xiàn)實(shí)時(shí)性處理,要求選擇具有并行處理功能的處理器。在設(shè)計(jì)中選用Xilinx公司的Sp3系列FPGA作為控制、處理器,將FPGA用在本系統(tǒng)中的好處有: (1)高密度FPGA可在一塊片子上實(shí)現(xiàn)多個(gè)子模塊,有效減小激光告警接收機(jī)的體積;(2)FPGA具有成熟的時(shí)鐘管理體系,和精確的時(shí)鐘控制體系,能夠?qū)崿F(xiàn)采集與處理的無(wú)縫連接,從而提高系統(tǒng)可靠性;(3)FPGA支持多種信號(hào)標(biāo)準(zhǔn),尤其在告警系統(tǒng)中FPGA可將接口設(shè)置為L(zhǎng)VDS型,使得FPGA與相機(jī)的通信更加直接,避免了以往采用電平轉(zhuǎn)換芯片的相關(guān)工作;(4)FPGA具有并行處理功能,能夠?qū)崿F(xiàn)流水作業(yè),可減少信號(hào)處理時(shí)進(jìn)行FFT運(yùn)算的時(shí)間。

2原理概述

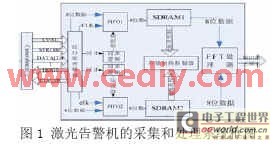

相機(jī)將探測(cè)到的激光信號(hào)通過Cameralink接口方式傳遞給FPGA,F(xiàn)PGA控制時(shí)序產(chǎn)生來完成以下工作:向CCD輸入時(shí)鐘信號(hào);通過觸發(fā)端設(shè)置 CCD積分時(shí)間;倍頻相機(jī)的STROBE信號(hào)實(shí)現(xiàn)接收數(shù)據(jù)的串并轉(zhuǎn)換;將并行數(shù)據(jù)在讀使能的控制下從FIFO中轉(zhuǎn)入塊RAM。為提高激光告警機(jī)的響應(yīng)時(shí)間該系統(tǒng)充分利用FPGA可流水作業(yè)這一功能,在數(shù)據(jù)接收端提供兩個(gè)1024個(gè)單元的數(shù)據(jù)存儲(chǔ)器交替工作,通過在軟件上設(shè)立標(biāo)志位來實(shí)現(xiàn)對(duì)存儲(chǔ)區(qū)間進(jìn)行切換。在數(shù)據(jù)存儲(chǔ)和數(shù)據(jù)處理時(shí),當(dāng)FPGA用1 區(qū)進(jìn)行采集數(shù)據(jù)的第i幀時(shí),同時(shí)2 區(qū)進(jìn)行第i-1幀數(shù)據(jù)的處理,當(dāng)兩者同時(shí)結(jié)束后,接著又用2 區(qū)進(jìn)行第i+1幀數(shù)據(jù)的采集, 同時(shí)1 區(qū)進(jìn)行第i 幀數(shù)據(jù)的處理, 這樣交替工作,形成流水線作業(yè)。由于相機(jī)采集速率和塊RAM寫入時(shí)間的不同,在FPGA內(nèi)部采用IP" title="IP">IP 核生成兩個(gè)FIFO為兩路數(shù)據(jù)的接收實(shí)現(xiàn)緩沖來取得同步。塊RAM的寫入、讀出時(shí)序和地址發(fā)生器由VHDL語(yǔ)言編寫完成。數(shù)據(jù)的處理通過在時(shí)鐘的同步下逐一讀取RAM中的數(shù)據(jù),采用十級(jí)流水基-2算法實(shí)現(xiàn)1024點(diǎn)的快速傅里葉變換,得出輸入激光信號(hào)的頻譜特性。激光告警機(jī)的采集和處理系統(tǒng)框圖如圖1所示。

3系統(tǒng)設(shè)計(jì)

整個(gè)系統(tǒng)由兩部分構(gòu)成:數(shù)據(jù)采集模塊,數(shù)據(jù)處理模塊。

3.1 CCD相機(jī)數(shù)據(jù)采集模塊

在設(shè)計(jì)中采用ATMEl公司的AViiVA M2 CL相機(jī),該相機(jī)采用Cameralink接口,Cameralink技術(shù)的核心是美國(guó)NS(National Semiconductor)提出的一種高速數(shù)據(jù)傳輸方法—Channel Link技術(shù),該技術(shù)主要用于數(shù)字圖像數(shù)據(jù)的高速傳輸,采用LVDS信號(hào)模式,LVDS低電壓擺幅差分模式具有高速傳輸數(shù)據(jù)時(shí)交叉干擾小、EMI 干擾小等優(yōu)點(diǎn),最高傳輸率可達(dá)2.38Gb/s。該相機(jī)的接口定義為:四對(duì)LVDS線,用來做FPGA對(duì)相機(jī)的控制;兩對(duì)LVDS線,用于相機(jī)和FPGA 之間的通信,速度可達(dá)9600波特率;四對(duì)LVDS線,用于輸出數(shù)據(jù)和數(shù)據(jù)的位同步、幀同步信號(hào)。選用XC3S400型的FPGA,它具有豐富的接口標(biāo)準(zhǔn)尤其是支持LVDS 信號(hào)標(biāo)準(zhǔn),可與Cameralink接口的相機(jī)直接連接。相機(jī)工作方式的設(shè)置由FPGA基于RS-232協(xié)議串行通信來實(shí)現(xiàn),采用全雙工,沒有握手信號(hào)的異步串行方式,波特率固定在9600Hz,每幀數(shù)據(jù)由一個(gè)起始位,8個(gè)數(shù)據(jù)位,一個(gè)停止位組成。相機(jī)的積分時(shí)間和輸出增益都是可以根據(jù)需要設(shè)置為不同的值。對(duì)于相機(jī)工作的觸發(fā)方式由FPGA外部觸發(fā),做到FPGA與相機(jī)共用同一個(gè)全局時(shí)鐘。

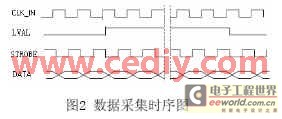

在數(shù)據(jù)的采集過程中,數(shù)據(jù)傳送的同步信號(hào)由 STROBE引腳產(chǎn)生,當(dāng)數(shù)據(jù)在一個(gè)數(shù)據(jù)區(qū)存滿時(shí),通過LVAL引腳通知FPGA 轉(zhuǎn)到另一數(shù)據(jù)存儲(chǔ)區(qū)。圖2 給出了數(shù)據(jù)采集的時(shí)序圖。其中CLK_IN是由FPGA的內(nèi)核數(shù)字時(shí)鐘管理模塊DCM 來實(shí)現(xiàn)倍頻得到。在時(shí)鐘控制和管理方面DCM比DLL功能更強(qiáng)大,使用更靈活。DCM的主要功能包括消除時(shí)鐘時(shí)延、頻率綜合和時(shí)鐘相位的調(diào)整。在本設(shè)計(jì)中對(duì)輸入時(shí)鐘STROBE作8倍頻處理,以實(shí)現(xiàn)數(shù)據(jù)一轉(zhuǎn)八串并轉(zhuǎn)換的鎖存輸出。

高速采集程序的設(shè)計(jì)主要有接口匹配、采集狀態(tài)機(jī)和數(shù)據(jù)存儲(chǔ)三部分。在接口匹配中由于LVDS 的輸入與輸出都是內(nèi)匹配的,所以LVDS 間可直接連接。在FPGA 內(nèi),需對(duì)差分輸入時(shí)鐘緩沖器(IBUFDS)、差分輸入的全局時(shí)鐘緩沖器(IBUFGDS)和差分輸出時(shí)鐘緩沖器(OBUFDS) 例化。

FPGA 的部分代碼如下:

component IBUFDS - - 差分輸入時(shí)鐘緩沖器( IBUFDS)

port (O : out STD_ULOGIC;

I : in STD_ULOGIC;

IB : in STD_ULOGIC) ;

end component ;

IBUFDS_INSTANCE_NAME: IBUFDS

port map (O=>user_O,I=> user_I,IB =>user_IB) ;

3.2數(shù)據(jù)處理模塊

Spartan3系列FPGA有豐富的乘法器資源,在不使用任何優(yōu)化算法的情況下每一個(gè)蝶形運(yùn)算需要4個(gè)實(shí)數(shù)乘法器,因此在FPGA中每個(gè)蝶形運(yùn)算可以用 4個(gè)乘法器在一個(gè)時(shí)鐘周期內(nèi)完成。豐富的RAM資源便于實(shí)現(xiàn)數(shù)據(jù)的流水操作,即對(duì)于輸入、輸出數(shù)據(jù)以及中間變量可以開辟不同的存儲(chǔ)區(qū),例如當(dāng)計(jì)算第i組數(shù)據(jù)時(shí),第i-1組計(jì)算結(jié)果正在輸出,第i+1組數(shù)據(jù)正在輸入。

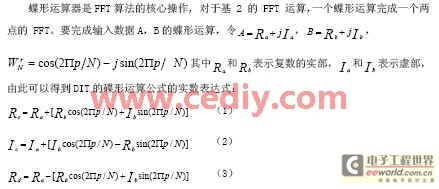

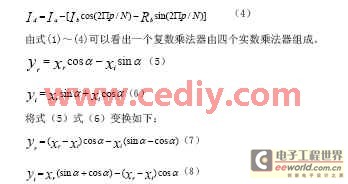

由于在FFT運(yùn)算中必然產(chǎn)生復(fù)數(shù),因此為使計(jì)算方便,在設(shè)計(jì)之初就將FFT變換器的數(shù)據(jù)輸入口分為實(shí)數(shù)和虛數(shù)。1024點(diǎn)復(fù)數(shù)FFT運(yùn)算,按照基-2頻率抽取運(yùn)算分成10級(jí),每級(jí)包括1個(gè)雙端RAM,1個(gè)地址發(fā)生器,一個(gè)ROM用于存儲(chǔ)旋轉(zhuǎn)因子表,1個(gè)蝶形運(yùn)算單元,2個(gè)選擇緩沖單元。為了簡(jiǎn)化地址單元電路,將復(fù)數(shù)數(shù)據(jù)的實(shí)部虛部組合成一個(gè)數(shù)據(jù)存儲(chǔ)在RAM中。由于使用雙口RAM ,當(dāng)一個(gè)存儲(chǔ)單元中的數(shù)據(jù)讀出做運(yùn)算時(shí),該存儲(chǔ)單元就能夠存儲(chǔ)上一級(jí)來的數(shù)據(jù),因此這種結(jié)構(gòu)的FFT 可以進(jìn)行流水線操作,能夠?qū)π盘?hào)樣本進(jìn)行實(shí)時(shí)連續(xù)的運(yùn)算。選擇緩沖器的用途是拉齊數(shù)據(jù),將RAM 輸出的2個(gè)復(fù)數(shù)數(shù)據(jù)拆成4個(gè)實(shí)數(shù)數(shù)據(jù)輸入到蝶形運(yùn)算單元,完成蝶形運(yùn)算后的數(shù)據(jù)進(jìn)入選擇緩沖器組合成2個(gè)復(fù)數(shù)數(shù)據(jù)輸出。

可見復(fù)數(shù)乘法需要的實(shí)數(shù)乘法由原來的4個(gè)變?yōu)?個(gè),式中 因子可作為常數(shù)存入ROM,這樣復(fù)數(shù)乘法只需3個(gè)實(shí)數(shù)乘法3個(gè)實(shí)數(shù)加法就可完成。由上述算法編程得到的蝶形變換器經(jīng)綜合后生成的原理圖如圖3所示。原理圖中clk是時(shí)鐘輸入引腳;X_re,X_im,Y_re,Y_im分別是復(fù)數(shù)X,Y的實(shí)部和虛部;Cin代表 ;cms和cps分別表示 和 ;out1_re,out1_im,out2_re,out2_im代表蝶形變換后兩個(gè)輸出數(shù)據(jù)的實(shí)部和虛部。

地址產(chǎn)生及控制單元對(duì)整個(gè)參與FFT運(yùn)算的數(shù)據(jù)的存儲(chǔ)、讀寫時(shí)序進(jìn)行控制,是 FFT 運(yùn)算器的重要組成部分。地址產(chǎn)生及控制單元將要產(chǎn)生每一階運(yùn)算單元輸入數(shù)據(jù)的讀寫地址、存儲(chǔ)器的讀寫、使能等控制信號(hào),同時(shí)還要產(chǎn)生旋轉(zhuǎn)因子系數(shù)的讀出地址,將配對(duì)的數(shù)據(jù)和旋轉(zhuǎn)因子系數(shù)按序送入蝶形運(yùn)算單元,從而實(shí)現(xiàn)每一階的蝶形運(yùn)算。地址產(chǎn)生及控制單元的設(shè)計(jì)方法主要是利用有限狀態(tài)機(jī)進(jìn)行設(shè)計(jì)。針對(duì)每一階運(yùn)算單元的運(yùn)算過程劃分成不同的狀態(tài),不同的狀態(tài)下輸出不同的數(shù)據(jù)地址和控制信號(hào)。

表1列出了計(jì)算一幀1024點(diǎn)FFT占用FPGA內(nèi)部資源的情況。經(jīng)后仿真時(shí)序分析,該激光告警系統(tǒng)在系統(tǒng)時(shí)鐘為50MHz的情況下,完成一幀1024點(diǎn) FFT只需110μs,加上數(shù)據(jù)載入時(shí)間和數(shù)據(jù)讀取時(shí)間只需230μs,滿足實(shí)時(shí)處理的要求。從表中可以看出, FFT子模塊完成后, FPGA還有大量資源可以利用,因此剩余資源可用于采集模塊,從而在一塊芯片上完成多種功能,有效減少了激光告警機(jī)的體積。

在信號(hào)處理前直接對(duì)FPGA的輸入信號(hào)用Matlab仿真的頻譜如圖4,可見激光信號(hào)的波長(zhǎng)峰值在523nm附近,數(shù)據(jù)在FPGA中進(jìn)行FFT之后輸出的數(shù)據(jù)經(jīng)過倒序后得到的頻譜結(jié)果如圖5,對(duì)比兩圖可知FPGA輸出與Matlab仿真結(jié)果基本相同,從而驗(yàn)證了告警系統(tǒng)的正確性。

4 總結(jié)

本文介紹了為激光告警機(jī)探測(cè)目標(biāo)激光的波長(zhǎng)所開發(fā)的CCD相機(jī)信號(hào)采集與快速處理系統(tǒng)設(shè)備的設(shè)計(jì)。該系統(tǒng)利用FPGA實(shí)現(xiàn)對(duì)Atmel公司的AViiVA M2 CL型線陣CCD相機(jī)輸出數(shù)據(jù)的采集與處理,電路簡(jiǎn)單,可靠性強(qiáng),充分利用了FPGA支持多信號(hào)標(biāo)準(zhǔn)、支持流水作業(yè)工作模式、內(nèi)設(shè)塊存儲(chǔ)器等特點(diǎn)。

本文作者創(chuàng)新點(diǎn):在電路設(shè)計(jì)方面:擺脫了以往Cameralink接口型相機(jī)在與信號(hào)處理器進(jìn)行通信時(shí)必須在相機(jī)和處理器之間加入電平轉(zhuǎn)換芯片的做法,充分利用了FPGA支持LVDS電平的優(yōu)勢(shì),從而減小了告警系統(tǒng)的電路體積和復(fù)雜度,在硬件方面提高了系統(tǒng)的可靠性。在程序設(shè)計(jì)方面:充分利用FPGA內(nèi)部 RAM資源,多處用到FIFO存儲(chǔ)器,以流水作業(yè)為手段,縮短了系統(tǒng)響應(yīng)時(shí)間。