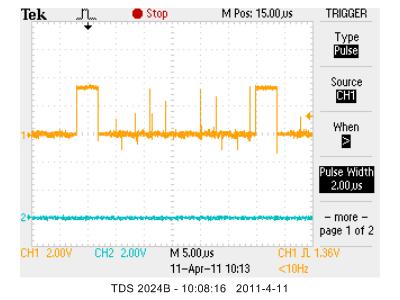

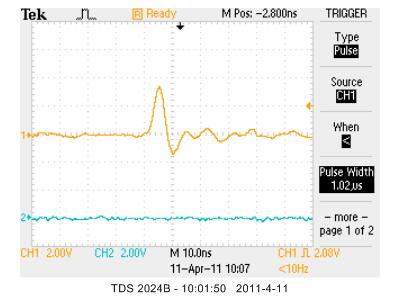

在采集一組并行接口信號(hào)時(shí),發(fā)現(xiàn)接收到的數(shù)據(jù)非常不穩(wěn)定。用示波器測(cè)量幾個(gè)用于同步的控制信號(hào),發(fā)現(xiàn)時(shí)不時(shí)的有毛刺產(chǎn)生。因?yàn)檫@些數(shù)據(jù)最終都是要顯示在液晶屏上的,當(dāng)示波器同時(shí)測(cè)量?jī)蓚€(gè)同步信號(hào)時(shí),液晶屏的顯示錯(cuò)位現(xiàn)象得到明顯好轉(zhuǎn)。示波器探頭測(cè)量信號(hào)時(shí)相當(dāng)于并聯(lián)上一個(gè)pF級(jí)的電容,也能夠一定程度上起到濾波的效果,因此可以斷定同步信號(hào)的毛刺影響了數(shù)據(jù)的采集。其中一個(gè)同步信號(hào)如圖1,兩個(gè)有效高脈沖之間有很多毛刺,放大毛刺后如圖2所示,大約維持10ns的高電平。

圖1

圖2

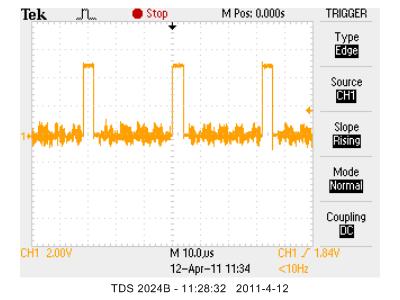

如何濾除這些毛刺呢?辦法有兩個(gè),其一就是用純粹硬件的辦法,在信號(hào)進(jìn)入FPGA之前進(jìn)行濾波處理,串個(gè)電阻并個(gè)電容都可以,特權(quán)同學(xué)并了一個(gè)20pF電容后就能夠把這些毛刺徹底濾干凈,如圖3所示。

圖3

而還有一種“軟”硬件濾波的方法。就如特權(quán)同學(xué)收錄進(jìn)<深入淺出玩轉(zhuǎn)FPGA>一書中的博文<基于FPGA的跨時(shí)鐘域信號(hào)處理——亞穩(wěn)態(tài)>所談到的,降低數(shù)據(jù)采集頻率以及多次采集后邏輯處理都是一種思路。那這里特權(quán)同學(xué)給出一種多次采集處理的濾波方法和大家分享。

input ain; //輸入信號(hào)

reg[3:0] ainr; //輸入信號(hào)緩存

//輸入信號(hào)打4拍

always @(posedge clk or negedge rst_n)

if(!rst_n) ainr <= 4‘d0;

else ainr <= {ainr[2:0],ain};

//輸入信號(hào)上升沿檢測(cè),高電平有效

wire pos_ain = ~ainr[3] & ~ainr[2] & ainr[1] & ainr[0];

//通常只要兩個(gè)信號(hào)就行,即wire pos_ain = ~ainr[2] & ainr[1] ;。

//這里用了4個(gè)信號(hào)就是多次采樣濾波的效果

//輸入信號(hào)下降沿檢測(cè),高電平有效

wire neg_ain = ainr[3] & ainr[2] & ~ainr[1] & ~ainr[0];

//通常只要兩個(gè)信號(hào)就行,即wire neg_ain = ainr[2] & ~ainr[1] ;。

//這里用了4個(gè)信號(hào)就是多次采樣濾波的效果

//若該輸入信號(hào)主要關(guān)注其高脈沖,那么可以做以下濾波

wire high_ain = ainr[1] & ainr[0];

//兩個(gè)信號(hào)相與通常可以濾除1個(gè)clk的毛刺,相應(yīng)的,3個(gè)信號(hào)相與可以濾除2個(gè)clk的毛刺

//若該輸入信號(hào)主要關(guān)注其低脈沖,那么可以做以下濾波

wire low_ain = ainr[1] | ainr[0];