摘 要: 介紹一種基于單片機(jī)系統(tǒng)設(shè)計(jì)的DMA硬件電路,以字塊傳輸方式與高速A/D接口。結(jié)合在數(shù)字式磁通表設(shè)計(jì)中的應(yīng)用給出其硬件軟件設(shè)計(jì)方案實(shí)例。

關(guān)鍵詞: 單片機(jī)系統(tǒng) 直接存儲(chǔ)器存取(DMA)方式 高速A/D

PC機(jī)中外設(shè)與內(nèi)存儲(chǔ)器之間數(shù)據(jù)直接傳輸?shù)腄MA功能以其高效、高速、CPU資源占用少等特點(diǎn)已被廣泛應(yīng)用,這一功能通過安裝在主板上的專用DMA控制器芯片或集成在外圍控制芯片來實(shí)現(xiàn)。單片機(jī)的應(yīng)用領(lǐng)域也常常需要有高速數(shù)據(jù)傳輸或數(shù)據(jù)采集,雖然近些年單片機(jī)速度有所提高,仍然無法應(yīng)付類似單脈沖信號(hào)捕獲、周期信號(hào)頻譜分析等需要采用高速A/D的場合。對于速率在100ksps以上的數(shù)據(jù)采集或傳輸一般的中斷查詢法就不易實(shí)現(xiàn),因此考慮通過直接存儲(chǔ)存取操作才能完成。然而單片機(jī)內(nèi)部設(shè)計(jì)通常不具有DMA功能,也沒有現(xiàn)成的控制芯片可以利用。而目前通用DSP芯片對于開發(fā)小型儀器儀表而言價(jià)格過高。

數(shù)字式磁通表主要應(yīng)用在對恒定磁場的磁感應(yīng)強(qiáng)度或脈沖場磁感應(yīng)強(qiáng)度峰值的測量。是采用閉合線圈作為探測線圈,穿過線圈的磁通Φ變化時(shí),探測線圈中感應(yīng)電動(dòng)勢:![]() 瞬間將線圈由0磁場移到磁場最大點(diǎn),記錄下整個(gè)過程中感應(yīng)電動(dòng)勢ε的變化。變化過程結(jié)束后用軟件對ε進(jìn)行積分,計(jì)算出磁感應(yīng)強(qiáng)度。本設(shè)計(jì)所需解決的是在瞬間記錄下ε的變化曲線。

瞬間將線圈由0磁場移到磁場最大點(diǎn),記錄下整個(gè)過程中感應(yīng)電動(dòng)勢ε的變化。變化過程結(jié)束后用軟件對ε進(jìn)行積分,計(jì)算出磁感應(yīng)強(qiáng)度。本設(shè)計(jì)所需解決的是在瞬間記錄下ε的變化曲線。

本文討論一種采用數(shù)字邏輯電路設(shè)計(jì)的DMA控制電路。結(jié)合在“數(shù)字式磁通表”中的實(shí)際應(yīng)用,給出高速A/D芯片MAX153與89C51單片機(jī)系統(tǒng)DMA接口電路的主要原理圖和主程序流程。

1 系統(tǒng)構(gòu)成

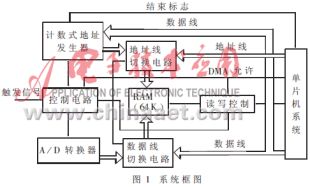

系統(tǒng)結(jié)構(gòu)如圖1所示。

設(shè)計(jì)采用89C51單片機(jī)芯片組成的單片機(jī)系統(tǒng),外部64K RAM采用62512芯片,存儲(chǔ)器的全部64K地址范圍允許作為外設(shè)的A/D轉(zhuǎn)換電路在DMA周期寫入,以及單片機(jī)在非DMA周期讀出寫入。RAM的數(shù)據(jù)線和地址線由總線切換電路來控制,選擇連接單片機(jī)系統(tǒng)總線或連接A/D轉(zhuǎn)換電路的數(shù)據(jù)輸出和地址發(fā)生器輸出地址。總線切換電路不僅切換地址線和數(shù)據(jù)線,同時(shí)切換RAM的寫控制線WRI,控制實(shí)現(xiàn)DMA周期外設(shè)寫入和非DMA周期的單片機(jī)寫入。RAM讀控制線接單片機(jī)/READ。

DMA周期時(shí),RAM的寫入地址由地址發(fā)生器產(chǎn)生。它是一個(gè)可預(yù)置數(shù)的16位二進(jìn)制計(jì)數(shù)器。其溢出信號(hào)作為DMA周期的結(jié)束控制和結(jié)束標(biāo)志。

2 硬件組成

· 單片機(jī)芯片

采用ATMEL公司的89C51,片內(nèi)有4K字節(jié)FLASH ROM。設(shè)計(jì)使用其最大時(shí)鐘頻率20MHz,可以有1μs以下的指令周期。

· A/D轉(zhuǎn)換器

采用MAXIM公司的MAX153芯片,轉(zhuǎn)換精度8bit并行輸出,轉(zhuǎn)換時(shí)間660ns、采集速率1Msps。設(shè)計(jì)采用循環(huán)采集方式。

· 靜態(tài)RAM

靜態(tài)RAM62512芯片為64Kbytes,典型存取時(shí)間200ns。

· 總線(數(shù)據(jù)線、地址線和WR)切換電路

總線切換采用74HC245三態(tài)總線收發(fā)器并聯(lián),分別選通。如圖2所示。

· 寫地址產(chǎn)生電路

DMA寫地址產(chǎn)生電路是一可預(yù)置數(shù)的16位2進(jìn)制計(jì)數(shù)器,電路是采用四片4位可預(yù)置計(jì)數(shù)器74HC569級(jí)連方式。因此可以預(yù)置16位地址的初值,就是DMA傳輸數(shù)據(jù)塊的起始地址。計(jì)數(shù)脈沖反向輸入74HC569的CP端以保證寫操作的時(shí)序。

3 工作原理

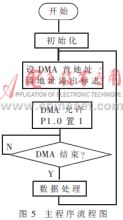

3.1 DMA允許與響應(yīng)

單片機(jī)系統(tǒng)開機(jī)運(yùn)行時(shí)或進(jìn)行內(nèi)部數(shù)據(jù)處理、顯示時(shí)應(yīng)置P1.0高,使其處于DMA禁止?fàn)顟B(tài)。單片機(jī)完成初始化或進(jìn)入DMA準(zhǔn)備就緒狀態(tài)時(shí),先向地址發(fā)生器寫入數(shù)據(jù)塊的起始地址,將地址溢出標(biāo)志位置零,再發(fā)出DMA允許信號(hào)釋放RAM的控制權(quán),等待DMA結(jié)束標(biāo)志和DMA控制信號(hào)。當(dāng)DMA允許為1且地址計(jì)數(shù)器溢出標(biāo)志為0時(shí),進(jìn)入DMA預(yù)備狀態(tài),等待外部觸發(fā)信號(hào)輸入。DMA觸發(fā)信號(hào)可以是周期信號(hào)的過零脈沖,也可以是單脈沖信號(hào)放大整形輸出,或者是A/D轉(zhuǎn)換完成信號(hào)。DMA控制部分如圖3所示。本設(shè)計(jì)采用將感應(yīng)電動(dòng)勢信號(hào)放大整形,其脈沖前沿觸發(fā)。DMA允許后的第一個(gè)觸發(fā)脈沖到來,D觸發(fā)器輸出Q為1。開通四輸入端與非門輸出與振蕩器同頻同相的周期信號(hào),開始數(shù)據(jù)采集和傳送。由NE555和阻容元件組成的方波振蕩器的振蕩頻率決定采樣頻率的大小,其頻率應(yīng)小于等于A/D轉(zhuǎn)換器的最大轉(zhuǎn)換速率1Msps。與非門輸出信號(hào)同時(shí)作為RAM寫信號(hào)、A/D芯片讀/RD,經(jīng)反相后作為地址計(jì)數(shù)器的計(jì)數(shù)輸入。

3.2 數(shù)據(jù)線與地址線的控制

總線的選擇控制由DMA允許信號(hào)控制兩組74HC245三態(tài)總線收發(fā)器,使其分別處于開通和高阻狀態(tài)。此兩組總線收發(fā)器一端并接至RAM,另一端分別接單片機(jī)系統(tǒng)總線和A/D轉(zhuǎn)換外部總線。當(dāng)DMA禁止周期時(shí)DMA允許信號(hào)為低,選通系統(tǒng)總線允許單片機(jī)對RAM進(jìn)行讀寫操作。反之當(dāng)DMA周期時(shí)DMA允許信號(hào)為高,選通外部總線允許DMA控制器對RAM寫操作。數(shù)據(jù)線有8根(D0~D7),對數(shù)據(jù)線的切換需要兩片74HC245,而地址線有16根(A0~A15),切換地址線需要4片74HC245才可以。另外還需兩片用以對RAM的讀寫線的切換,對讀寫線的控制采用相同的方法,也是由DMA允許進(jìn)行兩周期的控制權(quán)切換。

3.3 DMA塊數(shù)據(jù)傳輸

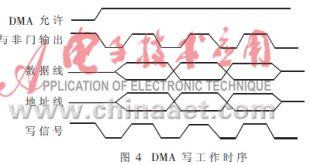

與非門輸出1MHz的振蕩信號(hào),連接A/D芯片/RD腳,在低電平開始時(shí)已采集的數(shù)據(jù)被輸出到數(shù)據(jù)線。地址計(jì)數(shù)器被設(shè)計(jì)為下降沿觸發(fā),因此下降沿開始后地址計(jì)數(shù)器將在預(yù)設(shè)的起始地址的基礎(chǔ)上加1,形成新的地址輸出至地址線。數(shù)據(jù)和地址的形成均在下降沿后的160ns(由74HC系列計(jì)數(shù)器性能參數(shù)可知其最大傳輸延遲時(shí)間為40ns,有四片級(jí)連總計(jì)160ns。由MAX153CPP的手冊可知其讀寫模式下Data-AccessTime為160ns)內(nèi)完成,其小于振蕩信號(hào)低電平停留時(shí)間500ns。在下一個(gè)振蕩的下降沿到來之前數(shù)據(jù)地址保持不變,在此后的上升沿時(shí)數(shù)據(jù)被寫入RAM的指定地址,第二個(gè)下降到來后重復(fù)這樣的過程,地址計(jì)數(shù)器加1形成新的地址和讀出A/D轉(zhuǎn)換器中新的數(shù)據(jù),再寫入儲(chǔ)存器。工作時(shí)序參見圖4。

3.4 響應(yīng)過程的結(jié)束

DMA過程的結(jié)束設(shè)計(jì)在地址溢出時(shí)。設(shè)計(jì)利用地址計(jì)數(shù)器的溢出位,當(dāng)?shù)刂芬绯黾创笥?FFFF)H時(shí)溢出位為1,經(jīng)反向器反向后至四輸入端與非門的輸入端,使其輸出常為高而達(dá)到封鎖的目的。直到單片機(jī)系統(tǒng)重新初始化地址計(jì)數(shù)器,清溢出標(biāo)志,并重新DMA允許后才能再次進(jìn)入DMA準(zhǔn)備就緒狀態(tài)。

4 軟件設(shè)計(jì)(主流程)

主程序流程圖見圖5。

單片機(jī)系統(tǒng)以其方便、簡潔、靈活、廉價(jià)為主要特點(diǎn),所以在DMA電路設(shè)計(jì)中一定要結(jié)合實(shí)際應(yīng)用簡化設(shè)計(jì),軟件硬件綜合設(shè)計(jì)避免系統(tǒng)過于復(fù)雜,才能達(dá)到優(yōu)質(zhì)廉價(jià)的最終目的。利用本設(shè)計(jì)研制的數(shù)字式磁通表綜合性能達(dá)到了預(yù)期指標(biāo),并獲得滿意的性能價(jià)格比。

參考文獻(xiàn)

1 MAXIM公司新產(chǎn)品數(shù)據(jù)手冊(四).1995

2 何立民.單片機(jī)應(yīng)用系統(tǒng)設(shè)計(jì). 北京:北京航空航天大學(xué)出版社,1990