0 引言

脈寬調(diào)制技術(shù)(PWM)目前廣泛應(yīng)用在電力、電子、微型計(jì)算機(jī)、自動(dòng)控制等多個(gè)學(xué)科領(lǐng)域。本設(shè)計(jì)采用基于FPGA的直接數(shù)字頻率合成(DDS)技術(shù),通過D/A轉(zhuǎn)換進(jìn)行程控放大,實(shí)現(xiàn)了三相功率可控的PWM信號(hào)。

1 系統(tǒng)的設(shè)計(jì)原理和實(shí)現(xiàn)過程

1.1 DDS的設(shè)計(jì)原理

直接數(shù)字頻率合成器(DDS)的組成見圖1。fc為時(shí)鐘頻率,K為頻率控制字,N為相位累加器的字長(zhǎng),W波形存儲(chǔ)器地址線位數(shù),L為ROM數(shù)據(jù)線寬度(一般也為D/A轉(zhuǎn)換器的位數(shù)),fo為輸出頻率。相位累加器按照時(shí)鐘脈fc的時(shí)序,對(duì)輸入頻率控制字K進(jìn)行累加,相位累加器的輸出作為波形存儲(chǔ)器的地址輸入。相位累加器的輸出對(duì)應(yīng)于該時(shí)刻合成周期信號(hào)的相位,由于N位累加產(chǎn)生溢出,因而相位是周期性的,在0~2π范圍內(nèi)變化。2π/2N rad是最小的相位增量,完成一整周的正弦波輸出需要經(jīng)過2π/(K×2π/2N rad)個(gè)系統(tǒng)時(shí)鐘周期。因此,可以得到輸出波形的頻率fo為:

而DDS的最小頻率分辨率(即最低的合成頻率)為

![]()

最高的基波合成頻率受奈奎斯持抽樣定理的限制(至少每周兩次抽樣才能重構(gòu)波形)。

由此可以看出,DDS具有高頻率分辨率的特點(diǎn)。在fc固定時(shí),取決于相位累加器的位數(shù)N,只要N足夠大,理論上就可以獲得相應(yīng)的分辨精度,這是傳統(tǒng)方法難以實(shí)現(xiàn)的。DDS中相位改變是線性過程,其相位誤差主要依賴于時(shí)鐘的相位特性,相位誤差小,形成的信號(hào)具有良好的頻譜特性。

1.2 用FPGA和DDS技術(shù)產(chǎn)生三相PWM的原理

本設(shè)計(jì)需要設(shè)計(jì)能夠輸出三相的PWM信號(hào)。根據(jù)DDS的原理,相位累加器的輸出對(duì)應(yīng)于該時(shí)刻合成周期信號(hào)的相位,并且相位具有周期性,在0~2π范圍內(nèi)變化。因此設(shè)置相位累加器的初始值,就可以使產(chǎn)生的信號(hào)具有不同的初相位。

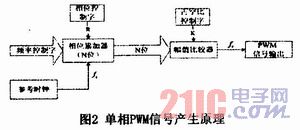

本設(shè)計(jì)的單相PWM信號(hào)在FPGA上實(shí)現(xiàn)的原理和過程如圖2所示。相位控制字R設(shè)置相位累加器的初始值,可決定PWM信號(hào)的初相。圖2中,使用一個(gè)幅值比較器取代了圖1中的波形儲(chǔ)存器,幅值比較器是一個(gè)0/1輸出的二值比較器,它決定了輸出脈沖的波形。由前面分析可知,累加器的輸出值是線性的,它的值與相位一一對(duì)應(yīng),因此累加器的輸出值與參數(shù)K進(jìn)行比較結(jié)果決定輸出信號(hào)fo的高低電平。K作為一個(gè)門限值,通過設(shè)置K便可設(shè)置輸出脈沖波形的占空比,我們把K稱為占空比控制字。多路單相PWM電路共用一個(gè)參考時(shí)鐘fc就可以構(gòu)成多相PWM信號(hào),各相PWM均有獨(dú)立的R和K,通過設(shè)置便可獲得多路同頻異相、占空比不同的PWM信號(hào)。

由于使用了DDS原理方法,上述PWM脈沖信號(hào)具有高頻率和相位分辨率的特點(diǎn)。但圖2中的DDS方法是有區(qū)別于傳統(tǒng)DDS實(shí)現(xiàn)的,它沒有使用波形存儲(chǔ)單元,節(jié)省了FPGA的存儲(chǔ)空間,使設(shè)計(jì)全數(shù)字化,便于在FPGA上實(shí)現(xiàn),方法簡(jiǎn)單高效。

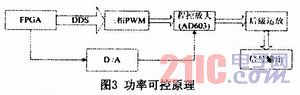

1.3 功率可控的設(shè)計(jì)

PWM信號(hào)的功率可控是為了滿足不同應(yīng)用的需求。本設(shè)計(jì)通過程控放大(AGC)實(shí)現(xiàn)PWM信號(hào)的功率可控,圖3是功率可控的原理框圖。

AD603是美國(guó)AD公司繼AD600后推出的寬頻帶、低噪聲、低畸變、高增益精度的壓控VGA芯片。由FPGA、D/A轉(zhuǎn)換器和可編程增益放大器AD603構(gòu)成程控放大的原理如圖3所示。FPGA通過對(duì)控制D/A輸出直流電壓來控制AD603的內(nèi)部電阻衰減網(wǎng)絡(luò),實(shí)現(xiàn)增益調(diào)節(jié)。其外圍元件少,電路簡(jiǎn)單,由于AD603帶寬最大能達(dá)到90MHz,增益范圍有40dB,增益精度在±0.5dB,可精確實(shí)現(xiàn)電壓的控制,實(shí)現(xiàn)功率的精確步進(jìn)控制。

2 設(shè)計(jì)的測(cè)試與結(jié)果分析

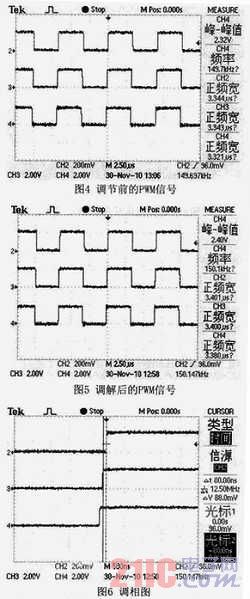

系統(tǒng)的測(cè)試結(jié)果如圖4、圖5及圖6所示。

圖1中的信號(hào)為作為比較的基準(zhǔn)信號(hào)。信號(hào)的頻率為149.7kHz,峰峰值2.32V,正頻寬3.344μs,即占空比為50%。信號(hào)進(jìn)行調(diào)幅、調(diào)頻及調(diào)相后如圖5所示,峰峰值為2.40V,步進(jìn)增量為80mV;頻率調(diào)為150.1 kHz,步進(jìn)增量為0.4kHz;正頻寬3.40 μs,占空比為51%;調(diào)相效果如圖6所示,相位調(diào)節(jié)為2.16°。

測(cè)試設(shè)備為Tektronix TDS2024型的數(shù)字存儲(chǔ)示波器。排除測(cè)試過程的誤差,結(jié)果調(diào)制波形有較高的精度,基本達(dá)到了設(shè)計(jì)要求。

3 結(jié)論

基于FPGA實(shí)現(xiàn)的DDS的方法結(jié)合了FPGA及DDS的特點(diǎn)和優(yōu)勢(shì),非常適用于產(chǎn)生頻率、相位、占空比可調(diào)的信號(hào),這恰好是PWM信號(hào)所需求的。目標(biāo)系統(tǒng)實(shí)現(xiàn)了高精度、高分辨率的任意頻率的三相PWM信號(hào)發(fā)生器的設(shè)計(jì),在實(shí)測(cè)中取得了較好的效果。