摘要:本文設(shè)計(jì)的基于FPGA" title="FPGA">FPGA的電子密碼鎖" title="密碼鎖">密碼鎖,具有記憶和修改6位密碼、輸入密碼位數(shù)指示及防止多次試探密碼等功能,與銀行卡的原理和功能極其相似,使得密碼鎖的保密和安全性能進(jìn)一步增強(qiáng)。最后,給出了在Quartus II軟件開發(fā)平臺(tái)上實(shí)現(xiàn)密碼鎖各項(xiàng)功能的仿真圖,并在FPGA芯片EP1K30TC144-3上通過(guò)了驗(yàn)證。

關(guān)鍵詞:現(xiàn)場(chǎng)可編程門陣列;超高速集成電路硬件描述語(yǔ)言;密碼鎖

0 引言

電子密碼鎖能保護(hù)用戶的重要資料不被非法用戶所竊取,目前使用的電子密碼鎖大多以單片機(jī)為控制器,通過(guò)運(yùn)行程序完成密碼鎖的各項(xiàng)功能。由于受到外部干擾的影響,單片機(jī)很容易將程序“跑飛”,因而可靠性較差。仿照銀行卡輸入密碼的原理,本文介紹了一種基于FG-PA的多功能密碼鎖的設(shè)計(jì)和實(shí)現(xiàn)方案,由于采用純硬件實(shí)現(xiàn),使得可靠性和安全性大大提高。

1 電子密碼鎖的功能要求

設(shè)計(jì)的密碼鎖至少具有下列功能:

(1)6位密碼,與銀行卡密碼位數(shù)相同;

(2)每位密碼采用十六進(jìn)制數(shù),與十進(jìn)制數(shù)密碼相比,密碼被破譯的概率大大降低;

(3)每位密碼按下時(shí),有密碼位數(shù)指示,類似自動(dòng)取款機(jī)輸入密碼時(shí)有“*”號(hào)提示;

(4)密碼輸入過(guò)程中密碼有誤時(shí),能對(duì)已經(jīng)輸入的密碼清除以便重新輸入密碼;

(5)6位密碼輸入都正確后,應(yīng)有開鎖指示,上鎖時(shí)也應(yīng)有上鎖指示;

(6)密碼連續(xù)三次輸入錯(cuò)誤,密碼鎖死鎖,并開啟報(bào)警,防止竊賊多次試探密碼;

(7)初始密碼默認(rèn)為“123456”,密碼可以修改,在密碼鎖打開狀態(tài)下,再一次輸入正確的舊密碼及兩次輸入的新密碼一致時(shí),密碼才能修改成功。

2 密碼鎖的系統(tǒng)構(gòu)成

根據(jù)密碼鎖具有的功能,可將其實(shí)現(xiàn)的功能劃分成分頻模塊、鍵盤和數(shù)碼管掃描模塊、按鍵抖動(dòng)消除模塊、按鍵編碼模塊、鍵值到7段數(shù)碼管譯碼顯示模塊和主控制模塊等6個(gè)子模塊,如圖1所示。

(1)分頻模塊。它對(duì)系統(tǒng)的主時(shí)鐘進(jìn)行分頻,以產(chǎn)生4×8小鍵盤的列掃描信號(hào)和6位數(shù)碼管的列掃描信號(hào)所需要的時(shí)鐘。分頻是因?yàn)橄存I抖動(dòng)的計(jì)數(shù)器時(shí)鐘要比分頻后掃描時(shí)鐘高得多。

(2)鍵盤和數(shù)碼管掃描模塊。它檢測(cè)到分頻輸出信號(hào)的上升沿到來(lái)時(shí),就對(duì)掃描的列加1,當(dāng)掃描到最后一列即第7列,再?gòu)牡?列開始掃描。當(dāng)檢測(cè)到有鍵按下的掃描控制信號(hào)時(shí),則停止列掃描,直至按鍵釋放后,再接著掃描下一列。數(shù)碼管的6列掃描信號(hào)和小鍵盤的8列掃描信號(hào)可以共用,當(dāng)掃描到小鍵盤的第6、7列時(shí),并沒(méi)有掃描6位數(shù)碼管,由于掃描速度足夠快,這并不影響數(shù)碼管的動(dòng)態(tài)顯示。

(3)按鍵抖動(dòng)消除模塊。機(jī)械鍵按下時(shí),會(huì)產(chǎn)生抖動(dòng)現(xiàn)象,若不消除,一次按鍵會(huì)被錯(cuò)誤地認(rèn)為同一鍵被多次按下,從而造成無(wú)法正確地輸入密碼。消除的方法可以采用硬件方法如RS觸發(fā)器和軟件延時(shí)方法,本文采用后者。

(4)按鍵編碼模塊。它負(fù)責(zé)將按下鍵的行列位置碼編碼成0~31的鍵值碼,鍵值0~15當(dāng)作有效的16進(jìn)制數(shù)輸入密碼位,大于等于16的鍵值可以定義成功能鍵,如定義清除密碼鍵[Clear]鍵值為17,確認(rèn)鍵[Enter]鍵值為23,修改密碼鍵[Chgsecret]鍵值為24,其他沒(méi)有定義的鍵可

以預(yù)留升級(jí)時(shí)的備用功能鍵。

(5)譯碼顯示模塊。它負(fù)責(zé)將按下的數(shù)值鍵0~F譯碼成7段LED共陰極字型碼。

(6)主控模塊。它依據(jù)消除抖動(dòng)后產(chǎn)生的按鍵釋放信號(hào)koff及按下的是數(shù)值鍵或功能鍵決定轉(zhuǎn)移的下一狀態(tài),在不同的狀態(tài)完成密碼的比較、修改及多次試探密碼報(bào)警提示等多項(xiàng)控制功能。

3 軟件實(shí)現(xiàn)

本文采用VHDL語(yǔ)言實(shí)現(xiàn)本密碼鎖系統(tǒng)的設(shè)計(jì)。對(duì)系統(tǒng)中劃分出的每一個(gè)模塊功能都可以采用一個(gè)進(jìn)程來(lái)描述。分頻、掃描和譯碼顯示三個(gè)功能模塊都比較簡(jiǎn)單,本文只重點(diǎn)介紹剩余的3個(gè)模塊實(shí)現(xiàn)原理及進(jìn)程中的部分關(guān)鍵代碼。完整的代碼可以向本文作者發(fā)郵件索取。

根據(jù)主控制模塊實(shí)現(xiàn)的功能,可以整理成如下圖2所示的流程圖,圖中對(duì)修改密碼的流程作了省略。

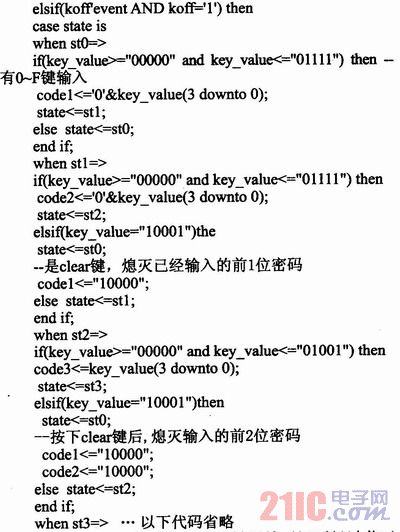

實(shí)現(xiàn)圖2流程的部分關(guān)鍵代碼如下:

完成消除抖動(dòng)的進(jìn)程是在按鍵釋放后還要經(jīng)過(guò)若干個(gè)時(shí)鐘的延遲再判斷按鍵是否釋放,若真的釋放,信號(hào)koff才從0變?yōu)?,該信號(hào)也是控制模塊根據(jù)密碼輸入進(jìn)行狀態(tài)轉(zhuǎn)移的觸發(fā)信號(hào)。例如按下鍵產(chǎn)生的前沿抖動(dòng),這個(gè)抖動(dòng)產(chǎn)生的假釋放高電壓一般不會(huì)持續(xù)太多個(gè)時(shí)鐘(若系統(tǒng)的時(shí)鐘頻率高可以增加代碼中計(jì)數(shù)器的位寬以增加延時(shí)),之后又變?yōu)榉€(wěn)定的低電平,則該進(jìn)程再一次對(duì)計(jì)數(shù)器進(jìn)行清零,重新判斷。

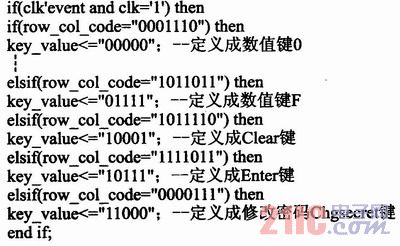

鍵值編碼功能是將按下鍵的行列位置碼賦予相應(yīng)的鍵值,自然地將0~F鍵定義成鍵值為0~15,功能鍵的定義比較隨意。實(shí)現(xiàn)的部分代碼如下:

4 仿真結(jié)果

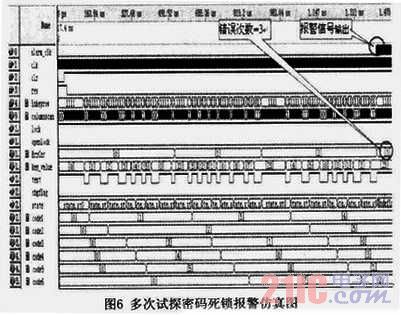

本設(shè)計(jì)在QuartusⅡ9.0軟件平臺(tái)上進(jìn)行了密碼鎖各項(xiàng)功能的波形仿真。

圖3是輸入了錯(cuò)誤的密碼123450并按下enter鍵(鍵值23)后,密碼鎖沒(méi)有打開的仿真圖,圖4是輸入正確的密碼123456和enter鍵后,密碼鎖能打開的仿真圖。

圖5是先輸入了一位密碼9,又按了clead鍵(鍵值17),接著又輸入了正確的密碼123456和enter鍵后,鎖能正確打開的仿真圖。

圖6是第一次輸入密碼123450,第二次輸入了521087,第三次輸入了450313,3次錯(cuò)誤的密碼后,啟動(dòng)防止多次試探密碼功能,密碼鎖進(jìn)入報(bào)警狀態(tài),并維持在報(bào)警狀態(tài)不退出,相當(dāng)于密碼鎖處于死鎖狀態(tài)。

圖3~6中的codel~code6是臨時(shí)存儲(chǔ)輸入密碼的寄存器。另外,在開鎖狀態(tài)下,按下修改密碼Chgsecrer鍵時(shí),進(jìn)行修改密碼的仿真圖,由于輸入輸出的數(shù)據(jù)量很多,全景視圖時(shí)不是很清楚,只能局部放大瀏覽,這里不再給出。

5 結(jié)論

本密碼鎖的各項(xiàng)功能也在FPGA芯片上EP1K30TC144-3下載通過(guò)了驗(yàn)證,實(shí)驗(yàn)表明,此密碼鎖運(yùn)行穩(wěn)定可靠,各項(xiàng)功能都能滿足要求。在實(shí)際應(yīng)用中可將數(shù)碼管顯示的密碼一律都用“-”來(lái)顯示,起到隱藏密碼位的目的