為了確保芯片在制作完成后的正確性,有關(guān)電路測(cè)試的這個(gè)問(wèn)題越來(lái)越受重視。而且其測(cè)試的難度及成本也越來(lái)越高,于是如何有效地檢驗(yàn)電路的正確性,并大幅度地降低測(cè)試成本,成為我們現(xiàn)在研究的熱點(diǎn)。通常我們?cè)谠O(shè)計(jì)芯片的同時(shí),可以根據(jù)芯片本身的特征,額外地把可測(cè)性電路設(shè)計(jì)(Design For Testability)在芯片里。談到可測(cè)性的電路設(shè)計(jì),內(nèi)建自測(cè)試(BIST)和基于掃描Scan—Based)的電路設(shè)計(jì)是常被提及的。

基于掃描的電路設(shè)計(jì)是可測(cè)性設(shè)計(jì)中最常用的一種方法。它是屬于Test—Per—Scan測(cè)試方法的電路。

目前的測(cè)試方法有兩種,一種是Test—Per—Scan,另一種是Test—Per—Clock,這兩種測(cè)試方法各有各的優(yōu)缺點(diǎn)。所謂Test—Per—Scan的運(yùn)作方式,就是我們將一個(gè)電路里的全部或部分寄存器串聯(lián)起來(lái),形成一條掃描鏈,然后將測(cè)試序列在每個(gè)周期移入一個(gè)值,直到測(cè)試向量填滿整個(gè)掃描路徑為止,再經(jīng)過(guò)一個(gè)周期后,我們將待測(cè)電路的測(cè)試結(jié)果傳到掃描鏈里。最后移出做壓縮分析。這種方法的優(yōu)點(diǎn)是很容易運(yùn)用在任何商業(yè)性的設(shè)計(jì)流程中,而且其硬件架構(gòu)對(duì)系統(tǒng)功能的影響較小,控制硬件設(shè)計(jì)也較為簡(jiǎn)單:缺點(diǎn)是要*較多的時(shí)間來(lái)產(chǎn)生測(cè)試向量,測(cè)試速度慢。所謂Test—Per一Clock,就是當(dāng)我們?cè)跍y(cè)試電路的時(shí)候,每一個(gè)周期都送進(jìn)一個(gè)新的測(cè)試向量進(jìn)入電路,同時(shí)在電路的輸出得到測(cè)試的結(jié)果,所以這種方式的電路測(cè)試時(shí)間較短,速度較快。

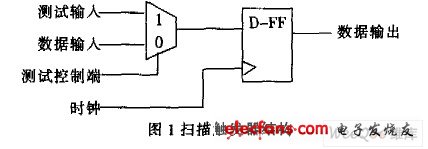

基于掃描的電路設(shè)計(jì),主要是將待測(cè)電路內(nèi)的寄存器,全部或部分用掃描寄存器來(lái)代替,讓我們?cè)趯?duì)電路進(jìn)行測(cè)試的時(shí)候可以輕易地控制其輸入及輸出,掃描寄存器最常用的結(jié)構(gòu)是多路掃描寄存器,它是在普通寄存器的輸入端口加上一個(gè)多路器, 如圖1所示。測(cè)試控制端即多路器的選擇端,數(shù)據(jù)輸入端為正常的功能輸入端。此外還有測(cè)試輸入端、時(shí)鐘輸入端和數(shù)據(jù)輸出端。當(dāng)測(cè)試輸入端為“0”時(shí),寄存器為正常的功能輸入,電路處于正常模式;當(dāng)測(cè)試輸入端為“1”時(shí),寄存器為掃描輸入。電路就轉(zhuǎn)換成掃描模式。很明顯。基于掃描的電路設(shè)計(jì)可以增加待測(cè)電路的可控制性和可觀察性。這種設(shè)計(jì)方式。優(yōu)點(diǎn)是需要額外的硬件空間較少,而且測(cè)試的效果較好,缺點(diǎn)是測(cè)試時(shí)間太長(zhǎng)。造成測(cè)試時(shí)間長(zhǎng)的原因有多個(gè)方面,我們可以通過(guò)分析基于掃描的電路設(shè)計(jì)來(lái)得到。這個(gè)缺點(diǎn),正是我們想要改進(jìn)的部分。

2 基于掃描的電路的基本單元

2.1 線性反饋移位寄存器(LFSR)

最簡(jiǎn)單的測(cè)試向量產(chǎn)生器就是由線性反饋移位寄存器(Linear Feedback Shift Registers,LFSR)來(lái)組成的。因?yàn)楫?dāng)時(shí)鐘信號(hào)改變時(shí),線性反饋移位寄存器內(nèi)D觸發(fā)器的值就會(huì)改變,此時(shí)我們就可以將這些會(huì)一直改變的值當(dāng)成測(cè)試向量,送給電路做測(cè)試。

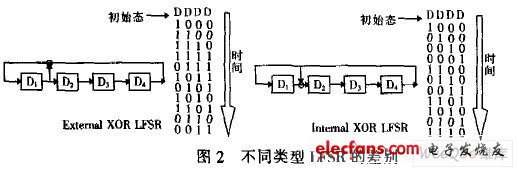

一般的線性反饋移位寄存器可以分為兩類(lèi),分別是Extemal XOR線性反饋移位寄存器和Internal XOR線性反饋移位寄存器,如圖2所示。這兩種線性反饋移位寄存器的主要差別在于External XOR線性反饋移位寄存器的modulo一2加法器是放在電路的反饋路徑上。而Internal XOR的線性反饋移位寄存器的加法器則是放在兩個(gè)寄存器之問(wèn)。這兩種不同結(jié)構(gòu)的線性反饋移位寄存器所產(chǎn)生出的測(cè)試向量也不一樣,ExternalXOR線性反饋移位寄存器所產(chǎn)生的測(cè)試向量有下列特性:每個(gè)向量與下個(gè)向量之問(wèn)的關(guān)系,是向量中的位分別往右移了一位。而Internal XOR的線性反饋移位寄存器由于modulo一2加法器是在寄存器之問(wèn),所以產(chǎn)生的測(cè)試向量看起來(lái)比External XOR線性反饋移位寄存器有更隨機(jī)的特性,所以我們必須選擇InternalXOR LFSR作為測(cè)試向量產(chǎn)生器。

2.2 多輸入特征寄存器(MISR)

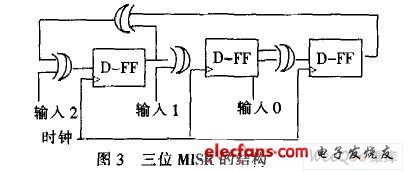

多輸入特征寄存器(Multiple Input Signature Reg—ister,MISR)是線性反饋移位寄存器的一種。如圖3所示,將待測(cè)電路的輸出部分加入線性反饋移位寄存器里,就成為一個(gè)多輸入特征寄存器。

多輸入特征寄存器最主要的特性是它的狀態(tài)。即其寄存器的值,不僅與現(xiàn)在的狀態(tài)有關(guān),還與當(dāng)時(shí)的輸入值有關(guān),可以表示為:Next state=MISR(Cur—renLstate,Input),而其中MISR(……)可以代表特征式不同的多輸入特征寄存器。

3 基于掃描的測(cè)試架構(gòu)的改進(jìn)

為了減少基于掃描的電路設(shè)計(jì)的測(cè)試時(shí)間,就必須深入了解它的電路設(shè)計(jì),了解為何其會(huì)消耗那么多的測(cè)試時(shí)間,然后來(lái)改進(jìn)測(cè)試架構(gòu)。

3.1 用向量壓縮來(lái)減少測(cè)試時(shí)間

在測(cè)試過(guò)程中,我們有時(shí)可以發(fā)現(xiàn),我們將要傳入掃描鏈的測(cè)試向量,已經(jīng)部分地包含在已經(jīng)傳入的測(cè)試向量序列中了,如圖4所示。V1向量的后半部分剛好等于V2向量的前半部分“1010”,如果在傳輸向量的時(shí)候,先傳輸V1再傳輸V2,那么我們就只需要將V2的后半段向量信息傳入掃描鏈就可以讓V2原本的信息在掃描鏈中完整地呈現(xiàn),如圖中V3所示。很明顯,我們?cè)瓉?lái)要輸入的測(cè)試向量的長(zhǎng)度為16位,壓縮后只有12位,節(jié)省了V2的前半部分傳入掃描鏈的時(shí)間,從而減少了測(cè)試的時(shí)間,而且測(cè)試信息也沒(méi)有減少,不會(huì)影響故障覆蓋率。

3.2 用Test—Per-Clock來(lái)縮短測(cè)試時(shí)間

我們對(duì)造成測(cè)試時(shí)間不夠理想的原因進(jìn)行分析:

傳統(tǒng)的基于掃描的測(cè)試電路是采取Test—Per—Scan的方式來(lái)進(jìn)行測(cè)試的,也就是說(shuō)要先將測(cè)試向量掃描到電路內(nèi)的由掃描寄存器所組成的掃描鏈內(nèi)。然后才可以完成一次測(cè)試;將測(cè)試向量掃描到待測(cè)電路這個(gè)步驟是一位一位地進(jìn)行的,所以如果一個(gè)電路需要長(zhǎng)度較大的測(cè)試的向量時(shí),那么在這整個(gè)測(cè)試過(guò)程里。將會(huì)花很多的時(shí)間在將測(cè)試向量輸入到掃描鏈的這個(gè)步驟上,從而增加了測(cè)試時(shí)間。這個(gè)結(jié)構(gòu)的測(cè)試向量的產(chǎn)生是利用LFSR產(chǎn)生出的偽隨機(jī)向量,并將其送入電路做測(cè)試。用LFSR產(chǎn)生測(cè)試向量會(huì)產(chǎn)生出許多沒(méi)有作用的測(cè)試向量,而這些沒(méi)有作用的測(cè)試向量又會(huì)產(chǎn)生大量多余的時(shí)間將其送入掃描鏈中,造成測(cè)試時(shí)間更嚴(yán)重的浪費(fèi)。如果采用Test—Per—Clock的方式做測(cè)試,在掃描鏈里原本的測(cè)試向量,在用一個(gè)時(shí)鐘的時(shí)間移進(jìn)來(lái)一位之后,掃描鏈所含的值即是測(cè)試向量,對(duì)待測(cè)電路而言,其實(shí)都是一個(gè)新的測(cè)試向量,而且也具有偽隨機(jī)向量的特性,如果此測(cè)試向量是有效的,我們的測(cè)試時(shí)間就只用了一個(gè)時(shí)鐘的時(shí)間,而如果此測(cè)試向量無(wú)效,原本測(cè)試到?jīng)]有作用的測(cè)試向量時(shí)所需的付出的時(shí)間代價(jià),由于用了新的測(cè)試向量填滿整個(gè)掃描鏈所需的時(shí)間,減少到只需一個(gè)時(shí)鐘移進(jìn)一位的時(shí)間。

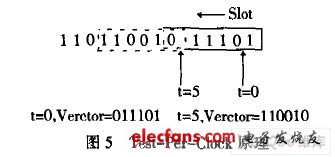

如圖5所示,每個(gè)時(shí)鐘周期。Slot會(huì)往左移動(dòng)一位,即在Slot內(nèi)產(chǎn)生一個(gè)新的測(cè)試向量,而Slot大小可以看成掃描鏈的大小。

不過(guò),由于每個(gè)時(shí)鐘都要作測(cè)試,所以每個(gè)時(shí)鐘在測(cè)試后都會(huì)產(chǎn)生新的測(cè)試結(jié)果。傳統(tǒng)的基于掃描的測(cè)試環(huán)境里,電路輸出結(jié)果傳送出來(lái)的同時(shí)也將新的測(cè)試傳進(jìn)掃描鏈里。

如果輸出的向量只有一位就不會(huì)有這樣的問(wèn)題。

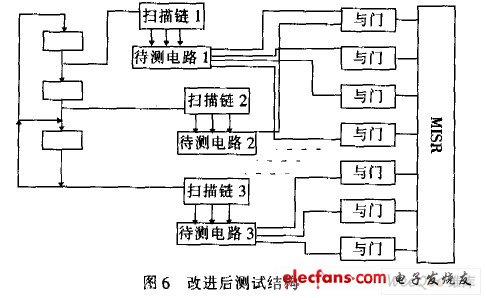

因?yàn)槲覀儸F(xiàn)在要產(chǎn)生一個(gè)新的測(cè)試向量所需要的時(shí)間只有一個(gè)時(shí)鐘周期,所以時(shí)問(wèn)剛剛好。但是一般而言,待測(cè)電路的輸出向量都會(huì)超過(guò)一位。所以我們?cè)谟^察電路輸出結(jié)果這個(gè)步驟上就會(huì)有問(wèn)題。為了解決這個(gè)問(wèn)題,需要對(duì)傳統(tǒng)的基于掃描的測(cè)試電路做些修改。在待測(cè)電路的輸出部分,可以用MISR來(lái)取代原來(lái)的掃描鏈電路,也就是將輸出送到MISR做特征分析,如圖6所示。

但是由于電路越來(lái)越復(fù)雜,電路的主要輸入與輸出的個(gè)數(shù)就會(huì)很多,如果對(duì)這樣的待測(cè)電路加測(cè)試電路,將會(huì)出現(xiàn)外加電路面積過(guò)大的問(wèn)題。所以我們針對(duì)MISR的部分提出一個(gè)方法,使得因測(cè)試而增加得MISR可以盡量地縮小。

縮小MISR的大小最直接的想法是將主要輸出經(jīng)組合電路壓縮變小,但是這樣會(huì)使錯(cuò)誤覆蓋率降低,使測(cè)試向量變多,這些問(wèn)題在文獻(xiàn)中談到了。造成錯(cuò)誤覆蓋率降低的原因是如果我們將有共同輸入向量的兩個(gè)主要輸出通過(guò)組合電路合并的話。將可能會(huì)造成原本可以測(cè)試到的錯(cuò)誤,在合并后就測(cè)試不到了,所以造成了錯(cuò)誤覆蓋率的降低。

為了避免這個(gè)情況的發(fā)生,我們?cè)谙蛄繅嚎s的過(guò)程中。只有將沒(méi)有共同輸入向量的主要輸出合并在一起,就不會(huì)有問(wèn)題出現(xiàn)了。如圖6所示,兩個(gè)不同的待測(cè)電路的主要輸出經(jīng)過(guò)合并以后輸出到MISR,這樣用一個(gè)與門(mén)代替了一個(gè)寄存器以便減少面積,而錯(cuò)誤覆蓋率則因?yàn)閮蓛珊喜⒌闹饕敵龆硕紱](méi)有相同的主要輸出資料,所以就沒(méi)有錯(cuò)誤覆蓋率降低的問(wèn)題存在,即原來(lái)可以被偵測(cè)到的錯(cuò)誤,在經(jīng)過(guò)主要輸出端合并之后仍然可以被偵測(cè)到。

4 結(jié)論

經(jīng)過(guò)改進(jìn)后的基于掃描的測(cè)試架構(gòu),用向量壓縮來(lái)減少測(cè)試時(shí)間,并且將Test—Per-Scan的測(cè)試方式改成了Test—Per-Clock的測(cè)試方式,加快了測(cè)試的速度。