同樣,運(yùn)用此方法對(duì)高頻信號(hào)進(jìn)行測(cè)量時(shí),由于相位差相對(duì)較小,一般的微處理器時(shí)鐘頻率,已經(jīng)無(wú)法滿足高精度的計(jì)數(shù)要求,這樣必然會(huì)影響相位測(cè)量的精度。所以,必須提高標(biāo)準(zhǔn)時(shí)鐘的計(jì)數(shù)頻率,才能滿足測(cè)量要求。這樣,一方面增加了設(shè)計(jì)本身的難度,另一方面也提高了選用元器件的要求。本系統(tǒng)首先采用頻率變換法將高頻輸入信號(hào)轉(zhuǎn)換成低頻信號(hào)后,且保持原信號(hào)的相位不發(fā)生變化,再利用基于ADuC7128為控制核心的數(shù)字測(cè)相系統(tǒng)進(jìn)行測(cè)量,從而完成了寬頻帶" title="寬頻帶">寬頻帶輸入信號(hào)的相位測(cè)量。

1 差頻變換原理的引入

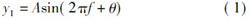

利用數(shù)學(xué)模型將被測(cè)信號(hào)和參考信號(hào)描寫成如下形式:

被測(cè)信號(hào):

參考信號(hào):

其中:A為被測(cè)信號(hào)的幅值;B為參考信號(hào)的幅值;f為被測(cè)信號(hào)的頻率;f0為參考信號(hào)的頻率;θ是被測(cè)信號(hào)的幅角。

同時(shí),將兩個(gè)信號(hào)y1和y2送入混頻器內(nèi)進(jìn)行混頻操作相乘后,會(huì)得到信號(hào)y3。

再將y3送入低通濾波器進(jìn)行濾波處理,濾除高頻信號(hào),剩下的低頻信號(hào)數(shù)學(xué)表達(dá)式為:

![]()

y3與y1相比,幅度呈線性變化,幅角不變,但頻率降低,其頻率是被測(cè)信號(hào)與參考信號(hào)的頻率差。對(duì)于測(cè)量y3來(lái)說(shuō),比直接測(cè)量y1容易得多。這樣把差頻變換法應(yīng)用到高頻信號(hào)的相位測(cè)量上,既可以提高相位測(cè)量的精度,又可以拓寬輸入信號(hào)的頻帶。

2 數(shù)字測(cè)相系統(tǒng)設(shè)計(jì)

2.1 硬件結(jié)構(gòu)設(shè)計(jì)

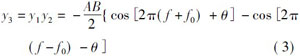

如圖1所示,本系統(tǒng)主要由信號(hào)調(diào)理電路、頻率變換電路以及微處理器控制電路3部分組成。

圖1 硬件電路原理框圖

2.1.1 信號(hào)調(diào)理電路

信號(hào)調(diào)理電路要完成對(duì)輸入信號(hào)的耦合、衰減、放大、電平調(diào)整等功能,系統(tǒng)有良好性能的前端模擬通道是進(jìn)行高精度測(cè)量所必須的[3]。本設(shè)計(jì)中的兩路信號(hào)調(diào)理通道CH1和CH2具有完全相同的對(duì)稱結(jié)構(gòu),且同時(shí)對(duì)輸入信號(hào)進(jìn)行信號(hào)調(diào)理。

2.1.2 頻率變換電路

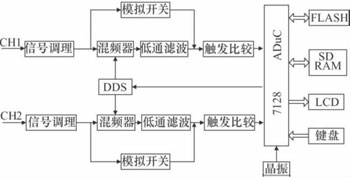

模擬乘法器是一種完成兩個(gè)模擬信號(hào)相乘的電子器件,由于乘法器與雙平衡混頻器相比具有更好的線性。因此,本設(shè)計(jì)選用了ADI公司的AD834芯片作為系統(tǒng)的混頻器使用,利用AD834將待測(cè)信號(hào)與ADuC7128內(nèi)部DDS模塊產(chǎn)生的參考信號(hào)進(jìn)行混頻后,再將差頻信號(hào)以單端電壓信號(hào)的方式輸出。

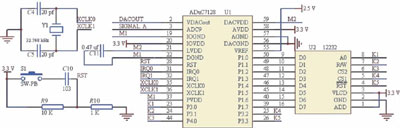

頻率變換電路如圖2所示,AD834的引腳X1和Y2均與地相連,將待測(cè)信號(hào)與參考信號(hào)分別以單端輸入的形式輸入到AD834的兩個(gè)信號(hào)端口Y1、X2。選擇Y1、X2 作為單端輸入引腳是因?yàn)檫@兩個(gè)引腳離輸出端比較遠(yuǎn),選擇它們作為輸入可以減小輸入信號(hào)到輸出端的耦合分量。根據(jù)設(shè)計(jì)需要,在AD834后面接入一個(gè)具有高開(kāi)環(huán)增益的運(yùn)算放大器OP-07,通過(guò)OP-7和R7、R6組成I /V轉(zhuǎn)換電路,這樣就可以將乘法器的輸出信號(hào)由雙端差分電流形式轉(zhuǎn)化為單端電壓形式。

圖2 頻率變換電路

2.1.3 微處理器控制電路

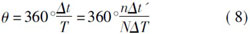

在進(jìn)行頻率轉(zhuǎn)換時(shí),需要一個(gè)頻率可調(diào)的信號(hào)源提供參考信號(hào)。以ARM7為內(nèi)核開(kāi)發(fā)的高性能微處理器ADuC7128內(nèi)部集成了一個(gè)輸出頻率可達(dá)到25MHz的DDS模塊,信號(hào)的輸出電壓在1V左右。其技術(shù)指標(biāo)滿足了作為參考信號(hào)的要求。同時(shí),ADuC7128可通過(guò)內(nèi)部PLL進(jìn)行時(shí)鐘倍頻,最高工作頻率可達(dá)41.78MHz,工作電壓在圖3ADuC7128控制電路3.0~3.6 V 范圍內(nèi)。ADuC7128微處理器自身結(jié)構(gòu)緊湊、體積小,能夠有效提高系統(tǒng)的集成度和可靠性。ADuC7128微處理器的控制電路,如圖3所示。

圖3 ADuC7128控制電路

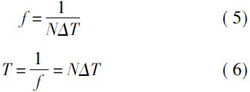

在本系統(tǒng)中,首先打開(kāi)CH1通道上的模擬開(kāi)關(guān),使被測(cè)信號(hào)繞過(guò)頻率轉(zhuǎn)換電路,而直接進(jìn)入比較器LT1715進(jìn)行整形,然后ADuC7128利用內(nèi)部計(jì)數(shù)器T0產(chǎn)生的標(biāo)準(zhǔn)計(jì)數(shù)脈沖對(duì)整形之后的脈寬信號(hào)進(jìn)行高速填充。如果計(jì)數(shù)值為N,標(biāo)準(zhǔn)計(jì)數(shù)脈沖的周期為ΔT,則輸入信號(hào)的頻率為f,周期為T:

DACOUT是一個(gè)用來(lái)設(shè)置ADuC7128內(nèi)部DDS輸出頻率的一個(gè)控制信號(hào),在本設(shè)計(jì)中,當(dāng)輸入信號(hào)的頻率超過(guò)30kHz時(shí),ADuC7128內(nèi)部DDS保持產(chǎn)生一個(gè)與輸入信號(hào)頻率相差30kHz的正弦波信號(hào),作為頻率轉(zhuǎn)換的參考信號(hào)。

經(jīng)過(guò)混頻、低通濾波、整形比較之后的兩路正弦波信號(hào),已經(jīng)變成頻率在30kHz以下的方波信號(hào)Q1和Q2。IRQ0、IRQ1是ADuC7128的兩個(gè)中斷引腳,分別將Q1的輸出端與ADuC7128的IRQ0引腳連接,Q2的輸出端與ADuC7128的IRQ1引腳連接。

IRQ0用于檢測(cè)Q1信號(hào)的下降沿,一旦Q1信號(hào)的下降沿到來(lái)時(shí),ADuC7128內(nèi)部計(jì)數(shù)器T1開(kāi)始工作,IRQ1用于檢測(cè)Q2信號(hào)的下降沿,一旦Q2信號(hào)的下降沿到來(lái)時(shí),ADuC7128內(nèi)部計(jì)數(shù)器T1停止工作。這樣,計(jì)數(shù)器T1上的累計(jì)值就是兩個(gè)方波間隔的脈沖數(shù)n,如果已知T1的計(jì)數(shù)間隔Δt',即可知兩個(gè)方波的時(shí)間間隔Δt:

![]()

從而通過(guò)公式(8)即可計(jì)算出兩輸入信號(hào)的相位差θ。

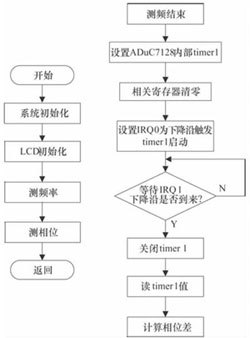

2.2 軟件設(shè)計(jì)

本系統(tǒng)的軟件設(shè)計(jì)主要是完成系統(tǒng)初始化、內(nèi)部數(shù)據(jù)處理、數(shù)據(jù)結(jié)果顯示等功能。圖4是系統(tǒng)的主程序和相位測(cè)量流程圖。

圖4 主程序和相位測(cè)量流程圖

3 測(cè)試結(jié)果與分析

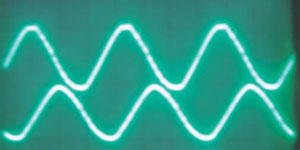

兩路同頻輸入信號(hào)是由一個(gè)相位差可調(diào)節(jié)的高精度信號(hào)源產(chǎn)生。當(dāng)輸入信號(hào)頻率小于30kHz時(shí),由ADuC7128內(nèi)部計(jì)數(shù)器直接計(jì)數(shù),經(jīng)過(guò)數(shù)據(jù)處理后得出相位差。輸入信號(hào)在進(jìn)行過(guò)零比較時(shí),由于兩路輸入信號(hào)之間的電平不相等所引起的幅相誤差,使得整形后產(chǎn)生的方波有所失真。圖5是兩路輸入信號(hào)為100kHz,相位差75°的正弦波信號(hào),經(jīng)過(guò)頻率變換及濾波整形后,兩個(gè)信號(hào)的相位保持不變,頻率變?yōu)?0kHz、幅度線性變化,如圖6所示。

圖5 兩路相位差75°的正弦波信號(hào)

圖6 兩路相位差75°的方波信號(hào)

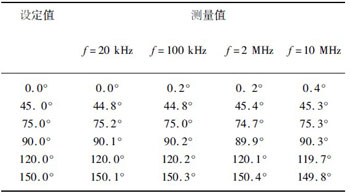

隨機(jī)抽取四個(gè)不同頻率的輸入信號(hào),分別在相位差為0~150°的范圍內(nèi)進(jìn)行測(cè)試,測(cè)試結(jié)果見(jiàn)表1。

表1 測(cè)試結(jié)果

測(cè)量結(jié)果表明該系統(tǒng)的最大測(cè)量不確定度為±0.4°,基本滿足了預(yù)期≤0.5°的設(shè)計(jì)要求。主要誤差源是ADuC7128內(nèi)部計(jì)數(shù)器只能進(jìn)行整數(shù)計(jì)數(shù),而引起的±1的計(jì)數(shù)誤差,該誤差可以采用多次測(cè)量求平均值的軟件方法進(jìn)行修正。同時(shí),兩路信號(hào)通道內(nèi)部硬件電路結(jié)構(gòu)存在差異,也是造成測(cè)量誤差的原因,解決此類誤差只能在設(shè)計(jì)對(duì)稱結(jié)構(gòu)的硬件電路時(shí),盡量選用相同的元器件。

4 結(jié)論

為了解決寬頻信號(hào)相位測(cè)量精度與微處理器主頻之間的矛盾,本文通過(guò)引入差頻變換原理,設(shè)計(jì)出一種基于ADuC7128微處理器的寬頻帶相位測(cè)量系統(tǒng)。該系統(tǒng)能夠完成輸入信號(hào)在0~10 MHz范圍內(nèi)的相位測(cè)量,測(cè)量分辨率可達(dá)0.1°,通過(guò)使用ADuC7128芯片內(nèi)部DDS模塊,節(jié)省了硬件成本,同時(shí)也降低了電路設(shè)計(jì)的復(fù)雜性,增加了系統(tǒng)的可靠性。試驗(yàn)表明,該系統(tǒng)設(shè)計(jì)方案可行、測(cè)量結(jié)果準(zhǔn)確。如果直接選擇主頻較高的微處理器或者通過(guò)時(shí)鐘倍頻的方法提高計(jì)數(shù)脈沖速度,在此設(shè)計(jì)方案基礎(chǔ)上,就能夠進(jìn)一步拓寬相位測(cè)量的頻帶。