1971年,,美國學者Joseph Tierney等三人提出了基于全數字技術,從相位概念出發(fā)直接合成所需波形的一種新的頻率合成原理,,稱之為直接數字頻率合成器(Drect Digital Synthesis,,DDS)。這是頻率合成技術的一次重大革命,,與第二代基于鎖相環(huán)頻率合成技術相比,,DDS具有頻率切換時間短、頻率分辨率高,、相位可連續(xù)變化和輸出波形靈活等優(yōu)點,。因此,廣泛應用于教學科研,、通信,、雷達、自動控制和電子測量等領域,。隨著DDS技術的不斷發(fā)展完善,,近幾年來,其應用范圍已經擴展到宇航,、遙控遙測,、儀器儀表等各項電子領域,。

雖然現在市場上有許多專用的DDS芯片,但控制方式卻是相對固定的,,因此不一定是所需要的?,F場可編程門陣列(Field Programmable Gate Array,FPGA)器件具有速度快,、集成度高和現場可編程的優(yōu)點,,因而在數字處理中得到廣泛應用,越來越得到硬件電路設計工程師的青睞,。因此,,利用FPGA的這些特性,則可根據需要方便的實現各種比較復雜的調頻,、調相和調幅功能,。

1 DDS結構原理

DDS是一種從相位概念出發(fā)直接合成所需波形的數字頻率合成技術,主要通過查找波形表實現,。由奈奎斯特抽樣定理可知,當抽樣頻率大于被抽樣頻率的2倍時,,通過抽樣得到的數字信號可通過一個低通濾波器還原成原來的信號,。

DDS的工作原理為:在參考時鐘的驅動下,相位累加器對頻率控制字進行線性累加,,得到的相位碼對波形存儲器尋址,,使之輸出相應的幅度碼,經過模/數轉換器得到相應的階梯波,,最后再使用低通濾波器對其進行平滑,,得到所需頻率的平滑連續(xù)的波形,其結構如圖1所示,。

相位累加器由N位加法器和N位累加寄存器級聯構成,。每經過一個時鐘脈沖fclk,加法器就將頻率控制字與累加寄存器輸出的累加相位數據相加,,把相加后的結果送至累加寄存器的數據輸入端,。相位累加器輸出的數據就是合成信號的相位,相位累加器的溢出頻率就是DDS的輸出信號頻率,。用相位累加器輸出數據作為波形存儲器(ROM)的相位取樣地址,,這樣就可以把存儲在波形存儲器內的波形抽樣值(二進制編碼)經查找表查出,完成相位到幅度的轉換,。

DDS模塊的輸出頻率是系統(tǒng)工作頻率,、相位累加器比特數N以及頻率控制字三者的一個函數,其數學關系由式(1)給出,。

它的頻率分辨率,,即頻率的變化間隔為K/2N。

2 系統(tǒng)功能單元實現

該系統(tǒng)設計是針對DDS的基本結構,以FPGA為核心,,加上外圍電路而實現的,。

2.1 相位累加器

相位累加器由8位加法器與8位寄存器級聯構成。累加器將加法器在上一個時鐘作用后所產生的相位數據反饋到加法器的輸入端:使加法器在下一個時鐘作用下繼續(xù)與頻率控制字data相加,,實現相位累加,,當相位累加器累加結果等于或大于256(當N=8時),則產生1次溢出,,完成1個周期波形輸出,。該相位累加器采用Verilog語言設計實現。

2.2 波形存儲器

以相位累加器輸出數據作為波形存儲器的取樣地址,,進行波形的相位—幅碼轉換,,即可在給定的時間上確定輸出的波形的抽樣幅碼。N位的尋址ROM相當于把0~2π的正弦信號離散成具有2N個樣值的序列,。若波形存儲器有D位數據位,,則各樣值的幅碼以D位二進制數值保存在該模擬ROM中,按照不同地址輸出相應相位的正弦信號的幅碼數值,。為了更加有效的表示波形,,當然期望波形存儲器輸出的二進制值位數越多越好。但是查找表的設計和D/A轉換器的選擇是相關的,,因此需要選擇位數高的D/A轉換器,。本文設計的正弦表,具有16b輸出,,采樣點為256,。

2.3 D/A轉換電路的實現

D/A轉換單元是繼波形數據產生單元之后,將數字量形式的波形幅值轉換成所要求的合成頻率的模擬量形式信號,。DAC輸出信號實際上是階梯模擬信號,,需在D/A轉換后利用低通濾波器對波形進行平滑處理。在此,,用Maxim公司生產的A/D換器MAX5885芯片,。該芯片需要將輸入時鐘信號轉換為差分輸入,且由外部芯片MAX6161提供1.2V的參考電壓,,D/A轉換后的差分輸出經變壓器轉換后即可得到所需的信號:

3 系統(tǒng)軟件設計

3.1 累加控制模塊的設計

相位累加器主要完成相位累加,,實現輸出波形頻率可調的功能。該模塊采用Verilog HDL語言來實現,,若要求DDS系統(tǒng)精度高,,相位累加器的位數N需較大。這里取N=8,,它的Verilog HDL關鍵代碼如下:

其中,,data信號為8位的頻率控制字,,通過改變data的值可以實現不同頻率波形的輸出。

3.2 波形存儲器的設計

針對不同的可編程器件,,ROM查找表的設計采用的方法也不相同,。主要是基于IP核Single Port BlockMemory和Verilog選擇語句這兩種方法。使用SinglePort Block Memory的波形存儲表只需要產生數據文件*.mif或*.coe,,然后直接在定制Single Port BlockMemory時,,添加數據文件即可。不過這種方法在FPGA支持內部嵌入式陣列塊(EAB)時才可以使用,;使用Verilog選擇語句比較直觀,,但當輸入數據量大的這種方法是比較繁瑣的。此次設計采用第一種方法,。

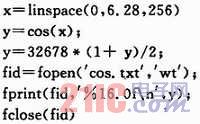

coe文件是在編譯和仿真過程中作為存儲器(ROM或RAM)初始化輸入的文件,,即memory initializationfile。創(chuàng)建coe文件的方式有很多種,,在這次設計中,,在Matlab中采用C語言來生成coe文件。coe文件編寫格式如下:

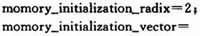

將生成的cos.txt文件的后綴該為.coe,,打開文件并將最后一行的逗號改為分號,,并在文件的最開始添加下面兩行:

最后保存文件退出,并加載到Single Port BlockMemory所生成的ROM中,。加載時要特別注意數據基數和數據長度的參數設置。

4 系統(tǒng)的功能仿真和驗證分析

累加控制器,、ROM查找表組成一個整體,,實現了一個基本的DDS系統(tǒng)。該設計以原子鐘(33MHz)為基準頻率輸入,,取累加器為32位,,實現輸出頻率為700kHz的信號。

通常相位累加器的位數N很大,,實際設計中受到體積和成本的限制,。為了節(jié)省ROM的容量采用相位截斷的方法,一般只取累加器輸出的高幾位作為ROM的尋址地址,。設計中取累加結果的高8位(N=8)來進行查表,,也就是說余弦ROM有256個尋址地址,數據寬度為16,。

5 結語

直接數字頻率合成(DDS)技術屬第三代頻率合成技術,,與第二代基于鎖相環(huán)頻率合成技術相比,利用DDS技術合成的輸出波形具有良好的性能指標本,。設計采用Xilinx公司Spartan-3系列的XC3S200芯片和高速16位D/A轉換器MAX5885,。在DDS的工作原理的基礎上,,介紹基于FPGA實現DDS的設計方法。 通過設置參數可以靈活控制輸出頻率和分辨率,。設計出具有精度高,,選擇參數控制輸出信號,產生一個理想的波形,。從測試結果可看出,,該系統(tǒng)工作穩(wěn)定、可靠,,并具有較好的參考與實用價值,。